Fターム[5F048BB04]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904)

Fターム[5F048BB04]の下位に属するFターム

多結晶Si (4,558)

シリサイド (1,994)

金属、合金、金属化合物(シリサイドを除く) (1,529)

異なるゲート電極材料を用いた複数MOS (668)

ゲート絶縁膜材料 (1,843)

Fターム[5F048BB04]に分類される特許

101 - 120 / 312

半導体基板、半導体基板の製造方法および電子デバイス

【課題】化合物半導体デバイスのスイッチング速度等の性能を向上できる半導体基板を提供する。

【解決手段】シリコン基板102と、シリコン基板の上に形成された絶縁膜104であってアスペクト比が√3/3以上のシリコン基板に達する開口部を有する絶縁膜104と、開口部に形成された化合物半導体結晶108であって絶縁膜104の表面より凸に形成されたシード化合物半導体結晶108と、シード化合物半導体結晶108の特定面をシード面として、絶縁膜の上にラテラル成長されたラテラル成長化合物半導体層112と、を備えた半導体基板。

(もっと読む)

半導体装置及びその製造方法

【課題】MIPS構造のデュアル・メタルゲートを有する半導体装置において高集積化を進展させつつ、PN境界部配線の断線や高抵抗化等の問題を防止できる半導体装置及びその製造方法を提供する。

【解決手段】NMISトランジスタのゲート電極122aは、第1の金属含有導電膜104aと、第1の金属含有導電膜104a上に形成された第3の金属含有導電膜113とから構成されており、PMISトランジスタのゲート電極122bは、第2の金属含有導電膜104bと、第2の金属含有導電膜104b上に形成された第3の金属含有導電膜113とから構成されている。第3の金属含有導電膜113は、第1の金属含有導電膜104a及び第2の金属含有導電膜104bのそれぞれと接するように、第1の金属含有導電膜104a上から素子分離領域102上を経て第2の金属含有導電膜104bの上まで連続的に形成されている。

(もっと読む)

二重CESLプロセス

【解決手段】 二重CESL(コンタクトエッチストップ層)プロセスは、(1)その上に第一装置領域、第二装置領域、及び第一と第二装置領域の間のSTI(シャロートレンチ分離)領域を有する基板を提供する段階と、(2)基板にかける第一応力を有し、第二装置領域を覆わない第一応力付与膜を形成する段階と、(3)基板の上にかける第二応力を有し、第一装置領域を覆わない第二応力付与膜を形成する段階とを含む。第一応力付与膜と第二応力付与膜とのオーバーラップ境界は、STI領域の直上の方向に製作され、オーバーラップ境界は、第二装置領域のチャネル領域に横方向に第一応力を引き起こすことを目的として、第二装置領域の近傍に設けられる。 (もっと読む)

半導体装置

【課題】低閾値動作に可及的に適した実効仕事関数を有するMISトランジスタを備えた半導体装置を提供することを可能にする。

【解決手段】Hf(或いはZr)酸化物に高価数金属を添加することでギャップ内準位を作りだし、窒素あるいはフッ素などによりギャップ内準位の位置を変化させることで、最適な実効仕事関数を有する電極を備え、低閾値動作が可能なCMISデバイスを実現した。

(もっと読む)

半導体装置及びその製造方法

【課題】改良された縦型のMOSトランジスタを備える半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10の主面に対してほぼ垂直に延在するチャネル領域22と、チャネル領域22の下部に設けられた第1の拡散層領域22aと、チャネル領域の上部に設けられた第2の拡散層領域22bと、半導体基板10の主面に対してほぼ垂直に延在し、ゲート絶縁膜30を介してチャネル領域22の側面に設けられた第1のゲート電極34と、半導体基板10の主面とほぼ平行に延在し、第1のゲート電極34の上部に接続された第2のゲート電極35aと、第1の拡散層領域22aに接続され、第2のゲート電極と交差する埋め込み配線21を備えている。第2のゲート電極35aの平面的な位置は、第1のゲート電極34の平面的な位置に対してオフセットされている。

(もっと読む)

半導体装置

【課題】電荷移動度を向上させる歪みをチャネル領域に発生させる結晶層をチャネル領域下に有し、かつリーク電流経路が形成されることを抑制できる半導体装置を提供する。

【解決手段】一態様に係る半導体装置は、半導体基板1と、前記半導体基板上に形成された第1の半導体結晶層14と、前記第1の半導体結晶層上にゲート絶縁膜11を介して形成されたゲート電極13と、前記第1の半導体結晶層内の前記ゲート絶縁膜下の領域に形成されたチャネル領域15と、前記第1の半導体結晶層内の前記チャネル領域を挟んだ領域に形成されたソース・ドレイン領域16と、前記半導体基板と前記チャネル領域との間に形成され、前記第1の半導体結晶層を構成する結晶よりも格子定数の大きい結晶からなり、前記半導体基板と前記第1の半導体層の間に、前記第2の半導体結晶層17を挟んで形成された埋込絶縁体層18と、を有する。

(もっと読む)

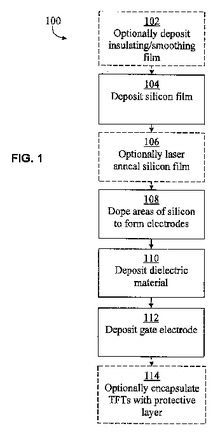

シリコン薄膜トランジスタ、並びにその製造システム及び方法

可撓性基板上に、自己整合シリコン薄膜トランジスタを製造するシステム及び方法。前記システム及び方法は、高いパフォーマンスのトランジスタを製造するために、精密さ、レゾリューション、レジストレーションが達成されるよう、レーザアニール、エッチング技術、レーザドーピングを全て低温度で行いつつ、化学気相堆積、プラズマエンハンスト気相堆積、プリント、コーティング、及び他の堆積処理といった堆積処理を組み込むとともに組み合わせている。そのようなTFTはディスプレイ、パッケージング、ラベリング等に使用できる。  (もっと読む)

(もっと読む)

サブリソグラフィック幅を有する応力誘起ライナによる異方性応力の生成。

【課題】 サブリソグラフィック幅を有する応力誘起ライナによる異方性応力の生成。

【解決手段】 直線端部を有する突出構造体を基板(8)上に形成する。突出構造体は電界効果トランジスタのゲートラインとすることができる。応力誘起ライナを基板(8)上に堆積させる。少なくとも2つの不混和性のポリマブロック成分を含む非感光性自己組織化ブロックコポリマ層を応力誘起ライナ(50)の上に堆積させ、アニールして不混和性成分を相分離させる。ポリマレジストを現像して少なくとも2つのポリマブロック成分のうちの少なくとも1つを除去し、突出構造体の直線端部(41)により入れ子になったラインのパターンを形成する。直線型のナノスケール・ストライプが、自己配列及び自己組織化のポリマレジスト内に形成される。応力誘起層は、サブリソグラフィック幅を有する直線型応力誘起ストライプにパターン化される。直線型応力誘起ストライプ(50)は主にそれらの縦方向に沿った一軸性応力をもたらし、下層の半導体デバイスに異方性応力を加える。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極をフルシリサイド化したMISFETを有する半導体装置及びその製造方法に関し、MISFETの特性劣化を引き起こすことなくゲート電極をフルシリサイド化しうる半導体装置の製造方法、並びに、そのような製造方法を用いて形成された優れた特性のMISFETを有する半導体装置を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜18と、ゲート絶縁膜18上に形成された金属シリサイド膜56bと、金属シリサイド膜56b上に形成された金属シリサイド膜56aとを有し、金属シリサイド膜56bにおける金属元素に対するシリコンの組成が、金属シリサイド膜56aにおける金属元素に対するシリコンの組成よりも大きいゲート電極26nと、ゲート電極26nの両側の半導体基板10内に形成された不純物拡散領域対54とを含むトランジスタを有する。

(もっと読む)

半導体装置、半導体装置の製造方法及び半導体装置の設計方法

【課題】複数のMOSFETにおけるトランジスタ特性変動を抑制すること。

【解決手段】半導体基板1に形成される第1のp型活性領域4と、半導体基板1に形成される第2のp型活性領域6と、半導体基板1に形成される第1のn型活性領域8と、半導体基板1に形成される第2のn型活性領域10と、第1のp型活性領域4の上方に形成されて第1の幅を有する第1導電パターン11gと、第2のp型活性領域6の上方に形成されて第1の幅より大きい第2の幅を有する第2導電パターン12gと、第1のn型活性領域8の上方に形成されて第3の幅を有する第3導電パターン13gと、第2のn型活性領域10の上方に形成されて第3の幅以下の第4の幅を有する第4導電パターン14gとを有する。

(もっと読む)

有機薄膜トランジスタおよびその製造方法

【課題】有機TFTにおいて、電子注入効率とホール注入効率を改善した電極と有機半導体の組み合わせをそれぞれ判別する手法を提供し、また、n型チャネルTFTとp型チャネルFETの2種類のTFTを実現し、さらに、相補型有機薄膜トランジスタ(有機CTFT)および、有機CTFTによる所望の任意回路構成を形成する有機CTFTアレイを提供する。

【解決手段】半導体−電極界面、および、半導体−ゲート絶縁体界面におけるフェルミエネルギーの差の大きさを与える数式を用いて、TFT材料を変えずに電極および絶縁膜の表面修飾だけを選択的に変化してn型とp型のTFTを実現する。任意回路を構成するために、p型チャネルTFT用のソース電極とゲート電極、および、n型チャネルTFT用のドレイン電極とゲート電極をすべてつないでおいて、表面修飾のプロセスを行い、その後、光照射などにより不要配線を切断する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート長に依存する仕事関数の変動を抑えることができる半導体装置の製造方法を提供する。

【解決手段】ゲート絶縁膜14上の多結晶シリコン膜を露出した後、半導体基板11を400℃まで加熱し、その温度が安定した後に、その温度を保持したまま、例えばスパッタリング法によりニッケル膜21を全面に形成する。ニッケル膜21の厚さは、シリコン酸化膜20上で60nmとする。この結果、シリコン酸化膜20上にはニッケル膜21が形成されるが、多結晶シリコン膜の表面に到達してきたニッケルは、そこに堆積するのではなく、多結晶シリコン膜と反応し、多結晶シリコン膜の全体がニッケルシリサイド膜22に変化する。従って、pMOS領域1には、p型不純物を含有するニッケルシリサイド膜22からなるゲート電極が形成され、nMOS領域2には、n型不純物を含有するニッケルシリサイド膜22からなるゲート電極が形成される。

(もっと読む)

半導体装置

【課題】 不純物チャネル層から下方向への不純物拡散を防止することにより、接合容量や接合リークを抑えたトランジスタを提供する。

【解決手段】 半導体基板1と、前記半導体基板上に形成された第一の不純物拡散抑制層3と、前記第一の不純物拡散抑制層3上に形成された不純物チャネル層5と、前記不純物チャネル層5上に形成された第二の不純物拡散抑制層4とを備えることにより不純物チャネル層5から下方向への不純物拡散を防止した急峻な不純物濃度勾配を有するチャネル構造を形成することができ、具体的にはシリコン基板1の不純物濃度を1×1017cm−3以下にすることによってより効果的に接合容量や接合リークを抑えたトランジスタを形成することができる。

(もっと読む)

半導体装置

【課題】複数列のゲート電極を備える半導体装置におけるトランジスタ特性のばらつきを低減する。

【解決手段】半導体基板70の上部にゲート長方向に並んで複数列に設けられたゲート電極10と、複数列のゲート電極10と同層に設けられてこれらを互いに電気的に接続するゲート接続部30と、を備え、ゲート接続部30が、複数列のゲート電極10のうち最も端に位置するゲート電極10bよりもゲート長方向の外側に突出する突出部32を有することを特徴とする半導体装置100。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極、ソース電極またはドレイン電極にタングステン膜を用いた半導体装置において、nMOSとpMOS間での抵抗差を低減可能な半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極14a,14bとソース/ドレイン拡散層16a,16bとを有するnMOS及びpMOSを形成し、ゲート電極14a,14b及びソース/ドレイン拡散層16a,16b上に、タングステン膜17を選択的に形成し、タングステン膜17を覆うように、絶縁膜(エッチングストップシリコン酸化膜18、シリコン窒化膜19)を形成し、pMOS領域12bの絶縁膜を除去し、pMOS領域12bのタングステン膜17上に、タングステン膜20を選択的に形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】工程数を削減しながらも、所望の不純物プロファイルおよびデバイス特性が得られる半導体装置の製造方法を提供する。

【解決手段】半導体基板1に溝6を形成する工程と、溝6の内部にゲート絶縁膜7を形成した後、溝6にゲート電極12を形成する工程と、半導体基板1およびゲート電極12を覆うように絶縁膜15を形成するとともに、ゲート電極12の幅方向両側に位置する絶縁膜15にセルコンタクト孔16を形成する工程と、セルコンタクト孔16を介して第1の不純物を半導体基板1に注入し、ゲート電極12の両側に前記第1の不純物を拡散させることによりソース・ドレイン拡散層13を形成する工程と、セルコンタクト孔16を介して第2の不純物を半導体基板1に注入し、溝6の底部6aおよび底部近傍の側面6bに前記第2の不純物を拡散させてチャネルドープ層9を形成する工程とを順に具備してなる。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド膜を有するMISトランジスタを備えた半導体装置において、接合リークを悪化させることなくゲート電極(Pch領域、Nch領域及びPN接合部)上のシリサイド層の断線を抑制する。

【解決手段】半導体装置は、半導体基板101と、半導体基板101上に形成されたゲート絶縁膜103と、ゲート絶縁膜103上に形成され、上部に金属シリサイド層108a及び108bを有するゲート電極104と、半導体基板101のうちのゲート電極104の両側に形成され、ソース領域及びドレイン領域となる活性領域106a及び106bとを備え、ゲート電極104は、P型不純物が導入されたP型部分104aを有し、P型不純物よりも重い所定の不純物元素が、P型部分104aを含むゲート電極104に選択的に導入されている。

(もっと読む)

MOSFETデバイスおよびその製造方法

【課題】フェルミレベルのピンニングの効果が、ポリシリコン(Poly−Si)/金属酸化物の界面で高い閾値電圧を招かないMOSFET(金属酸化物半導体電界効果トランジスタ)を含む半導体デバイスの製造方法を提供する。

【解決手段】半導体デバイスは、第1MOSFETトランジスタを含む。トランジスタは、基板、基板上の第1high−k誘電体層1、第1high−k誘電体層1上の第1誘電体キャップ層2、および第1誘電体キャップ層2上の、第1ドーピングレベルで第1導電型の半導体材料3からなる第1ゲート電極とを含む。第1誘電体キャップ層2は、スカンジウムを含む。

(もっと読む)

半導体装置の製造方法

【課題】素子分離領域に影響を及ぼすことなく、所望のMISトランジスタのチャネル領域に対して選択的に応力を生じさせ且つ記憶させることができる半導体装置を製造できるようにする。

【解決手段】半導体基板11の上に、応力歪み生成膜24を形成し、さらに、第3のレジストパターン25を形成する。第3のレジストパターン25をマスクにして、応力歪み生成膜24に対してプラズマ処理を行うことにより、応力歪み生成膜24における第1の活性領域11aの上側部分を改質して引っ張り応力を生じる引っ張り応力含有部24Aを形成する。次に、第3のレジストパターン25を除去した後、半導体基板11に対して熱処理を行うことにより、引っ張り応力含有部24Aによって、第1の活性領域11aにおけるn型ゲート電極15aの下に位置するチャネル領域に対してゲート長方向に沿った引っ張り応力を生じさせる。

(もっと読む)

半導体装置の製造方法

【課題】素子分離領域で分離される部分の半導体基板を低抵抗化することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、ウェルコンタクト接続領域を有するウェル、および前記ウェル上にトランジスタを形成するための素子領域を有する半導体基板の、前記ウェル上の前記素子領域と前記ウェルコンタクト接続領域との間の領域に溝を形成する工程と、前記溝の少なくとも底面にシリサイド層を形成する工程と、前記シリサイド層を形成した後、前記溝内に絶縁膜を埋め込み、素子分離領域を形成する工程と、を含む。

(もっと読む)

101 - 120 / 312

[ Back to top ]