Fターム[5F048BB04]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904)

Fターム[5F048BB04]の下位に属するFターム

多結晶Si (4,558)

シリサイド (1,994)

金属、合金、金属化合物(シリサイドを除く) (1,529)

異なるゲート電極材料を用いた複数MOS (668)

ゲート絶縁膜材料 (1,843)

Fターム[5F048BB04]に分類される特許

41 - 60 / 312

半導体装置及び半導体装置の製造方法

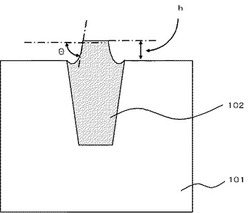

【課題】エッチング量を少なくしても素子分離膜の周辺にHigh−kゲート絶縁膜材料やゲート電極材料が残ることを抑制できるようにする。

【解決手段】素子分離膜102はSTI構造を有しており、基板101に埋め込まれており、かつトランジスタが形成される素子形成領域を分離している。素子分離膜102の側面の上端は、トランジスタのチャネル形成層よりも上に位置しており、かつチャネル形成層の表面から素子分離膜102の側面の最上部までの高さhが35nm以下である。また素子分離膜102のうちチャネル形成層よりも上に位置している部分の側面は、基板の表面に対する角度θが80度以下である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】半導体と金属の反応速度を制御してメモリセル領域と周辺回路領域とのシリサイド反応の差による不具合を解消する不揮発性半導体記憶装置とその製造方法を提供する。

【解決手段】シリコン基板1の上面にゲート絶縁膜4、第1の導電膜5を形成し、これらをエッチングして素子分離絶縁膜2を埋め込み形成する。電極間絶縁膜6、ゲルマニウム膜7aを形成する。周辺回路領域のゲート電極PGの電極間絶縁膜6に開口6aを形成し、この上に多結晶シリコン膜9aを形成する。ゲート電極MG、PGおよび容量性素子Capの分離加工後に層間絶縁膜10を埋め込む。多結晶シリコン膜9aの上部を露出させ、金属膜を形成してシリサイド化をする。この時、メモリセル領域ではシリサイドが速く進行するが、ゲルマニウム膜7aに達するとジャーマナイド反応は遅くなり、その間に周辺回路領域のシリサイド反応を促進させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の不純物分布のバラツキを抑え、STIエッジ部分への電界集中をより効果的に制御でき、実効チャネル幅が狭くなることを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】P型のシリコン基板10の一主面11に、トレンチ22と絶縁物24とを有する素子分離領域25と、素子分離領域25に囲まれた素子領域12であって、シリコン基板10の側面上部17が、トレンチ25に露出した素子領域12を形成し、ゲート絶縁膜40をシリコン基板10の上面14から側面上部17に延在して形成し、N+型ポリシリコン32とN+型ポリシリコン32の両側のP+型ポリシリコン34と、P+型ポリシリコン34の下側の側面上部17に沿って設けられたN+型ポリシリコン36とを有するゲート電極30を形成する。

(もっと読む)

薄膜回路構造及びその製造方法並びに有機EL装置

【課題】回路構造のスペースを小さくして画素の微細化を達成できる、薄膜回路構造及びその製造方法を提供する。

【解決手段】基材1上の面内方向Xに、ゲート電極2、ゲート絶縁膜3、酸化物半導体膜4、ソース電極5s及びドレイン電極5dで少なくとも構成された隣り合う2以上の薄膜トランジスタ10A,10Bを有する薄膜回路装置12であって、前記2以上の薄膜トランジスタ10A,10Bは、共通するゲート絶縁膜3を有するとともに、ゲート絶縁膜3の下に第1の酸化物半導体膜4Aが設けられた第1の薄膜トランジスタ10Aと、ゲート絶縁膜3の上に第2の酸化物半導体膜Aが設けられた第2の薄膜トランジスタ10Bとを有するようにして、上記課題を解決した。

(もっと読む)

電界効果トランジスタの金属ゲート構造

【課題】電界効果トランジスタの電気抵抗の小さい金属ゲート構造を提供する。

【解決手段】本発明は、集積回路製造に関するものであって、特に、低抵抗の金属ゲート電極を有する電界効果トランジスタに関するものである。電界効果トランジスタのゲート電極の例は、凹部326aを有し、かつ、第一抵抗を有する第一金属材料からなる下側部分326と、突起328aを有し、かつ、第二抵抗を有する第二金属材料からなる上側部分328とからなり、突起が凹部に延伸し、第二抵抗は第一抵抗より小さい材料で形成される。

(もっと読む)

平板表示装置及びその製造方法

【課題】薄膜トランジスタ及びMOS(Metal−Oxide−Semiconductor)構造のキャパシタを備える平板表示装置及びその製造方法を提供する。

【解決手段】第1領域の基板上に半導体で形成された活性層と、第2領域の基板上に半導体で形成された下部電極と、活性層及び下部電極を含む上部に形成された第1絶縁層と、活性層上の第1絶縁層上に第1導電層及び第2導電層で形成されたゲート電極と、下部電極上の第1絶縁層上に第1導電層で形成された上部電極と、ゲート電極及び上部電極を含む上部に形成され、活性層及び上部電極が露出するようにパターニングされた第2絶縁層と、露出した活性層に接続されるソース電極及びドレイン電極とを備える。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を有するMISFETを備えた半導体装置の信頼性向上を図る。

【解決手段】nチャネル型MISFET用の高誘電率ゲート絶縁膜としてHfとLaとOとを主成分として含有するHf含有絶縁膜4aを形成し、pチャネル型MISFET用の高誘電率ゲート絶縁膜としてHfとAlとOとを主成分として含有するHf含有絶縁膜4bを形成する。それから、金属膜7とシリコン膜8を形成し、これらをドライエッチングでパターニングしてゲート電極GE1,GE2を形成する。その後、ゲート電極GE1,GE2で覆われない部分のHf含有絶縁膜4a,4bをウェットエッチングで除去するが、この際、フッ酸を含有しない酸性溶液でのウェット処理とアルカリ性溶液でのウェット処理とを行ってから、フッ酸を含有する酸性溶液でのウェット処理を行う。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に対する不純物の突き抜けを抑止する。

【課題を解決するための手段】半導体装置の製造方法は、基板上方に成膜した多結晶シリコンをエッチングして基板の第1領域上方に第1ゲート電極を形成し、基板の第2領域上方に第2ゲート電極を形成し、第1領域及び第1ゲート電極を覆う第1パターンを形成し、第2ゲート電極及び第1パターンをマスクにして第2領域に第1不純物を第1ドーズ量で注入して第2領域に第1エクステンション領域を形成し、第1ゲート電極、第1領域及び第2ゲート電極の上面を露出させた第2パターンを形成し、第1エクステンション領域を覆い、第1ゲート電極、第2ゲート電極及び第2パターンをマスクにして第1領域に第2不純物を第1ドーズ量よりも多いドーズ量で注入して第1領域に第2エクステンション領域を形成するとともに、第1ゲート電極及び第2ゲート電極の少なくとも上部をアモルファス化する。

(もっと読む)

半導体装置

【課題】 半導体装置に関し、ソース・ドレイン領域を実効的に埋込Si混晶層で構成する際の電気的特性を向上する

【解決手段】 一導電型シリコン基体と、一導電型シリコン基体上に設けたゲート絶縁膜と、ゲート絶縁膜の上に設けたゲート電極とゲート電極の両側の一導電型シリコン基体に設けた逆導電型エクステンション領域と、逆導電型エクステンション領域に接するとともに、一導電型シリコン基体に形成された凹部に埋め込まれた逆導電型Si混晶層とを備えた半導体装置であって、逆導電型Si混晶層が、第1不純物濃度Si混晶層/第2不純物濃度Si混晶層/第3不純物濃度Si混晶層を有し、第2不純物濃度を第1不純物濃度及び第3不純物濃度よりも高くする。

(もっと読む)

半導体装置およびその作製方法

【課題】高性能な半導体装置を提供する。

【解決手段】絶縁表面上に設けられるゲート電極層と、ゲート電極層上に設けられるゲート絶縁層と、ゲート絶縁層上に設けられる第1の酸化物半導体層と、第1の酸化物半導体層上に接して設けられる第2の酸化物半導体層と、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域と重なり、且つ第2の酸化物半導体層に接して設けられる酸化物絶縁層と、酸化物絶縁層上、第1の酸化物半導体層の第2の領域上、及び第2の酸化物半導体層の第2の領域と重なり、且つ第2の酸化物半導体層に接して設けられるソース電極層及びドレイン電極層と、を有し、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域は、ゲート電極層と重なる領域、並びに第1の酸化物半導体層及び第2の酸化物半導体層の周縁及び側面、に設けられる領域である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】

微細化したMOSトランジスタを含む半導体装置において、リーク/ショートの可能性を抑制する。

【解決手段】

半導体装置の製造方法は、活性領域上に、ゲート絶縁膜とシリコン膜とを形成し、シリコン膜上方にゲート電極用レジストパターンを形成し、レジストパターンをマスクとして、シリコン膜を厚さの途中までエッチングしてレジストパターン下方に凸部を残し、レジストパターンを除去した後シリコン膜を覆うダミー膜を形成し、ダミー膜を異方性エッチングして、凸部の側壁にダミー膜を残存させつつ、平坦面上のダミー膜を除去し、ダミー膜をマスクとして、シリコン膜の残りの厚さをエッチングしてゲート電極を形成し、ゲート電極両側の半導体基板に、ソース/ドレイン領域を形成し、シリコン領域にシリサイドを形成する。

(もっと読む)

ゲート・スタック・ストレッサを有する多重方位のナノワイヤ

【課題】トランジスタ・チャネルのより効果的な電気伝導を提供する。

【解決手段】電子デバイスは、結晶構造を規定し、ある長さおよび厚さtCを有する導電チャネルと、チャネルの表面と接している厚さtGの誘電体膜とを包含する。さらに、この膜は、結晶構造に対するチャネル長さの配列方向に依存し圧縮力もしくは引張力によって、電荷担体(電子または正孔)のチャネル長さ沿いの電気的移動度が増大するように、圧縮力または引張力のいずれかをチャネルの被接触面に作用させる材料を含む。異なるトランジスタにおいて正孔および電子両方の移動度が増大したチップと、かかるトランジスタまたはチップを作製する方法とに対する実施形態が提示される。

(もっと読む)

半導体装置、半導体装置の製造方法、電子機器および電子機器の製造方法

【課題】回路特性の向上が可能な、有機トランジスタよりなる論理回路を有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、ドライバトランジスタ(PTD)とロードトランジスタ(PTL)を有する論理回路を含む半導体装置であって、ドライバトランジスタの能動層は、第1のp型有機半導体層(5D)からなり、ロードトランジスタの能動層は、第2のp型有機半導体層(5L)からなり、ロードトランジスタの閾値電圧(VthL)はドライバトランジスタの閾値電圧(VthD)よりも高い。p型有機半導体(5D,5L)の膜厚を変えることにより、閾値を変化させる。p型有機半導体(5D,5L)の材料を変えることにより、閾値を変化させる。第1のp型有機半導体層(5D)にドナーを含ませる。第2のp型有機半導体層(5L)にアクセプターを含ませる。かかる構成により、論理回路の特性を向上させることができる。

(もっと読む)

半導体装置及び電子機器

【課題】回路面積が小さい、またはトランジスタの劣化を防止するよう形成された、有機トランジスタと無機トランジスタとを備えた半導体装置を提供する。

【解決手段】本発明の一形態の半導体装置としてのCMOS回路は、(a)基板100と、(b)有機半導体層106aを含むp型有機トランジスタPTと、(c)p型有機トランジスタPTの上層に設けられた無機半導体層126aを含むn型無機トランジスタNTと、を備える。さらに、n型無機トランジスタNTのチャネル領域126は、p型有機トランジスタPTのチャネル領域106と、平面視において少なくとも部分的に重なっている。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置が有する集積回路の多機能化を図ること、又は、炭化シリコン基板を用いて集積回路を形成する場合であっても集積回路の大面積化を図ることを目的とする。

【解決手段】基板上に第1の絶縁層を介して設けられた島状の炭化シリコン層と、炭化シリコン層上に設けられた第1のゲート絶縁層と、第1のゲート絶縁層上に設けられ且つ炭化シリコン層と重畳する第1の導電層とを有する第1のトランジスタと、基板上に第2の絶縁層を介して設けられた島状の単結晶シリコン層と、単結晶シリコン層上に設けられた第2のゲート絶縁層と、第2のゲート絶縁層上に設けられ且つ単結晶シリコン層と重畳する第2の導電層とを有する第2のトランジスタを設ける。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

半導体構造体およびその形成方法(内部応力を有する半導体ナノワイヤ)

【課題】高性能の相補型金属半導体(CMOS)回路の為の高いオン電流をもたらす半導体ナノワイヤ・デバイスを提供する。

【解決手段】両方の端部に半導体パッド33A、37Aを有する半導体ナノワイヤ32が、基板上にサスペンドされる。半導体ナノワイヤが応力発生ライナ部によって長手方向の応力を受けている間、半導体ナノワイヤの中間部の上にゲート誘電体36及びゲート電極38が形成される。ゲート誘電体及びゲート電極の形成によって半導体ナノワイヤの歪み状態が固定されるため、半導体ナノワイヤの中間部は、応力発生ライナの除去後に長手方向の固有の内部応力を受ける。半導体パッド内にソース及びドレイン領域33B,37Bが形成され、半導体ナノワイヤ・トランジスタが得られる。ソース及びドレイン・パッドの上に、中間工程(MOL)誘電体層を直接形成することができる。

(もっと読む)

41 - 60 / 312

[ Back to top ]