Fターム[5F048BB04]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904)

Fターム[5F048BB04]の下位に属するFターム

多結晶Si (4,558)

シリサイド (1,994)

金属、合金、金属化合物(シリサイドを除く) (1,529)

異なるゲート電極材料を用いた複数MOS (668)

ゲート絶縁膜材料 (1,843)

Fターム[5F048BB04]に分類される特許

141 - 160 / 312

半導体装置および半導体装置の製造方法

【課題】レイアウトに依存することなく深さが制御されかつ結晶欠陥の発生が抑えられたエピタキシャル成長層が設けられ、これにより特性の向上が図られた半導体装置を提供する。

【解決手段】半導体基板3上に設けられたゲート電極9と、ゲート電極9両脇に不純物を導入して設けられたソース/ドレイン領域15とを備えた半導体装置1aにおいて、ソース/ドレイン領域15は、ゲート電極9脇における半導体基板3を掘り下げた位置に当該半導体基板3とは格子定数が異なる半導体材料をエピタキシャル成長させてなるエピタキシャル成長層11と、半導体基板3の表面層に設けた基板拡散層13とで構成されている。

(もっと読む)

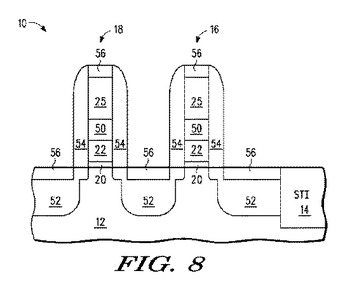

ゲート・ストレッサ及び半導体デバイスを特徴とする半導体デバイスの製造方法

半導体デバイス(10)は半導体層(12)に形成される。ゲート・スタック(16,18)は、半導体層の上にわたって形成され、第1の伝導層(22)及び、第1の層の上の第2層(24)を有する。第1の層は、より伝導性であり、第2の層よりインプラントに対して停止力を提供する。種(46)が、第2の層内にインプラントされる。ソース/ドレイン領域(52)は、ゲート・スタックの対抗する側の半導体層に形成される。ゲート・スタックの下の領域の半導体層にゲート・スタックが応力を働かせるインプラントのステップの後、ゲート・スタックは加熱される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 半導体領域にn型不純物領域およびp型不純物領域を形成する際に、該半導体領域に形成されるn型およびp型不純物を含む不純物領域を小さくできる、半導体装置の製造方法を提供すること。

【解決手段】 nMOS形成領域の多結晶シリコン膜にn型不純物を導入し、加熱処理によりn型不純物領域を形成し、pMOS形成領域の多結晶シリコン膜にp型不純物を導入し、加熱処理によりp型不純物領域を形成することを含む半導体装置の製造方法であって、pMOS形成領域の多結晶シリコン膜をマスクで覆って、nMOS形成領域の多結晶シリコン膜の表面にn型不純物を導入する工程と、酸素を用いた処理により前記マスクを除去するとともに、nMOS形成領域の多結晶シリコン膜の表面に酸化膜10を形成する工程と、酸化膜10をマスクに用いてpMOS形成領域の多結晶シリコン膜1の表面にp型不純物12を導入する工程とを含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化プロセスにおいても、また、Nchトランジスタ及びPchトランジスタの両方を持つデバイスにおいても、欠陥等を発生させることなく、トランジスタのチャネル領域に対する応力制御を行うことを可能にする。

【解決手段】Nchトランジスタの第1のゲート電極107及びPchトランジスタの第2のゲート電極108のそれぞれの構成材料として、互いに応力の大きさが異なる材料を用いている。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ及び画像表示装置

【課題】簡便なプロセスで素子分離が可能な薄膜トランジスタの製造方法、薄膜トランジスタおよび画像表示装置を提供すること。

【解決手段】絶縁基板上にゲート電極、ゲート絶縁膜、一対の主電極領域を形成する工程と、一対の主電極領域上を含む絶縁基板上の全面に有機半導体層を形成する工程と、有機半導体層と一対の主電極領域との間のチャネル領域を覆う封止層を形成する工程と、有機半導体層の前記封止層の形成されていない領域を非活性化させる工程と、を備えたことを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

半導体素子及びその製造方法

【課題】本発明はフィントランジスタを含む半導体素子及びその製造方法に関する。

【解決手段】半導体素子は、素子分離構造を備えた半導体基板に画成されたフィン型活性領域と、フィン型活性領域の上部に形成されたリセスと、フィン型活性領域の上部に形成され、前記リセスを埋め込むシリコンゲルマニウム層を含むゲート電極とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】適切な仕事関数を有する金属ゲート電極を備え、空乏化が抑制され、高速に動作可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1001内に形成されたp型活性領域1003およびn型活性領域1004と、p型活性領域1003の上面に形成された第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成され、金属元素を含む第1の電極形成膜1007を有する第1のゲート電極とを有する第1のMISFETと、n型活性領域1004の上面に形成された第2のゲート絶縁膜と、第2のゲート絶縁膜上に形成された第2の電極形成膜1010を有する第2のゲート電極とを有する第2のMISFETとを備えている。第2の電極形成膜1010は、第1の電極形成膜1007と同じ金属元素を含み、第1の電極形成膜1007よりも酸素の含有比が高い。

(もっと読む)

半導体装置及びその製造方法

【課題】金属半導体化合物からなるゲート電極を採用して十分な低抵抗化を図るも、煩瑣な構成・製造工程を付加することなく、容易且つ確実にゲート電極の閾値電圧の十分に広範囲な制御を可能とし、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体領域に例えばシリコン基板を用い、ゲート電極材料に多結晶シリコンを用いる場合、多結晶シリコン膜を炭素、窒素及び酸素のうちから選ばれた少なくとも1種である添加元素を含有するように形成して半導体層とした後、この半導体層上にNi,Co,Pd,Pt等の高融点金属膜を積層して熱処理してシリサイド化し、ゲート電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】従来のCMISデバイスにおいては、価電子帯端近くの高い仕事関数を有する金属は、還元雰囲気アニール後に実効仕事関数が低下する。

【解決手段】半導体装置は、ソースとドレイン間のN型半導体層上に形成された金属元素を含むゲート絶縁膜と、ゲート絶縁膜上に形成され、膜厚が3nm以下であるカーボン層と、カーボン層上に形成されたゲート電極とを有し、ゲート電極/ゲート絶縁膜界面へのカーボン層による仕事関数の上昇効果により、還元雰囲気アニール耐性のない価電子帯端近くの高い仕事関数を有する金属を用いずとも、PMISFETに必要な実効仕事関数を得ることができ、低い閾値電圧を実現する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化が進みゲート長のバリエーションが増大した場合にも、高駆動力MISFETを搭載した高性能デバイスを安定して実現できる簡便なFUSI化技術を提供する。

【解決手段】第1のゲート長(相対的に短いゲート長)を持つ第1のゲート電極105Aがフルシリサイド化されているのに対して、第2のゲート長(相対的に長いゲート長)を持つ第2のゲート電極105Bはフルシリサイド化されていない。

(もっと読む)

接点装置およびスイッチ装置

【課題】アーク生成物や接点金属粉の飛散等が無く、性能を長期に維持することができる接点装置を提供すること。

【解決手段】本接点装置2は、共に同じ導電型の半導体領域からなる一対の接点領域10,10と、両接点領域10,10間に介在する半導体領域から構成された制御領域12と、上記制御領域12に向けてプラスマイナスの電界を選択的に発生可能に配置された電界発生体6と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】溝ゲート構造を有するトランジスタとプレーナゲート構造を有するトランジスタを同一基板上に有する半導体装置であって、ゲート電極構造をポリメタルゲート構造とし、溝ゲートとプレーナゲートとを異なる導電型としたデュアルゲート構造としても、溝ゲートのポリシリコンに十分なドーパントを導入して空乏化を防止し、一方、プレーナゲートも同じ層厚のポリシリコンでも不純物イオンのゲート絶縁膜突抜けが起こらない新たな製造方法を提供する。

【解決手段】溝ゲート用のシリコン層にイオン注入し、その後一旦ポリシリコン化し、再度イオン注入によりポリシリコン層の表面をアモルファス化(層9,10)して、プレーナゲート用の異なる導電型のイオン注入を行う。

(もっと読む)

半導体装置の製造方法

【課題】対向するゲート電極パターンの間隙をリソグラフィーの限界を超えて狭く形成した上で、両ゲート電極の全体をシリサイド化して閾値を調整可能とする。

【解決手段】分離形成すべきゲート電極を連結した一体のパターンとして形成し、ゲート電極を被覆する第1絶縁膜を形成後、第1絶縁膜を平坦化しながら膜厚を減じてゲート電極表面を露出させる。その後、ゲート電極パターンの分離すべき箇所をエッチングにより除去してゲート電極パターンを2つの部分20,21に分断する。その上で、開口部全体を第2絶縁膜22で埋め、両ゲート電極20,21及び第2絶縁膜22上に金属膜23を形成する。その後、熱処理によって、金属膜23とシリコンとを反応させて両ゲート電極20,21を金属シリサイド化する。その後、7層〜9層のCu配線を両トランジスタ上方に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】金属とシリコンおよび/またはゲルマニウムを必須として含む金属半導体化合物をゲート電極とする金属絶縁膜半導体電界効果トランジスタを利用した半導体装置において、ゲート絶縁膜やチャネル等によらずに複数の閾値電圧を設定する。

【解決手段】半導体装置が、MAxで表される組成を有する第1のゲート電極を含む第1のトランジスタと、MAyで表される組成を有する第2のゲート電極を含む第2のトランジスタを少なくとも含むMIS電界効果トランジスタを含む(式中、MはW、Mo、Ni、Pt、Ta、Pd、Co、およびTiからなる群より選択される少なくとも1種の金属元素であり、Aはシリコンおよび/またはゲルマニウムであり、0<x≦3、および0<y≦3であり、xとyは異なる)。

(もっと読む)

2つの仕事関数を備えたCMOSデバイスの製造方法

【課題】本発明は、2つの仕事関数の半導体デバイスの製造方法を提供する。

【解決手段】製造方法は、基板の第1領域及び第2領域上にデバイスを設けることを備える。これは、基板の第1領域及び第2領域上に誘電性層を設けること、及び第1及び第2領域の両方の誘電性層の上部にゲート電極を設けることによってなされる。第1領域上のゲート電極及び第2領域上のゲート電極の両方は仕事関数を有する。上記方法は、さらに、誘電性層とゲート電極との間で第1領域上にキャッピング層を設けることで第1領域上のゲート電極の仕事関数を変更し、及び第2領域における誘電性層とゲート電極との間の界面でスピーシーズを導入するようにスピーシーズを埋め込むことにより第2領域上のゲート電極の仕事関数を変更することを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】安定した特性が得られる半導体装置及びその製造方法を提供する。

【解決手段】シリコン酸化膜と、前記シリコン酸化膜の上に設けられ、前記シリコン酸化膜よりも誘電率が高い金属シリケート絶縁膜と、前記金属シリケート絶縁膜の上に設けられたゲート電極と、を備え、前記金属シリケート絶縁膜における、前記ゲート電極と接する側の金属元素の組成比率が、前記シリコン酸化膜と接する側の金属元素の組成比率よりも低い。

(もっと読む)

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板とは格子定数の異なる半導体層からチャネル部に対して効果的に応力を印加することが可能でこれによりキャリア移動度の向上を図り高機能化の達成が可能な半導体装置を提供する。

【解決手段】半導体基板3上にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇において半導体基板3の表面を掘り下げた部分にエピタキシャル成長によって形成された半導体層(応力印加層)9とを備えた半導体装置1において、半導体層9は、半導体基板3とは格子定数の異なる層であり、ゲート絶縁膜5およびゲート電極7は、半導体層9間において半導体基板3の表面を掘り下げた部分を埋め込む状態で設けられている。半導体基板3の表面に対するゲート絶縁膜5の深さ位置d2は、半導体層9の深さ位置d1よりも浅いこととする。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネリングの発生と製造工程の増加とを防ぐことができる半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極106及び第1,第2のソース/ドレイン領域119A,119Bの上部が非晶質化シリコン層110となっている。これにより、上記第1,第2のソース/ドレイン領域119A,119Bを形成するための不純物の注入を行っても、非晶質化シリコン層110がその不純物の障壁となるので、チャネリングの発生を防ぐことができる。また、上記非晶質化シリコン層110は除去しなくてもよいので、製造工程の増加も生じない。

(もっと読む)

銅ニッケル及びガリウム−スズ−亜鉛−銅−チタンのp型及びn型酸化物に基づく電子半導体デバイス、周辺機器及びその製造工程

本発明は、銅ニッケル(OCuxNiy,但し0<x<3且つ0<y<3)、又は、GSZTCOとして示される複数成分のガリウム−スズ−亜鉛−銅−チタン酸化物に基づくp型及びn型酸化物半導体の使用に関する。前記半導体は、異なるモル組成であり、非結晶構造又は結晶構造を備え、ドナー又は電子受容半導体の電気的性質(価数)を備える。本発明は、室温又は100℃以下の温度の製造工程を含む。光電子分野、電子分野での適用は、補完−金属−酸化物−半導体(C−MOS)、薄膜トランジスタ、p−nヘテロ接合、ロジックゲート、Oリング発振器等のデバイスを、ガラス、金属箔、ポリマー、セルロース材料等の基板を用いて製造することである。ここでは、フッ化マグネシウムに基づく保護層が使用され、二酸化ケイ素等の誘電体に対するアクティブな半導体のタンタル酸化物の整合層を備えている。 (もっと読む)

141 - 160 / 312

[ Back to top ]