Fターム[5F048BB04]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904)

Fターム[5F048BB04]の下位に属するFターム

多結晶Si (4,558)

シリサイド (1,994)

金属、合金、金属化合物(シリサイドを除く) (1,529)

異なるゲート電極材料を用いた複数MOS (668)

ゲート絶縁膜材料 (1,843)

Fターム[5F048BB04]に分類される特許

61 - 80 / 312

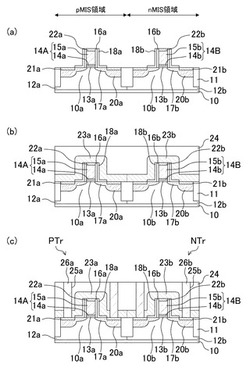

半導体装置及びその製造方法

【課題】(110)面を主面とする半導体基板に形成されたp型MISトランジスタを備えた半導体装置において、p型MISトランジスタのさらなる性能向上を図る。

【解決手段】半導体装置は、(110)面を主面とする半導体基板10に形成されたp型MISトランジスタPTrを備えた半導体装置である。p型MISトランジスタPTrは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され第1の金属膜14a及び第1の金属膜14a上に形成された第1のシリコン膜15aからなる第1のゲート電極14Aとを備えている。第1の金属膜14aは、膜厚が1nm以上であって且つ10nm以下である。

(もっと読む)

多重Vt電界効果トランジスタ素子

【課題】 多重閾値電圧(Vt)電界効果トランジスタ(FET)素子、及びその製造のための技術を提供する。

【解決手段】 1つの態様において、ソース領域と、ドレイン領域と、ソース領域とドレイン領域とを相互接続する少なくとも1つのチャネルと、チャネルの少なくとも一部を囲み、ゲート全体に対し選択的に配置された少なくとも1つのバンド・エッジ金属により多重閾値電圧を有するように構成されたゲートとを含むFET素子が提供される。

(もっと読む)

半導体構造体およびその形成方法(内部応力を有する半導体ナノワイヤ)

【課題】高性能の相補型金属半導体(CMOS)回路の為の高いオン電流をもたらす半導体ナノワイヤ・デバイスを提供する。

【解決手段】両方の端部に半導体パッド33A、37Aを有する半導体ナノワイヤ32が、基板上にサスペンドされる。半導体ナノワイヤが応力発生ライナ部によって長手方向の応力を受けている間、半導体ナノワイヤの中間部の上にゲート誘電体36及びゲート電極38が形成される。ゲート誘電体及びゲート電極の形成によって半導体ナノワイヤの歪み状態が固定されるため、半導体ナノワイヤの中間部は、応力発生ライナの除去後に長手方向の固有の内部応力を受ける。半導体パッド内にソース及びドレイン領域33B,37Bが形成され、半導体ナノワイヤ・トランジスタが得られる。ソース及びドレイン・パッドの上に、中間工程(MOL)誘電体層を直接形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】直接トンネル電流が流れる程度に薄膜化されたゲート絶縁膜におけるゲート電極からのドーパント原子の基板への拡散を防止すると共に、ゲートリーク電流を低減できるようにする。

【解決手段】第1の素子形成領域51及び第2の素子形成領域52に区画された半導体基板11上に、酸化膜からなる第1のゲート絶縁膜13Aを形成する。次に、第1のゲート絶縁膜13Aの第2の素子形成領域52に含まれる部分を除去し、半導体基板11に対して酸窒化性雰囲気で熱処理を行なうことにより、第2の素子形成領域52上に膜厚が第1のゲート絶縁膜13Aよりも小さい酸窒化膜からなる第2のゲート絶縁膜15Bを形成する。次に、第1のゲート絶縁膜13B及び第2のゲート絶縁膜15Bを窒素プラズマに暴露することにより、窒素原子をさらに導入された第1のゲート絶縁膜13C及び第2のゲート絶縁膜15Cを形成する。

(もっと読む)

半導体装置の製造方法

【課題】nMOSFETのソース/ドレイン領域にはSiGeを埋め込まず、pMOSFETのソース/ドレイン領域にのみSiGeを再現性よく埋め込むことが可能な製造方法を提供する。

【解決手段】第1活性領域12と交差する第1ゲート電極21、及び第2活性領域13と交差する第2ゲート電極22を形成し、第1及び第2ゲート電極を覆うように、第1キャップ膜35を形成する。第1活性領域上の第1キャップ膜35を、エッチングして除去する。半導体基板全面に、第2キャップ膜を形成37する。第2活性領域上の第2キャップ膜37を第2マスクパターンで覆い、第1活性領域上の第2キャップ膜37をエッチングして除去する。第2活性領域を第1及び第2キャップ膜で覆った状態で、第1活性領域において、ソース/ドレイン領域をエッチングすることにより、凹部を形成する。凹部内を、埋込部材で埋め込む。

(もっと読む)

縦型論理素子

【課題】狭い面積で高速応答性の縦型半導体装置を提供する。

【解決手段】基板上に形成された第1の電極と、絶縁膜と、絶縁膜を介し第1の電極の側面の一方に形成された第1の導電型の第1の半導体層と、絶縁膜を介し第1の電極の側面の他方に形成された第2の導電型の第2の半導体層と、一部領域における第1の半導体層上に形成された第2の電極と、他の一部領域における第2の半導体層上に形成された第3の電極と、第1の電極の上層の第1の半導体層及び第2の半導体層上に形成された第4の電極とを有し、第2の電極と前記第4の電極間における第1の半導体層に第1のチャネル領域が形成され、第3の電極と前記第4の電極間における第2の半導体層に第2のチャネル領域が形成されるものであることを特徴とする縦型半導体装置を提供することにより上記課題を解決する。

(もっと読む)

高次無線周波数高調波抑制領域を含む半導体オン・インシュレータ基板及び構造体

【課題】 抑制された高次無線周波数高調波を有する無線周波数デバイス及び無線周波数回路の製造を可能にする、半導体オン・インシュレータ基板及び関連した半導体構造体、並びに、半導体オン・インシュレータ基板及び関連した半導体構造体を製造する方法を提供する。

【解決手段】 半導体オン・インシュレータ基板及び関連した半導体構造体、並びに、半導体オン・インシュレータ基板及び関連した半導体構造体を製造するための方法が、半導体オン・インシュレータ基板内のベース半導体基板と埋込み誘電体層との界面の下方の位置において、ベース半導体基板内に配置及び形成された高次無線周波数高調波抑制領域をもたらす。高次無線周波数高調波抑制領域は、これに限定するものではないが、希ガス原子などのイオン注入原子を含むことができ、これに限定するものではないが、半導体構造体内の表面半導体層内及びその上に配置及び形成された無線周波数相補型金属酸化膜半導体デバイス(又は代替的には受動デバイス)などの無線周波数デバイスに電力供給するとき、抑制された高次無線周波数高調波をもたらす。

(もっと読む)

半導体装置およびその製造方法

【課題】NMISFETにおいて、最も高移動度化可能である(111)面をチャネル面に持ち、同時に、<110>方向を電流方向に持つ半導体装置およびその製造方法を提供すること。

【解決手段】チャネル電流が流れる方向に対して垂直方向の断面が三角形状をしており、その2面が(111)面で、残りの1面が(100)面であるGOI層6またはGe層8と、前記(100)面上に形成されたSi層7と、を備えたNMISFET領域3を備えたこと、を特徴とする半導体装置1。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】デュアルゲート電極構造のMOSトランジスタにおいて、閾値電圧シフト及びばらつきを抑えることができる半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板上にP型MOSトランジスタ及びN型MOSトランジスタを備える半導体装置において、P型MOSトランジスタ及びN型MOSトランジスタは、それぞれチャネル極性と同極のポリゲート電極を備えたデュアルゲート構造のMOSトランジスタであって、デュアルゲート型MOSトランジスタのポリゲート電極が、ゲルマニウムからなる第1のポリゲート電極層と、ゲルマニウムとシリコンとが混在した第2のポリゲート電極層と、シリコンからなる第3のポリゲート電極層と、を順次備えた積層構造を有している。

(もっと読む)

半導体装置及びその作製方法

【課題】大型の半導体装置で、高速に動作する半導体装置を提供することを目的する。

【解決手段】単結晶の半導体層を有するトップゲート型のトランジスタと、アモルファス

シリコン(またはマイクロクリスタルシリコン)の半導体層を有するボトムゲート型のト

ランジスタとを同一基板に形成する。そして、各々のトランジスタが有するゲート電極を

同じレイヤーで形成し、ソース及びドレイン電極も同じレイヤーで形成する。このように

して、製造工程を削減する。つまり、ボトムゲート型のトランジスタの製造工程に、少し

だけ工程を追加するだけで、2つのタイプのトランジスタを製造することが出来る。

(もっと読む)

垂直置換ゲートトランジスタと集積可能な容量の構造及び作製法

【課題】垂直MOSFETデバイス及び容量に関連したプロセス及び構成を提供する。

【解決手段】半導体デバイスは半導体材料の第1の層と、第1の層中に形成された第1のソース/ドレイン領域を有する電界効果トランジスタを含む。チャネル領域は、第1の層上に形成され、第2のソース/ドレイン領域235はチャネル領域上に形成される。集積回路構造は底部プレート266、誘電体層258及び最上部容量プレート259を有する容量を更に含む。作製方法において、電界効果トランジスタのソース領域及びドレイン領域から成るグループから選択された第1のデバイス領域が、半導体層上に形成される。第1の電界効果トランジスタゲート領域265が、第1のデバイス領域上に形成される。間にはさまれた誘電体層を有する最上部及び底部層も、半導体層上に形成される。別の実施例において、容量層は半導体層中に形成された溝又は窓内に形成される。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板であっても加熱処理が可能となる、基板の熱処理方法を提供する。

【解決手段】熱処理される被熱処理部を備えるベース基板を熱処理して半導体基板を製造する方法であって、電磁波を吸収して熱を発生し、被熱処理部を選択的に加熱する被加熱部をベース基板上に設ける段階と、ベース基板に電磁波を照射する段階と、被加熱部が電磁波を吸収することにより発生する熱によって、被熱処理部の格子欠陥密度を低減する段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜形成工程のような大きな熱負荷を避けて、チャネルの最上面の不純物濃度を薄くした、深さ方向のドーピング・プロファイルを実現し、オン電流が向上する半導体装置の製造方法を提供することである。

【解決手段】 ゲート電極形成後にゲート電極をマスクにして角度10度以下でチャネル不純物をイオン注入し、この後、チャネル不純物の活性化を、基板表面から所定の深さのチャネル不純物濃度がゲート長方向に一定になるように、RTAを用いたアニールで行う、さらに、その後のエクステンション/ハロー注入、深いS/D注入の後の活性化を、拡散レスアニールで行う。

(もっと読む)

半導体装置

【課題】トランジスタの集積化を妨げることなく、トランジスタの駆動力を向上させる半導体装置を提供する。

【解決手段】所定の結晶からなる半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、ゲート幅方向に凸部を有して前記半導体基板内に形成され、前記所定の結晶とは異なる格子定数を有するエピタキシャル結晶が埋め込まれたソース・ドレイン領域と、を具備するトランジスタと、前記凸部以外の前記ソース・ドレイン領域に接続されたコンタクトプラグと、を備えた半導体装置を提供する。

(もっと読む)

半導体装置の製造方法

【課題】素子分離領域に埋め込まれる絶縁膜に効率良く応力を残留させる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板に形成した溝内に絶縁膜を埋め込む工程と、埋め込まれた前記絶縁膜上を覆うように被覆膜を形成する工程と、前記被覆膜を形成した後、熱処理により、前記半導体基板の前記絶縁膜周辺の領域に歪みを発生させる応力を前記絶縁膜に残留させ、素子分離領域を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

生物要素検出用チップの製造方法

【課題】生物要素検出用トランジスタを備えたマイクロエレクトロニクス装置を製造するための新規の方法を提供する。

【解決手段】生物要素を検出するための少なくとも1つの回路を備えたマイクロエレクトロニクス装置の改良された製造方法であって、a)トランジスタを形成する段階と、−前記トランジスタを被覆する少なくとも1つの絶縁材料(141)で少なくとも1つの層を堆積する段階と、−第1型トランジスタのそれぞれのゲート(135)の上面が露出されるように前記絶縁材料(141)の層に1つ以上の穴(143)を形成する段階と、−ゲート材料で穴を充填する段階と、b)第1型トランジスタのそれぞれのゲート(135)の少なくとも一部を除去する一方で、第2型トランジスタのゲートを保護する段階と、を含み、段階b)で実施される除去より前または同時に、ゲート材料を除去する段階をさらに含む方法。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応でき、High−kゲート絶縁膜を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、p型層103上に設けられた第1のゲート絶縁膜115、TiNからなる第1のゲート電極116と、及び不純物を含む半導体からなる第1の上部ゲート電極117を有するNチャネル型MOSトランジスタ106と、n型層102上に設けられた第2のゲート絶縁膜109、TiN結晶からなり、(111)配向/(200)配向が1.5以上となるTiN層を少なくとも一部に含む第2のゲート電極110、及び不純物を含む半導体からなる第2の上部ゲート電極111を有するPチャネル型MOSトランジスタ105とを備えている。

(もっと読む)

デュアル仕事関数半導体デバイスの製造方法および製造されたデバイス

【課題】デュアル仕事関数半導体デバイスの製造方法を提供する。

【解決手段】半導体基板100上に、これと接触するゲート誘電体層104を形成する工程と、ゲート誘電体層の上に、これと接触する金属層105を形成する工程と、金属層の上に、これと接触するゲート充填材料の層106を形成する工程と、ゲート誘電体層、金属層、およびゲート充填層をパターニングして、第1ゲートスタックと第2ゲートスタックとを形成する工程と、半導体基板中に、ソースおよびドレイン領域109を形成する工程と、第1および第2ゲートスタックの少なくとも片側の第1および第2領域中に誘電体層を形成する工程と、その後に第2ゲートスタックのみからゲート充填材料を除去し、下層の金属層を露出させる工程と、露出した金属層を金属酸化物層1051に変える工程と、第2ゲートスタックを他のゲート充填材料115を用いて再形成する工程とを含む。

(もっと読む)

61 - 80 / 312

[ Back to top ]