Fターム[5F048BB09]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | 金属、合金、金属化合物(シリサイドを除く) (1,529)

Fターム[5F048BB09]に分類される特許

141 - 160 / 1,529

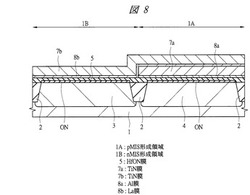

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】本発明は、pチャネル型MISFETをpMIS形成領域1Aに有し、nチャネル型MISFETをnMIS形成領域1Bに有する半導体装置の製造方法であって、HfON膜5上にAl膜8aを形成する工程と、Al膜上にTiリッチなTiN膜7aを形成する工程と、を有する。さらに、nMIS形成領域1BのTiN膜およびAl膜を除去する工程と、nMIS形成領域1BのHfON膜5上およびpMIS形成領域1AのTiN膜7a上にLa膜8bを形成する工程と、La膜8b上にNリッチなTiN膜7bを形成する工程と、熱処理を施す工程とを有する。かかる工程によれば、pMIS形成領域1Aにおいては、HfAlON膜のN含有量を少なくでき、nMIS形成領域1Bにおいては、HfLaON膜のN含有量を多くできる。よって、eWFを改善できる。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MOSトランジスタ及びp型MOSトランジスタのそれぞれに共通のゲート電極材料を用い、且つそれぞれの閾値電圧が適切な値に調整された半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1トランジスタ11及び第2トランジスタ12を備えている。第1トランジスタ11は、第1ゲート絶縁膜131と、第1ゲート電極133とを有し、第2トランジスタ12は、第2ゲート絶縁膜132と、第2ゲート電極134とを有している。第1ゲート絶縁膜131及び第2ゲート絶縁膜132は、第1絶縁層151及び第2絶縁層152を含む。第1ゲート電極133及び第2ゲート電極134は、断面凹形の第1導電層155及び該第1導電層155の上に形成された第2導電層156を含む。第1絶縁層151及び第2絶縁層152は平板状であり、第1ゲート絶縁膜131は、仕事関数調整用の第1元素を含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース及びドレインのいずれか一方に高抵抗成分が付加されたときドレイン電流の低下を抑制する。

【解決手段】一つの実施形態によれば、半導体装置は基板、第一のソース及びドレイン、第二のソース及びドレイン、ゲート電極膜が設けられる。第一のソース及びドレインと第二のソース及びドレインは、基板表面に設けられる。第二のソース及びドレインの一方は、第一のソース及びドレインの一方に隣接配置される。第二のソース及びドレインの他方は、第一のソース及びドレインの他方に隣接配置される。ゲート電極膜は、第一及び第二のソース及びドレインの一方と第一及び第二のソース及びドレインの他方の間の基板表面上に設けられ、ゲート絶縁膜を介して設けられる。第一のソース及びドレインとゲート電極膜は第一のFETを構成し、第二のソース及びドレインとゲート電極膜は第二のFETを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生バイポーラトランジスタのゲインを低下することにより、誤動作や動作特性の変動が少ない半導体装置及びその製造方法を得る。

【解決手段】シリコン層3の上面上には、シリコン酸化膜6が部分的に形成されている。シリコン酸化膜6上には、ポリシリコンから成るゲート電極7が部分的に形成されている。ゲート電極7の下方に存在する部分のシリコン酸化膜6は、ゲート絶縁膜として機能する。ゲート電極7の側面には、シリコン酸化膜8を挟んで、シリコン窒化膜9が形成されている。シリコン酸化膜8及びシリコン窒化膜9は、シリコン酸化膜6上に形成されている。ゲート長方向に関するシリコン酸化膜8の幅W1は、シリコン酸化膜6の膜厚T1よりも大きい。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】用途によって異なるしきい値電圧を有するトランジスタを有する半導体装置、及び工程数の増加を抑えた当該半導体装置を製造する方法を提供する。

【解決手段】半導体装置100は、半導体基板101上に形成された第1のゲート絶縁膜110aと、第1のゲート絶縁膜110a上に形成された第1のゲート電極109aと、第1のゲート絶縁膜110aの側面上及び第1のゲート電極109aの側面上に形成された第1のサイドウォール絶縁膜140aとを有する第1導電型の第1のMISFET150を備えている。第1のサイドウォール絶縁膜140aの少なくとも一部には、第1のゲート絶縁膜110aに正または負の固定電荷を誘起するための元素が含まれている。

(もっと読む)

半導体装置の製造方法

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】 トランジスタの接合耐圧と表面耐圧の劣化を抑制し、信頼性の高い不揮発性半導体記憶装置を提供する。

【解決手段】 トランジスタTr.2は、ソース高濃度領域9を有するソース拡散層、メモリセルのゲート絶縁膜より厚いゲート絶縁膜16を有するゲート電極、ドレイン高濃度領域9とドレイン高濃度領域を囲むドレイン低濃度領域23を有するドレイン拡散層22を備え、ドレイン拡散層22は、ゲート絶縁膜16の底面より低い第1の窪みを有し、ドレイン低濃度領域23は、第1の窪みより低い第2の窪み“c”を有し、ドレイン高濃度領域9に接合されるコンタクト10を介してビット線に接続され、ソース高濃度領域に接合されるコンタクトを介してセンスアンプに接続される。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

電界効果トランジスタを備える半導体素子及びその製造方法

【課題】電界効果トランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成され、第1活性領域の上面及び向き合う側面を経て伸張する第1ゲート電極を有する第1導電型の第1FET素子と、前記第1FET素子上に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、第2活性領域の上面及び向き合う側面を経て伸張する第2ゲート電極を有する第2導電型の第2FET素子と、を備える。

(もっと読む)

半導体装置及び電子機器

【課題】薄膜の応力を用いて、トランジスタのしきい値電圧を変化させる。

【解決手段】第1のチャネル形成領域を有する第1の半導体層と、第2のチャネル形成領域を有する第2の半導体層に対して、それらの上に形成された薄膜の応力を用いて、トランジスタのしきい値電圧を異ならせることができる。これらを電気的に接続することで、E/D MOS回路を提供できる。

(もっと読む)

半導体装置及び電子機器

【課題】薄膜の応力を用いてしきい値電圧を制御する。

【解決手段】第1の半導体層に設けられた第1のゲート電極と、第2の半導体層に設けられた第2のゲート電極と、第1の半導体層と第2の半導体層に接して設けられた第1の絶縁層と、第1の絶縁層が設けられた第1の半導体層の一方の面の反対側に設けられた第2の絶縁層と、第1の絶縁層が設けられた第2の半導体層の一方の面の反対側に設けられた第2の絶縁層及び第3の絶縁層と、を有し、第1の半導体層には第2の絶縁層により応力が加わり、第2の半導体層には第2の絶縁層と第3の絶縁層により応力が加わることで、第1の半導体層及び第2の半導体層に加わる応力が異なる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化金属膜から放出される窒素がゲート絶縁膜に到達することを抑制する。

【解決手段】この半導体装置は、半導体基板100、第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び第1ゲート電極を備えている。第1ゲート絶縁膜110は半導体基板100上に形成されており、酸化シリコン又は酸窒化シリコンよりも比誘電率が高い材料から構成されている。シリコン含有第2ゲート絶縁膜122は、第1ゲート絶縁膜110上に形成されている。第1ゲート電極はシリコン含有第2ゲート絶縁膜122上に形成されており、窒化金属層124を有している。第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び窒化金属層124は、pMOSFETの一部を構成している。

(もっと読む)

半導体装置及びその製造方法

【課題】DRAMの微細化及び高集積化により、プロセス低温化が進み、400〜500℃熱処理による基板内の酸素ドナー化による電子発生量が多くなってきた。そのため、基板深くに形成されるウェル同士の分離耐圧が厳しくなり、デバイス劣化を引き起こしてしまう。

【解決手段】P型半導体基板11の表面から0.2〜1μmの範囲の深さに2E+17atom/cm3以上のピーク濃度を有するNウェル層12の下方に、P型半導体基板11中に発生するキャリア電子濃度より高濃度のP型不純物を含有する空乏層拡大防止層17を有する半導体装置。

(もっと読む)

EL表示装置

【課題】動作性能および信頼性の高いEL表示装置を提供する。

【解決手段】第1のチャネル形成領域と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率の絶縁膜を有するnチャネル型トランジスタやpチャネル型トランジスタを有する半導体装置の製造方法において、nチャネル型トランジスタのゲート絶縁膜の側面への異物の付着を抑制する。

【解決手段】半導体基板の主表面上の、p型不純物領域PWLに機能用nチャネル型トランジスタが、n型不純物領域NWLに機能用pチャネル型トランジスタが形成される。p型不純物領域PWLの、平面視における機能用nチャネル型トランジスタ以外の領域に形成される複数の第1の周辺用トランジスタは、周辺用n型ゲート構造体と周辺用p型ゲート構造体とが混在するように形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

埋め込みドープ層を有する完全空乏型SOIデバイス

【課題】完全空乏型SOIデバイスの製造に適したセミコンダクタオンインシュレータ(SeOI)ウェーハおよびそれを用いたデバイスを提供すること。

【解決手段】本発明は、第1の基板の表面領域にドープ層、ドープ層上に埋め込み酸化物層、埋め込み酸化物層上に半導体層を形成してSeOIウェーハを得る。SeOIウェーハの第2の領域の埋め込み酸化物層および半導体層を維持しながらSeOIウェーハの第1の領域から埋め込み酸化物層および半導体層を除去し、第2の領域に上部トランジスタを形成する。第1の領域にリセスチャネルアレイトランジスタを形成し、第2の領域にpチャネルトランジスタおよび/またはnチャネルトランジスタを形成する。ドープ層内またはこの近傍にバックゲートを形成し、第1の領域にリセスチャネルアレイトランジスタを形成し、ドープ層内またはその近傍にソース領域およびドレイン領域を形成する。

(もっと読む)

ダイオードを含む半導体装置

【課題】ダイオードを含む半導体装置において、ダイオードの逆回復挙動とオン状態特性とのトレードオフを改善する。

【解決手段】半導体装置200は陰極216と陽極218を含む。陽極は第1のp型半導体陽極領域204と第2のp型半導体陽極領域206を含む。第1のp型半導体陽極領域204は陽極接触領域218に電気的に接続される。第2のp型半導体陽極領域206は、第2のp型陽極領域と陽極接触領域218間を電気的に接続または切断するように構成された、MOSFET228等のスイッチを介し陽極接触領域218に電気的に接続される。

(もっと読む)

141 - 160 / 1,529

[ Back to top ]