Fターム[5F048BB12]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 多層(2層)ゲート (2,461)

Fターム[5F048BB12]の下位に属するFターム

3層以上 (480)

Fターム[5F048BB12]に分類される特許

361 - 380 / 1,981

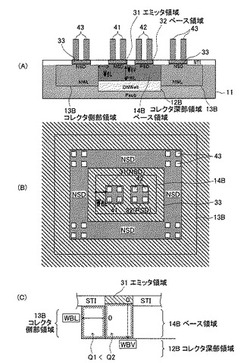

半導体デバイスおよびその製造方法

【課題】CMOS回路側の仕様で不純物領域の深さや濃度が制約を受けるような場合でもhFEの向上を可能とする。

【解決手段】1つのバイポーラトランジスタが、横型の主トランジスタ部と、縦型の補助トランジスタ部とから形成されている。横型の主トランジスタ部は、エミッタ領域31と、ベース領域14Bの表面側部分とコレクタ側部領域13Bとを電流チャネルとして動作する。縦型の補助トランジスタ部は、エミッタ領域31と、その底面に接するベース領域14Bの深部側部と、コレクタ深部領域12Bとを電流チャネルとして動作する。

(もっと読む)

電界効果トランジスタの金属ゲート構造

【課題】電界効果トランジスタの電気抵抗の小さい金属ゲート構造を提供する。

【解決手段】本発明は、集積回路製造に関するものであって、特に、低抵抗の金属ゲート電極を有する電界効果トランジスタに関するものである。電界効果トランジスタのゲート電極の例は、凹部326aを有し、かつ、第一抵抗を有する第一金属材料からなる下側部分326と、突起328aを有し、かつ、第二抵抗を有する第二金属材料からなる上側部分328とからなり、突起が凹部に延伸し、第二抵抗は第一抵抗より小さい材料で形成される。

(もっと読む)

半導体装置とその製造方法

【課題】製造工程増加を抑制しつつ、閾値電圧の異なる複数のトランジスタ(FET)を同一基板上に有する半導体装置を実現する。

【解決手段】半導体装置は同一導電型の第1及び第2FETを有する。第1FETは、基板1上の第1ゲート電極13L、その側方の第1サイドウォール15L、第1ゲート電極13L両側の第1活性領域1Lの第1エクステンション領域17Lを備える。第2FETは、基板1上の第2ゲート電極13H、その側方の第2サイドウォール15H、第2ゲート電極13H両側の第2活性領域1Hの第2エクステンション領域17Hを備える。ゲート長方向に関し、第1エクステンション領域17Lと第1ゲート電極13Lとの重なりは、第2エクステンション領域17Hと第2ゲート電極13Hとの重なりよりも長い。第1ゲート電極13Lと第1サイドウォール15Lとの距離は、第2ゲート電極13Hと第2サイドウォール15Hとの距離より短い。

(もっと読む)

半導体装置およびその製造方法

【課題】短チャネル効果の発生を抑制できる半導体装置及びその製造方法の提供。

【解決手段】本発明の半導体装置は、半導体基板1の活性領域上にゲート絶縁膜5aを介して形成されたゲート電極105と、ゲート電極105側面を覆う第1絶縁膜サイドウォール5bと、ゲート電極105を挟んで形成されたソース領域108S及びドレイン領域108Dにおいて、側面が第1絶縁膜サイドウォール5bに接して半導体基板1上面に形成されたシリコン層109と、第1絶縁膜サイドウォール5bを介してゲート電極105側面と対向し、底面がシリコン層109上面に接して形成された第2絶縁膜サイドウォール5dと、シリコン層109内下層部に設けられたLDD不純物層109aと、シリコン層109内上層部に設けられた高濃度不純物層109bと、LDD不純物層109aの下方、半導体基板1の表面側に形成されたポケット不純物層108aとを具備する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】信頼性および集積性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板(シリコン基板1)と、シリコン基板1に設けられた第1のトレンチ3と、第1のトレンチ3に埋め込まれた受動素子層10と、第1のトレンチ3と受動素子層10との間に設けられた第1の絶縁膜(シリコン窒化膜4)と、を備え、上面視において、第1のトレンチ3形成の周縁部分と第1の絶縁膜(シリコン窒化膜4)の周縁部分とが略一致している。

(もっと読む)

自己整合されたデュアル応力層を用いるCMOS構造体及び方法

【課題】 デバイス性能を向上させ、チップの留まりを改善するために、CMOS構造体内に機械的応力を与える構造体及び方法を提供すること。

【解決手段】 第1のトランジスタの上に配置された第1の応力層及び第2のトランジスタの上に配置された第2の応力層が、当接するが、重ならない、CMOS構造体及びCMOS構造体を製造する方法が提供される。こうした重ならない当接により、第1のトランジスタ及び第2のトランジスタの一方の中のソース/ドレイン領域の上に、シリサイド層へのコンタクトを形成するとき、製造の柔軟性が向上する。

(もっと読む)

平板表示装置及びその製造方法

【課題】薄膜トランジスタ及びMOS(Metal−Oxide−Semiconductor)構造のキャパシタを備える平板表示装置及びその製造方法を提供する。

【解決手段】第1領域の基板上に半導体で形成された活性層と、第2領域の基板上に半導体で形成された下部電極と、活性層及び下部電極を含む上部に形成された第1絶縁層と、活性層上の第1絶縁層上に第1導電層及び第2導電層で形成されたゲート電極と、下部電極上の第1絶縁層上に第1導電層で形成された上部電極と、ゲート電極及び上部電極を含む上部に形成され、活性層及び上部電極が露出するようにパターニングされた第2絶縁層と、露出した活性層に接続されるソース電極及びドレイン電極とを備える。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層を含むトランジスタと、酸化物半導体以外の半導体材料を用いて構成された論理回路と、を有し、前記トランジスタのソース電極またはドレイン電極の一方と、前記論理回路の少なくとも一の入力とは電気的に接続され、前記トランジスタを介して、前記論理回路に少なくとも一の入力信号が供給される半導体装置である。ここで、トランジスタのオフ電流は1×10−13A以下であるのが望ましい。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの性能を良好にするとともに、トランジスタにより構成されたアンチヒューズのゲート絶縁膜の破壊後の特性を良好にする。

【解決手段】アンチヒューズ素子190として機能するNMOSトランジスタにおいて、N型チャネル領域112aが設けられている。また、通常のNMOSトランジスタ194には、N型エクステンション領域120およびP型ポケット領域122が設けられているが、アンチヒューズ素子190には、エクステンション領域およびポケット領域が設けられない。

(もっと読む)

半導体集積装置

【課題】半導体集積回路装置において、スナップバック動作が生じることのない表示パネル駆動用半導体集積装置の出力回路に適した静電気保護回路を提供する。

【解決手段】静電気保護回路において、半導体基板上に形成され、外部接続端子10に接続されたゲート電極をPMOSトランジスタ2と、半導体基板上に形成され、外部接続端10子に接続されたゲート電極を有するNMOSトランジスタ3とを備え、正極性のサージ電流を、PMOSトランジスタ2のソース領域およびドレイン領域と半導体基板との間のpn接合を介して順方向電流としてVDD電源端子11aに逃がし、負極性のサージ電流を、該NMOSトランジスタ3のソース領域およびドレイン領域と半導体基板との間のpn接合を介して順方向電流としてVSS電源端子11bに逃がすようにした。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】絶縁表面上に第1配線と、前記第1配線を覆う第1層間絶縁膜と、前記第1層間絶縁膜上の一部に接して第2層間絶縁膜と、前記第1層間絶縁膜及び前記第2層間絶縁膜上に第2配線とを有し、前記第1配線と前記第2配線とが重なっている領域には、前記第1層間絶縁膜と前記第2層間絶縁膜とが積層された半導体装置である。第1配線と第2配線間に層間絶縁膜が積層されていることで寄生容量の低減が可能となる。

(もっと読む)

半導体装置

【課題】待機電力の低減を実現する半導体装置の提供を、目的の一とする。

【解決手段】酸化物半導体を活性層として有するトランジスタをスイッチング素子として用い、該スイッチング素子で、集積回路を構成する回路への電源電圧の供給を制御する。具体的には、回路が動作状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を行い、回路が停止状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を停止する。また、電源電圧が供給される回路は、半導体を用いて形成されるトランジスタ、ダイオード、容量素子、抵抗素子、インダクタンスなどの、集積回路を構成する最小単位の半導体素子を、単数または複数有する。そして、上記半導体素子が有する半導体は、結晶性を有するシリコン(結晶性シリコン)、具体的には、微結晶シリコン、多結晶シリコン、単結晶シリコンを含む。

(もっと読む)

半導体装置の製造方法

【課題】メモリセル領域と高電圧トランジスタとの高濃度不純物拡散領域を同時にイオン注入で形成し、且つ高電圧トランジスタ側の方が浅くなるように形成する。

【解決手段】シリコン基板1にメモリセル領域にゲート電極MG、SGを形成し(図3(b))、周辺回路領域にゲート電極PG(図3(c))を形成する。周辺回路領域のゲート電極PGは、高電圧トランジスタについては厚い膜厚のゲート絶縁膜11が形成されている。ゲート絶縁膜11を残した状態でTEOS酸化膜9を成膜し、スペーサ加工をする。この時、スペーサ9aを形成すると共に、ゲート絶縁膜11を半分程度エッチングして11aとする。TEOS酸化膜10を形成後に高濃度不純物拡散領域1d、1eをイオン注入で深さd1、d2で形成する。高電圧トランジスタについてはゲート絶縁膜11aを介して行うので、浅く形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSプロセスへの導入が容易で、エミッタ−ベース間のリーク電流(電界強度)を低減し、ノイズやサージ電圧の影響を受けにくい高性能な半導体装置とその製造方法の提供。

【解決手段】導電膜をマスクとして、2回のイオン注入を行ってエミッタを形成する。第2エミッタ領域111bは、低濃度の不純物イオン注入によって形成し、第1エミッタ領域111aは、高濃度の不純物イオン注入によって形成する。その結果、エミッタの周縁部に低濃度の第2エミッタ領域が形成され、電界が緩和され、リーク電流が低減する。また、導電膜とエミッタ電極116とが接続され、ノイズの影響を受けにくくなる。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層とSi層との界面における抵抗が低いMOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成された、チャネル移動度に実質的な影響を与えないSiGe層15と、SiGe層15上に形成されたSi層16と、半導体基板2、SiGe層15、およびSi層16内のゲート電極12の両側に形成されたn型ソース・ドレイン領域19と、Si層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】絶縁層上の半導体層に形成された部分空乏型のトランジスターにおいて、高いON/OFF比と、安定動作を同時に実現できるようにした半導体装置を提供する。

【解決手段】絶縁層上の半導体層に形成された部分空乏型の第1トランジスターと、前記半導体層に形成された第2トランジスターと、前記半導体層に形成された第3トランジスターと、を備え、前記第1トランジスターは、第1導電型の第1ソース又は第1ドレインを有し、前記第2トランジスターは、第1導電型の第2ソース又は第2ドレインを有し、前記第3トランジスターは、第2導電型の第3ソース又は第3ドレインを有し、前記第1ソース又は第1ドレインの一方と、前記第2ソース又は第2ドレインの一方とが電気的に接続され、前記第2ソース又は第2ドレインの他方と、前記第1トランジスターのボディ領域と、前記第3ソース又は第3ドレインの一方とが互いに電気的に接続されている。

(もっと読む)

半導体装置

【課題】低酸素処理を施したシリコン基板は基板表面層が応力に対して非常にもろくなってしまい、ハンド津愛想うちの製造プロセスの過程でクラックや反りが発生する原因ともなってしまう。

【解決手段】チャネル形成領域に形成された不純物領域に応力を集中させるため、チャネル形成領域に対して人為的かつ局部的に不純物領域を設ける。チャネル形成領域に局部的に添加された不純物元素(炭素、窒素、酸素から選ばれた一種または複数種類の元素)の領域は、低酸素処理を施したシリコン基板の応力を緩和する緩衝領域として機能する。

(もっと読む)

半導体装置及びその製造方法

【課題】pチャネルトランジスタ及びnチャネルトランジスタの閾値電圧を共に低減できるCMISトランジスタを有する半導体装置を提供する。

【解決手段】pチャネルトランジスタは、半導体基板100における第1の領域上に形成された第1のゲート構造150Aと、第1のゲート構造150Aの側壁上に形成された第1のスペーサ構造とを有する。nチャネルトランジスタは、半導体基板100における第2の領域上に形成された第2のゲート構造150Bと、第2のゲート構造150Bの側壁上に形成された第2のスペーサ構造とを有する。第1のスペーサ構造における第1のゲート構造150Aの側壁との接触部分の含有酸素濃度は、第2のスペーサ構造における第2のゲート構造150Bの側壁との接触部分の含有酸素濃度よりも高い。

(もっと読む)

361 - 380 / 1,981

[ Back to top ]