Fターム[5F048BB18]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521) | 閾値電圧が異なる複数MOS (1,778) | 注入量、注入物質が異なるもの (323)

Fターム[5F048BB18]に分類される特許

201 - 220 / 323

半導体装置の製造方法

【課題】溝ゲート構造を有するトランジスタとプレーナゲート構造を有するトランジスタを同一基板上に有する半導体装置であって、ゲート電極構造をポリメタルゲート構造とし、溝ゲートとプレーナゲートとを異なる導電型としたデュアルゲート構造としても、溝ゲートのポリシリコンに十分なドーパントを導入して空乏化を防止し、一方、プレーナゲートも同じ層厚のポリシリコンでも不純物イオンのゲート絶縁膜突抜けが起こらない新たな製造方法を提供する。

【解決手段】溝ゲート用のシリコン層にイオン注入し、その後一旦ポリシリコン化し、再度イオン注入によりポリシリコン層の表面をアモルファス化(層9,10)して、プレーナゲート用の異なる導電型のイオン注入を行う。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】表面チャネル型の微細なPチャネルMISトランジスタを備え、装置全体としてのNBTI信頼性が高い半導体装置を製造し易い半導体装置の製造方法を得ること。

【解決手段】表面チャネル型の微細なPチャネルMISトランジスタ20Pを備えた半導体装置を得るにあたって、ゲート絶縁膜11にシリコン酸窒化物膜が含まれているPチャネルMISトランジスタの集積密度が相対的に高い第1機能領域MRと、PチャネルMISトランジスタの集積密度が相対的に低い第2機能領域LRとが片面に形成され、かつPチャネルMISトランジスタの各々を覆う層間絶縁膜用の電気絶縁膜40Aが形成された半導体基板10に、第1機能領域を対象に選択的にレーザアニールを施し、このレーザアニールにより第1機能領域に形成されているゲート絶縁膜の各々を改質する選択的アニーリングを行う。

(もっと読む)

2つの仕事関数を備えたCMOSデバイスの製造方法

【課題】本発明は、2つの仕事関数の半導体デバイスの製造方法を提供する。

【解決手段】製造方法は、基板の第1領域及び第2領域上にデバイスを設けることを備える。これは、基板の第1領域及び第2領域上に誘電性層を設けること、及び第1及び第2領域の両方の誘電性層の上部にゲート電極を設けることによってなされる。第1領域上のゲート電極及び第2領域上のゲート電極の両方は仕事関数を有する。上記方法は、さらに、誘電性層とゲート電極との間で第1領域上にキャッピング層を設けることで第1領域上のゲート電極の仕事関数を変更し、及び第2領域における誘電性層とゲート電極との間の界面でスピーシーズを導入するようにスピーシーズを埋め込むことにより第2領域上のゲート電極の仕事関数を変更することを備える。

(もっと読む)

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易なNi−FUSI/SiONあるいはHigh−kゲート絶縁膜構造および低いしきい値電圧Vthを有するCMISを備えた半導体装置およびその製造方法を提供することを可能にする。

【解決手段】基板1中に互いに絶縁分離されたp型半導体領域2とn型半導体領域3を形成する工程と、p型およびn型半導体領域上に第1および第2ゲート絶縁膜5,15をそれぞれ形成する工程と、第1ゲート絶縁膜上にNi/Si<31/12となる組成の第1ニッケルシリサイド6bを形成するとともに第2ゲート絶縁膜上にNi/Si≧31/12となる組成の第2ニッケルシリサイド16を形成する工程と、第1ニッケルシリサイド中にアルミニウムを拡散させ、第1ニッケルシリサイドと第1ゲート絶縁膜との界面にアルミニウム6aを偏析させる工程と、を備えている。

(もっと読む)

半導体装置

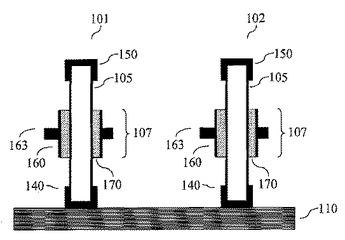

【課題】円柱型構造のトランジスタの特性を向上させる。

【解決手段】導電層の形成された基板において前記導電層上に形成された柱状半導体と、前記柱状半導体の周囲に形成された絶縁層と、前記絶縁層の周囲に形成された一つのトランジスタのゲート電極を有しており、ゲート電極は、仕事関数の異なる少なくとも2層以上の導電膜の積層構造により構成されていることを特徴とする半導体装置を提供することにより、上記課題を解決する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】DRAMのメモリセルを微細化して高集積化するとともに高速動作可能な半導体集積回路技術を提供する。

【解決手段】半導体装置の製造方法は、まず、ゲート電極7の上面に窒化シリコン膜8を形成し、その側面に窒化シリコンからなる第1サイドウォールスペーサ14および酸化シリコンからなる第2サイドウォールスペーサ15を形成する。次に、DRAMのメモリセル領域の選択MISFETQsにおいては接続孔19,21が第1サイドウォールスペーサ14に対して自己整合で開口され、導電体20およびビット線BLの接続部が形成される。また、DRAMのメモリセル領域以外のNチャネルMISFETQn1,Qn2およびPチャネルMISFETQp1においては、高濃度N形半導体領域16,16bおよび高濃度P形半導体領域17が第2サイドウォールスペーサ15に対して自己整合に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】アーリー電圧の低下を抑制する。

【解決手段】第1導電型の半導体基板に設けられた、第1,第2の素子領域と、第2導電型の第1の不純物からなり第1の素子領域の深さ方向の奥深部位に設けられたレトログレードウェルと、第2導電型の第2の不純物からなり第1の素子領域の深さ方向の中間部位に設けられたエンハンスドドープ層と、第2導電型の第3の不純物からなり第1の素子領域の表面部位に設けられたパンチスルー抑制層と、第1の素子領域に接する第2のゲート絶縁膜と、第2の素子領域に接し第2のゲート絶縁膜よりも膜厚の厚い第1のゲート絶縁膜とを備える。第1の不純物のプロファイルと第3の不純物のプロファイルとが交差する領域に、第2の不純物が分布する。

(もっと読む)

半導体装置の製造方法

【課題】p型MOSFETとn型MOSFETとの間で異なる所望のしきい値を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板上にHf、 Zrの少なくとも1つと、Si、O、Nを含むゲート絶縁膜を形成し、第1、第2のゲート電極層を形成し、第1のゲート電極層上および第2のゲート電極層上に、第1の金属含有層を形成し、第2の金属含有層を形成し、保護膜を形成し、保護膜を選択的に除去し、残存する保護膜をマスクとして、第1の金属含有層および第2の金属含有層を選択的に除去し、第1の金属含有層および第2の金属含有層が選択的に除去された第2のゲート電極層上に、第3の金属含有層を成膜し、加熱処理により、第1のゲート電極層を合金化するとともに、第2のゲート電極層を合金化し、異なる組成のゲート電極を形成する。

(もっと読む)

主電極を含むドープされた金属を含む半導体装置

【課題】良好な半導体装置およびそのような半導体装置を作製するための良好な方法を提供する。

【解決手段】半導体装置は、主電極(4)と主電極(4)に接触した誘電体(3)を含み、主電極(4)は、所定の仕事関数を有する材料と、主電極(4)の材料の仕事関数を予め決められた値に向かって変調する仕事関数変調元素(6)とを含み、更に、主電極(4)は、仕事関数変調元素(6)が誘電体(3)に向かっておよび/または誘電体(3)中に拡散するのを防止する拡散防止ドーパント元素(5)を含む。

(もっと読む)

半導体装置

【課題】シリコン基板表面に損傷及び汚染を与えることなく窒化シリコン膜を選択的に形成することによって同一シリコン基板内に種類の異なる複数のゲート絶縁膜を形成して成る半導体装置及びその製造方法を提供すること。

【解決手段】シリコン基板の表面に酸化シリコン膜を形成してからその一部を除去し、酸化シリコン膜を除去した基板面に窒化シリコン膜を形成すると同時に除去せずに残した酸化シリコン膜の表面に窒素を導入する。その他に、シリコン基板の表面に化学気相成長法により酸化シリコン膜を堆積してからその一部を除去し、酸化シリコン膜を除去した基板面に窒化シリコン膜を形成すると共に除去せずに残した酸化シリコン膜の表面に窒素を導入し、続いて窒素を導入した酸化シリコン膜を溶解除去して基板表面を露出させ、露出したシリコン基板の表面及び上記窒化シリコン膜を酸化する。

(もっと読む)

半導体装置及びその製造方法

【課題】PMOSにおけるキャリアの移動度を高くしつつ、なおかつNMOSの移動度を所望の程度に維持するようにした半導体装置及びその製造方法を提供する。

【解決手段】面方位が(110)であるシリコン基板に形成された埋め込み型NMOSと埋め込み型PMOSとを備え、埋め込み型NMOSのソース−ドレイン間の電流方向は<100>方向であり、埋め込み型PMOSのソース−ドレイン間の電流方向は<110>方向である。このような構成であれば、埋め込み型NMOSの移動度と埋め込み型PMOSの移動度はそれぞれ最大値となる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル幅やチャンネル長が異なるにも係らずほぼ同じ閾値電圧が要求される複数種類のトランジスタを有する半導体装置において、工程数を削減する。

【解決手段】半導体装置は、少なくともチャネル幅が互いに異なる複数のトランジスタを有しており、これらトランジスタの閾値電圧が、これらトランジスタへの実質的に等しいチャネルドーズ量と、これらトランジスタのゲート絶縁膜への所定金属の付着および/またはこれらトランジスタのゲート電極材料による仕事関数制御(すなわち、これらトランジスタのチャネル領域に対するゲート構造(ゲート絶縁膜および/またはゲート電極)に基づく仕事関数制御)との両方を用いて、ほぼ同じに設定されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ランダム成分によるトランジスタ特性のばらつきを抑制した、レトログレードチャネル構造を有するMISトランジスタを備えた半導体装置及びその製造方法を提供することにある。

【解決手段】レトログレードチャネル構造を有する第1のMISトランジスタのチャネル領域4aを、通常の表面チャネル構造を有する第2のMISトランジスタの厚い第2のゲート絶縁膜3c、3dの形成後に形成する。第2のMISトランジスタのチャネル領域4c、4dは、第2のゲート絶縁膜3c、3dが形成される前に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】CMOSトランジスタ等において、nチャネル型トランジスタとpチャネル型トランジスタとで、徒に実行困難な製造プロセスを伴うことなくゲート電極の十分な仕事関数差の確保を可能とし、トランジスタの駆動特性を大幅に向上させる。

【解決手段】nMOS領域及びpMOS領域の双方でNi2を用いてアニール処理により各多結晶シリコン膜1と反応させ、多結晶シリコン膜1をニッケルリッチ状態にシリサイド化する。その後、pMOS領域のみにマスク層4を形成して、nMOS領域のみにシリコンをイオン注入し、アニール処理することにより、nMOS領域にはシリコンリッチ状態のゲート電極5を、pMOS領域にはNiリッチ状態のゲート電極6を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】本発明は、PチャネルMOSFETのゲート電極に所定値以上の仕事関数を有するメタルを用いた場合であっても、適正なしきい値電圧を有する半導体装置及び当該半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、NチャネルMOSFET及びPチャネルMOSFETを含む半導体装置であって、前記PチャネルMOSFETのゲート電極は、第1の濃度の酸素を含有する第1の導電性膜110aと、前記第1の濃度より高い第2の濃度の酸素を含有する第2の導電性膜110bと、前記第2の濃度より低い第3の濃度の酸素を含有する第3の導電性膜110cと、を含む積層構造を有することを特徴とするものである。

(もっと読む)

ナノスケール電界効果トランジスタの構体

本発明は、ラップゲート構造を有する縦型ナノワイヤトランジスタに関する。縦型ナノワイヤトランジスタの閾値電圧は、ナノワイヤの直径、ナノワイヤの不純物添加レベル、ナノワイヤへのヘテロ構造のセグメントの導入、ナノワイヤを取り囲むシェル構造における不純物添加、ゲートスタックの仕事関数の適応、歪み調整、誘電体材料の制御又はナノワイヤ材料の選択により制御される。異なる閾値電圧を有するトランジスタが同一の基板上に形成されることにより、直接結合フィールドロジックと同様に、閾値電圧の変化を利用する最先端回路の設計が可能になる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】チャネルを構成する半導体材料にGe又はSiGeを用いて高速動作を実現するとともに、低温且つ簡易な製造プロセスにより、所望の閾値制御及び高い実効移動度特性を達成することを可能とするCMOSFETを実現する。

【解決手段】nMOSFET10では、ゲート電極13がNiSiで構成されたシリサイド層で形成されている。ゲート電極13の両側におけるGe基板2の表層には、NiGeで構成されたGermanide層であるNiGe層15が形成されている。NiGe層15とGe基板2との接合界面には、所定の原子が高濃度に偏析して形成されてなる第1の層16が形成され、ゲート電極13とゲート絶縁膜12との界面には、第1の層16と同じ原子が高濃度に偏析して形成されてなる第2の層17が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】同一の材料のメタルゲート電極をn型MOS領域およびp型MOS領域に用いて高精度で仕事関数を制御することができるCMOS型の半導体装置を提供すること。

【解決手段】半導体基板10の主面に形成されたnMOS領域37およびpMOS領域38を含むCMOS型の半導体装置であって、nMOS領域37は、WSi膜17を含むメタルゲート電極23を有し、pMOS領域38は、WSiN膜35を含むメタルゲート電極25を有し、WSiN膜35のN量を制御してその仕事関数を制御し、pMOS領域38におけるゲート電極25の閾値を制御する。

(もっと読む)

半導体装置及びその製造方法

【課題】仕事関数の値及び閾値が安定したフルシリサイドゲート電極を有する半導体装置を実現できるようにする。

【解決手段】本発明に係る半導体装置は、半導体基板の上に形成されたゲート絶縁膜15aと、ゲート絶縁膜の上に形成されたゲート電極23とを備えている。ゲート電極23は、層状の複数の結晶粒が積層されてなる金属シリサイド膜を有するフルシリサイドゲート電極である。

(もっと読む)

201 - 220 / 323

[ Back to top ]