Fターム[5F048BB18]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521) | 閾値電圧が異なる複数MOS (1,778) | 注入量、注入物質が異なるもの (323)

Fターム[5F048BB18]に分類される特許

141 - 160 / 323

半導体装置の製造方法および半導体装置

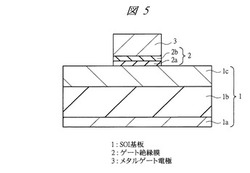

【課題】Hf−O系絶縁膜上に、TaCx膜を用いたメタルゲート電極を備えたMISトランジスタの実効仕事関数を制御する。

【解決手段】SOI基板1のシリコン層1c側よりゲート絶縁膜2を形成する。次いで、ゲート絶縁膜2上に室温スパッタ法によってTaCx膜を堆積し、このTaCx膜から構成されるメタルゲート電極3を形成する。次いで、メタルゲート電極3上にアモルファス状態のシリコン膜を形成した後、メタルゲート電極3に熱処理を施す。次いで、前記シリコン膜を除去した後、メタルゲート電極3に酸素を添加する。

(もっと読む)

半導体装置

【課題】高い反転層キャリア移動度を有するシングルメタルCMISFETを提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板上に形成されたpチャネルMISトランジスタとnチャネルMISトランジスタとを具備し、pチャネルMISトランジスタとnチャネルMISトランジスタは、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極層を夫々備え、pチャネルMISトランジスタとnチャネルMISトランジスタのゲート電極における、少なくともゲート絶縁膜と接する最下層は、TaとCを含む同一組成を有し、CとTaとの合計に対するTaのモル比(Ta/(Ta+C))が0.5より大であり、最下層は同一配向性を有することを特徴とする。

(もっと読む)

半導体装置

【課題】メタルをゲート電極材料に用いたCMIS素子の閾値を低減する。

【解決手段】p型MISトランジスタQpのゲート絶縁膜5上に設けられたp型ゲート電極7は、順に、カチオン比でAlが10%以上50%以下のTiAlNから構成される第1金属膜30と、TiNから構成され、膜厚が5nm以下の第2金属膜31と、Siを主成分として含有する導電体膜32とが積層された構造を有している。また、n型MISトランジスタQnのゲート絶縁膜5上に設けられたn型ゲート電極6は、順に、第2金属膜31と、導電体膜32とが積層された構造を有している。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】同一半導体基板上に第1導電型MOSトランジスタと第2導電型トランジスタとMOSキャパシタを形成するための半導体装置の製造方法において、製造工程を追加することなく、MOSトランジスタのしきい値電圧近傍で安定した容量をもつMOSキャパシタを製造する。

【解決手段】工程(2)でNchMOSトランジスタ9nの形成領域のP型ウェル3及びMOSキャパシタ11の形成領域のN型ウェル5にNchMOSトランジスタ9nのしきい値電圧調整用ボロンイオンを同時に注入し、かつPchMOSトランジスタ9pの形成領域のN型ウェル5には上記ボロンイオンを注入せず、MOSキャパシタ11とPchMOSトランジスタ9pでN型ウェル5の表面近傍の不純物イオン濃度プロファイルを異ならせる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】記憶情報を高速に読み出す半導体集積回路装置の製造方法を提供する。

【解決手段】本発明の半導体集積回路装置の製造方法は、半導体基板上に第1ゲート電極を形成する工程、この工程の後に第1ゲート電極を覆うように半導体基板上に導電性膜を形成する工程、この工程の後に導電性膜の一部を覆うように半導体基板上にマスクパターンを形成する工程、この工程の後にドライエッチングを行いマスクパターンで覆われていない導電性膜をサイドスペーサ状の第2ゲート電極に加工する工程で、且つマスクパターンで覆われた導電性膜を第2ゲート電極のコンタクト領域としてパターニングする工程、この工程の後にマスクパターンを除去する工程、この工程の後に不揮発性メモリセルを覆うように半導体基板上に層間絶縁膜を形成する工程、この工程の後に層間絶縁膜中に第2ゲート電極のコンタクト領域に接続するプラグを形成する工程、を有する。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート絶縁膜にHfを含むMOSトランジスタの特性のばらつきを抑制するために、Hf密度の面内ばらつきを少なくすることが必要である。

【解決手段】 半導体基板上に、熱酸化により酸化シリコンまたは酸窒化シリコンを含む絶縁膜(40)を形成する。絶縁膜の上にHfを含むガス(45)を供給して、絶縁膜の上にHf原子(41)を堆積させる。Hf原子が堆積している絶縁膜を、酸素雰囲気中(46)で熱処理する。酸素雰囲気中で熱処理した後、絶縁膜の上に、ゲート電極(50P,50N)を形成する。ゲート電極の両側に、ソース領域及びドレイン領域(52P,52N)を形成する。

(もっと読む)

半導体装置、キャパシタ、および電界効果トランジスタ

【課題】半導体と金属との界面において、接合する金属の実効仕事関数を最適化した半導体装置を提供することを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aとを備え、酸化膜がHf酸化膜或いはZr酸化膜であって、酸化膜に、V、Cr、Mn、Nb、Mo、Tc、W、Reから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体デバイスの製造方法および半導体デバイス

適切な仕事関数の材料のゲート電極を有する半導体デバイスの製造方法を開示する。この方法は、所定数の活性領域(110,120)および該活性領域(110,120)を被覆する誘電体層(130)を含む基板(100)を提供する工程と、前記誘電体層上に積層体(140,150,160)を形成する工程を有する。積層体の形成は、前記誘電体層(130)上に、第1の厚さ、例えば10nm未満を有する第1の金属層(140)を析出させる工程と、該第1の金属層(140)上に、第2の厚さを有する第2の金属層(150)を析出させる工程であり、前記第2の厚さが前記第1の厚さより厚い工程と、前記第2の金属層(150)にドーパント(152,154)を導入する工程と、前記デバイスを温度上昇下にさらし、前記ドーパント(152,154)の少なくとも一部を、前記第2の金属層(150)から前記第1の金属層(140)と前記第2の金属層(150)との界面を越えて、移動させる工程と、前記積層体を所定数のゲート電極(170)にパターニングする工程と、を有する。この方法によれば、ゲート電極は、誘電体層(130)の近くにドーパントプロファイルを有するように形成されるため、ゲート誘電体がドーパントの侵入により劣化することなく、ゲート電極の仕事関数を最適化することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】精度良く形成された第1,第2のゲート電極を実現すると共に、ゲート幅方向の幅が縮小化された素子分離領域を実現する。

【解決手段】第1のMISトランジスタは、第1のゲート絶縁膜13a上に形成された第2の金属膜30aからなる第1のゲート電極30Aと、第1のゲート電極の側面上から第1の活性領域10aにおける第1のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第2のMISトランジスタは、第2のゲート絶縁膜13b上に形成され第1の金属膜14bと第1の金属膜上に形成された導電膜30bとからなる第2のゲート電極30Bと、第2のゲート電極の側面上から第2の活性領域における第2のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第1の金属膜と第2の金属膜とは、互いに異なる金属材料からなり、第1,第2のゲート電極の上面上には絶縁膜が形成されていない。

(もっと読む)

半導体装置及びその製造方法

【課題】最小の工程数で尚且つ、特性が安定しており、スイッチングスピードの速いパワー半導体装置を実現する。

【解決手段】厚いゲート絶縁膜9及びこれよりも薄いゲート絶縁膜11を形成した後、ゲート電極材料を堆積し、ゲート絶縁膜9下のボディ領域の形成予定部位にp型不純物をイオン注入してp型不純物領域15を形成する。そして、ゲート絶縁膜9,11下にそれぞれp型不純物をイオン注入してボディ領域19a,19bをそれぞれ形成する。ボディ領域19aはp型不純物領域15と一体化する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】CMIS集積回路装置等の量産において、MISFETのゲート長等の変動により、Vth等の電気特性が変動する問題が、短チャネル化によって、深刻な問題となってきている。この問題を解決するために、先行する変動要因プロセスの変動を後続の変動要因プロセスを逆側に振って、変動要因を相殺するフィード・フォーワッド技術が種々検討されている。これらのフィード・フォーワッド技術は、相殺プロセスの効果が全体に及ぶため、単一種類のMISFETを搭載した製品では、比較的容易に適用できるものの、複数種類のMISFET搭載した製品では、適用が困難である。

【解決手段】本願発明は、ゲート電極パターニング工程およびオフセット・スペーサ成膜工程の結果に基づいて、多変量解析の手法により、ハロー注入量を調整するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】Nチャネル領域内、およびPチャネル領域内のチャネルに印加するストレスを制御でき、面積の増加抑制および歩留まりの低下を実現できる半導体装置およびその製造方法を提供する。

【解決手段】Nチャネル領域201内のコンタクトライナー513にSiより大きな元素イオンを注入して構成原子の結合を切断する。Pチャネル領域202内のコンタクトライナー513にSiより大きな元素イオンを注入して構成原子の結合を切断後、酸素などをイオン注入する。その後、熱処理を加えてNチャネル領域201内のコンタクトライナー513を収縮させてnチャネルコンタクトライナー518を形成し、Pチャネル領域202内のコンタクトライナー513を膨張させてpチャネルコンタクトライナー519を形成する。

(もっと読む)

半導体装置

【課題】低閾値動作に可及的に適した実効仕事関数を有するMISトランジスタを備えた半導体装置を提供することを可能にする。

【解決手段】Hf(或いはZr)酸化物に高価数金属を添加することでギャップ内準位を作りだし、窒素あるいはフッ素などによりギャップ内準位の位置を変化させることで、最適な実効仕事関数を有する電極を備え、低閾値動作が可能なCMISデバイスを実現した。

(もっと読む)

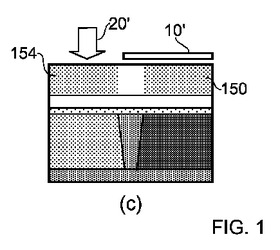

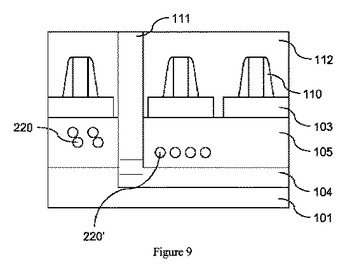

埋め込み型トラッピング層によるトランジスタの閾値電圧の調整方法

方法は、電子サブアセンブリの形成について、調整可能な閾値電圧を有する少なくとも1つの第1のトランジスタ(110)を担持する半導体層(103)が絶縁層(102、105)に接合される組み立てステップと、半導体層および第1のトラッピングゾーンが容量結合されるように、第1のトラッピングゾーン(220)が所定の第1の深さで絶縁層に形成される形成ステップであって、前記第1のトラッピングゾーンが、前記第1のトランジスタのチャネルの少なくとも下に延び、かつ前記第1のトラッピングゾーンの外側のトラップの密度より高い密度のトラップを有する形成ステップとを含み、前記第1のトランジスタからの有用な情報はこのトランジスタ内の電荷移動である。具体的な実施形態において、第2のトランジスタのチャネルの少なくとも下に延びる第2のトラッピングゾーンが、第1のトラッピングゾーンに使用されるのとは異なるエネルギーおよび/または用量および/または原子の第2の注入によって形成される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】組成の安定したゲート電極を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板11に、ゲート長に加工された、ゲート絶縁膜21、シリコン材料膜23a、ストッパ膜25、及びシリコン材料膜23bを順に有する第1の積層膜を備えたpMOS領域1、離間して、ゲート長に加工された、ゲート絶縁膜21、シリコン材料膜23a、及びシリコン材料膜23bを順に有する第2の積層膜を備えたnMOS領域2を形成し、第1及び第2の積層膜の側壁にオフセット膜33、サイドウォール35の形成、及びソース・ドレイン領域15の形成を行い、pMOS領域1のシリコン材料膜23b及びストッパ膜25を除去し、シリコン材料膜23a上、及びnMOS領域2のシリコン材料膜23b上にNiを堆積し、pMOS領域1にNi3Siを形成し、nMOS領域2にNiSi2を形成する。

(もっと読む)

半導体装置の製造方法

【課題】所望のMOSトランジスタのみにチャネル領域に引っ張り応力を印加してキャリア移動度を向上させ、且つ、製造工程の複雑化を抑える。

【解決手段】シリコン基板10上にnMOSトランジスタのゲート絶縁膜13およびゲート電極14を非単結晶シリコンで形成し、ゲート電極14をマスクとして例えばAsやSb等の比較的質量数が大きい(質量数70以上)n型ドーパントを注入することで、nMOSトランジスタのソースドレイン領域を形成する。それにより、ゲート電極14は非晶質化する。そして、ゲート電極14が再結晶化する温度(約550℃)以下の温度条件でゲート電極14を覆うようにシリコン酸化膜40を形成し、その後1000℃程度の加熱処理を行う。それにより、ゲート電極14内に強い圧縮応力が残留すると共に、その下のチャネル領域には強い引っ張り応力が印加され、当該nMOSトランジスタのキャリア移動度は向上する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜とゲート電極を工夫することにより、ゲート空乏化を抑制しつつ実効仕事関数を制御することを可能とする。

【解決手段】P型の絶縁ゲート型電界効果トランジスタの第1トランジスタ2と、N型の絶縁ゲート型電界効果トランジスタの第2トランジスタ3とを有し、前記第1トランジスタ2のゲート絶縁膜21と前記第2トランジスタ3のゲート絶縁膜21は、前記ゲート電極側に金属不純物22が存在していて、前記第1トランジスタ2のゲート電極23NがN型のポリシリコンである、もしくは前記第2トランジスタ3のゲート電極23PがP型のポリシリコンである、もしくは前記第1トランジスタ2のゲート電極23NがP型のポリシリコンであり前記第2トランジスタ3のゲート電極23PがP型のポリシリコンであることを特徴とする。

(もっと読む)

スタティックランダムアクセスメモリの製造方法

【課題】改善された性能および安定を備えたSRAMビットセルを製造できるスタティックランダムアクセスメモリの製造方法を提供する。

【解決手段】それぞれ2個のパスゲートトランジスタ302、プルダウントランジスタ304、及びプルアップトランジスタ306を有するSRAMビットセル300が形成され、シリコン窒化膜308が全面に堆積され、その後、プルダウントランジスタ304上にシリコン窒化膜308が形成され、その後、高温アニール処理が行われることにより、シリコン窒化膜308によってカバーされた領域が再結晶化され、歪が導入され、その後、シリコン窒化膜308が除去される。

(もっと読む)

トランジスタ、半導体装置、半導体装置の製造方法

【課題】 占有面積を拡大することなく特性バラツキの抑制を可能にする半導体装置及びその製造方法を提供する。

【解決手段】 低濃度P型の半導体基板1の上層にゲート酸化膜3を形成した後、ゲート酸化膜3上層にP型のゲート電極4を形成する。その後、ゲート酸化膜3及びゲート電極4をマスクとしてN型の不純物イオンを注入することで、N型のソース・ドレイン拡散領域6を複数離間形成する。その後、半導体基板1及びゲート電極4の上層に層間絶縁膜7を形成した後、各ソース・ドレイン拡散領域6及びゲート電極4夫々との電気的接続を確保する複数のコンタクトプラグ8を形成する。その後、所望の閾値電圧となるよう、コンタクトプラグ8を介してソース・ドレイン拡散領域6とゲート電極4の間に所定の高電圧を印加してゲート酸化膜3内に正電荷を注入する。

(もっと読む)

半導体装置およびその製造方法

【課題】High−K膜からなるゲート絶縁膜と基板との間に1nm以下の厚さの界面層を有し、再酸化による界面層の膜厚増加を抑えることができ、微細化が可能となる半導体装置を提供する。

【解決手段】シリコン基板1のチャネル領域3上にシリコン酸化物よりも誘電率の高い高誘電率材料膜(High−K膜13)を介して形成されるゲート電極14と、チャネル領域3を挟んだシリコン基板1の表面に形成されたソース/ドレイン領域17とを備える半導体装置であって、シリコン基板1と高誘電率材料膜との間に、シリコン基板1との界面付近に厚さ方向の窒素濃度分布のピークを有し、厚さが0.2〜1nmのシリコン酸窒化膜からなる界面層12を備える。

(もっと読む)

141 - 160 / 323

[ Back to top ]