Fターム[5F048BB18]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521) | 閾値電圧が異なる複数MOS (1,778) | 注入量、注入物質が異なるもの (323)

Fターム[5F048BB18]に分類される特許

81 - 100 / 323

半導体装置およびその製造方法

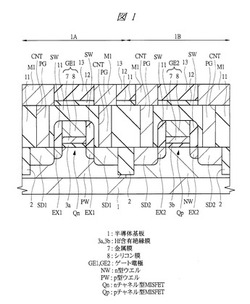

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】nチャネル型MISFETQnは、半導体基板1のp型ウエルPWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3aを介して形成されたゲート電極GE1を有し、pチャネル型MISFETQpは、n型ウエルNWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3bを介して形成されたゲート電極GE2を有している。ゲート電極GE1,GE2は、金属膜7とその上のシリコン膜8との積層構造を有している。Hf含有絶縁膜3aは、Hfと希土類元素とSiとOとNとからなる絶縁材料膜またはHfと希土類元素とSiとOとからなる絶縁材料膜であり、Hf含有絶縁膜3bは、HfとAlとOとNとからなる絶縁材料膜またはHfとAlとOとからなる絶縁材料膜である。

(もっと読む)

半導体装置及びその製造方法

【課題】High-k/metalゲート電極構造において各極性のFETに要求される仕事関数値を実現する。

【解決手段】第1の領域と第2の領域とを有する半導体基板101の上にゲート絶縁膜103を形成する。次に、ゲート絶縁膜103の上に第1の金属窒化膜105を堆積する。次に、第1の金属窒化膜105における第2の領域に位置する部分を除去することにより、ゲート絶縁膜103における第2の領域に位置する部分を露出させる。次に、ゲート絶縁膜103における第2の領域に位置する部分の上に、第1の金属窒化膜105と同じ金属窒化物からなる第2の金属窒化膜107を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】閾値電圧が相対的に高い半導体装置のチャネル領域における不純物濃度を閾値電圧が相対的に低い半導体装置のチャネル領域における不純物濃度よりも高くすると、閾値電圧が相対的に高い半導体装置の駆動力の低下を招来する虞があった。

【解決手段】半導体装置は、第1のトランジスタと第2のトランジスタとを備えている。第1のトランジスタは、第1のチャネル領域3aと、第1のゲート絶縁膜4aと、第1のゲート電極5aと、第1のエクステンション領域8aとを有している。第2のトランジスタは、第1のトランジスタよりも高い閾値電圧を有しており、第2のチャネル領域3bと、第2のゲート絶縁膜4bと、第2のゲート電極5bと、第2のエクステンション領域8bとを有している。第2のエクステンション領域8bは浅接合化不純物を含んでおり、第2のエクステンション領域8bの接合深さは第1のエクステンション領域8aの接合深さよりも浅い。

(もっと読む)

半導体装置及びその製造方法

【課題】相異なる動作電圧の第1,第2,第3のMISトランジスタを有する半導体装置において、第1,第2,第3のチャネル拡散層の不純物プロファイルの変動を抑制する。

【解決手段】半導体装置は、第1,第2,第3の活性領域上に第1,第2,第3のゲート絶縁膜13A,13B,14Cを介して形成された第1,第2,第3のゲート電極を有する第1導電型の第1,第2,第3のMISトランジスタを備えている。第1のゲート絶縁膜13Aは、第1のシリコン酸化膜13aと第1の高誘電率絶縁膜15aとからなる。第2のゲート絶縁膜13Bは、第2のシリコン酸化膜13bと第2の高誘電率絶縁膜15bとからなる。第3のゲート絶縁膜14Cは、第3のシリコン酸化膜14cと第3の高誘電率絶縁膜15cとからなる。第2のシリコン酸化膜13bは、第1のシリコン酸化膜13aと同じ膜厚を有し、且つ、第3のシリコン酸化膜14cよりも厚い膜厚を有している。

(もっと読む)

半導体装置及びその製造方法

【課題】複数のゲート長を有するトランジスタを形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、第1の柱状体と第2の柱状体とを形成する工程と、前記第1及び第2の柱状体と前記半導体基板とを覆う半導体膜であって、前記第1の柱状体を覆う第1の部分と前記第2の柱状体を覆う第2の部分との導電型及び不純物の濃度の少なくとも一方が互いに異なるように半導体膜を形成する工程と、前記半導体膜をエッチバックして、前記第1及び第2の柱状体のそれぞれの側壁に、互いに異なる高さを有する第1の半導体膜柱状部と第2の半導体膜柱状部とを形成する工程と、を備えることを特徴とする半導体装置の製造方法を採用する。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜及びメタルゲート電極を備えたCMISFETの生産性や性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有絶縁膜5を形成し、その上に窒化金属膜7を形成し、窒化金属膜7上のフォトレジストパターンをマスクにしたウェットエッチングによって、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aの窒化金属膜7を選択的に除去する。それから、希土類元素を含有するしきい値調整層8を形成し、熱処理を行って、nMIS形成領域1AのHf含有絶縁膜5をしきい値調整層8と反応させるが、pチャネル型MISFET形成予定領域であるpMIS形成領域1BのHf含有絶縁膜5は、窒化金属膜7があるためしきい値調整層8とは反応しない。その後、未反応のしきい値調整層8と窒化金属膜7を除去してから、nMIS形成領域1AとpMIS形成領域1Bにメタルゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】短いゲート長を加工可能にする半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法の一形態は、シリコン基板2上にシリコン酸化膜34を形成し、酸化膜34上に所定幅T1を有する多結晶シリコン膜35aを形成し、少なくとも多結晶シリコン膜35aの両側部を酸化し、所定幅T1よりも狭い幅を有する酸化膜34の部分を多結晶シリコン膜35aの下に残すように、酸化膜34を、多結晶シリコン膜35aの酸化された部分と共にエッチングし、酸化された部分がエッチングされた多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入し、多結晶シリコン膜35aの両側に側壁絶縁膜14を形成し、側壁絶縁膜14が形成された多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入する、工程を有する。

(もっと読む)

デュアルゲート不純物ドーピング方法及びこれを用いたデュアルゲート形成方法

【課題】デュアルゲート不純物ドーピング方法及びこれを用いたデュアルゲート形成方法を提供する。

【解決手段】デュアルゲート不純物ドーピング方法は、第1領域及び第2領域を有する半導体基板上のゲート導電膜に第1導電型の不純物イオンをドープする段階であって、ゲート導電膜の下部よりも上部における不純物ドーピング濃度がより高い濃度勾配でドープする段階と、第2領域のゲート導電膜をオープンさせるマスクを用いて第2領域のゲート導電膜に第2導電型の不純物イオンをドープする段階と、熱処理を行い、第1導電型及び第2導電型の不純物イオンを拡散させる段階と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのしきい値電圧制御のために使用する金属酸化膜の膜減り等に起因するしきい値電圧ばらつきを抑制し、所望のしきい値電圧を有するトランジスタを形成することができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板1上に、高融点金属酸化物を含む材料からなるゲート絶縁膜3が形成され、ゲート絶縁膜3上に金属酸化膜4が形成される。次いで、金属酸化膜4を構成する金属原子を、金属酸化膜4からゲート絶縁膜3の表面部へ拡散させる処理が実施される。当該金属原子の拡散工程後、上記金属酸化膜4がゲート絶縁膜3に対して選択的に除去される。そして、金属原子が拡散されたゲート絶縁膜3上に導電膜7、8が形成され、当該導電膜7、8を加工することでゲート電極30、31が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】複数の閾値を有し、ダストや不純物の局所的なばらつきによる歩留りの低下や、信頼性の低下を抑えることが可能な半導体装置とその製造方法を提供する。

【解決手段】半導体基板(Sub.)に形成された第1導電型のMOSFETと第2導電型のMOSFETを有し、前記第1導電型のMOSFETは、第1導電型の不純物を含む第1のゲート電極15aと、第2導電型の不純物を含む第2のゲート電極15bとを備え、前記第2導電型のMOSFETは、第1導電型の不純物を含む第3のゲート電極15cと、第2導電型の不純物を含む第4のゲート電極15dとを備える。

(もっと読む)

半導体装置の製造方法

【課題】

製造工程を簡略化しつつ、特性の優れた第1のMOSトランジスタと第2のMOSトランジスタとを製造する半導体装置の製造方法を提供する。

【解決手段】

半導体基板に、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域を画定する素子分離領域を形成し、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域に第1導電型の不純物をイオン注入し、第1導電型のウェルを形成し、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域上に絶縁ゲート電極を形成し、第2のMOSトランジスタのドレイン領域を覆うマスクを介して、半導体基板法線方向から傾いた複数方向から第1導電型の不純物をイオン注入し、第1のMOSトランジスタ領域の前記絶縁ゲート電極下方に対称的なチャネルドーズ領域、第2のMOSトランジスタ領域の前記絶縁ゲート電極下方に非対称なチャネルドーズ領域を形成し、半導体装置を製造する。

(もっと読む)

半導体装置

【課題】寿命を可及的に長くすることの可能なMISFETを備えた半導体装置を提供する。

【解決手段】半導体領域2が形成された半導体基板1と、半導体領域に離間して形成されたソース領域5aおよびドレイン領域5bと、ソース領域とドレイン領域との間の半導体領域3上に形成され金属および酸素を含む金属酸化層12を有するゲート絶縁膜10と、ゲート絶縁膜上に形成されたゲート電極16と、を有するMISFETを備え、金属酸化層に含まれる金属はHf、Zrのうちから選択された少なくとも1つであり、金属酸化層は、更にRu、Cr、Os、V、Fe、Tc、Nb、Taのうちから選択された少なくとも1つの元素が添加され、金属酸化層は元素が添加されたことにより形成される電荷を捕獲または放出する電荷トラップを有し、金属酸化層中における元素の密度は、1×1015cm−3以上、2.96×1020cm−3以下の範囲にあり、電荷トラップは、金属酸化層の中央より半導体領域側にピークを有するように分布することを特徴とする。

(もっと読む)

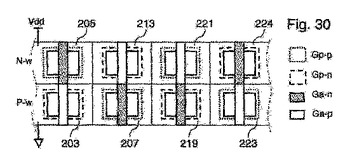

明白に異なる閾値電圧を有するトランジスタを持つSOIから製造する集積回路

本発明は、埋め込まれた絶縁材料面によって半導体基板層から隔てられた活性半導体層を含む集積回路に関する。この集積回路は、同じ型の第1および第2のトランジスタ(205、213)と、第1および第2のトランジスタの真下に配置された第1および第2の接地面とを有し、第1のトランジスタの接地面のドーピングは、第1のトランジスタのソースのドーピングと反対のドーピングであり、第1の閾値電圧を有する。第2のトランジスタの接地面のドーピングは、第2のトランジスタのソースのドーピングと同一のドーピングであり、第2の閾値電圧を有する。第1の閾値電圧は、第1のトランジスタのソースと接地面との間に印加される電位差に依存し、第2の閾値電圧は、第2のトランジスタのソースと接地面との間に印加される電位差に依存する。  (もっと読む)

(もっと読む)

ソース/ドレイン延長部又は/及びハローポケットと組み合わせて空のウエルを使用した電界効果トランジスタの構成及び製造

【課題】 混合信号適用例を含むアナログ及びデジタル適用例用のIGFETを与える半導体製造プラットフォームに適した対称的及び非対称的の両方の絶縁ゲート電界効果トランジスタ(「IGFET」)が、高性能を達成する上で空のウエル領域を使用する。

【解決手段】 各空のウエルの上部近くにおいては半導体ウエルドーパントが比較的少量である。各IGFET(100,102,112,114,124又は236)は、空のウエル(180,182,192,194,204又は206)のボディ物質のチャンネルゾーンによって横方向に分離された一対のソース/ドレインゾーンを有している。ゲート電極が該チャンネルゾーン上方でゲート誘電体層の上側に位置している。各ソース/ドレインゾーン(240,242,280,282,520,522,550,552,720.722、752又は752)が主要部分(240M,242M,280M,282M,520M,522M,550M,552M,720M,722M,752M又は752M)及び一層軽度にドープした横方向延長部(240E,242E,280E,282E,520E,522E,550E,552E,720E,722E,752E又は752E)を有している。代替的に又は付加的に、該ボディ物質の一層高度にドープしたポケット部分(250又は290)が該ソース/ドレインゾーンの内の一方に沿って延在する。存在する場合には、該ポケット部分は典型的に該IGFETを非対称的装置とさせる。

(もっと読む)

液晶表示装置

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】 リーク電流の低減を実現しながらも従来に比べて更に素子サイズを縮小させることが可能な、高耐圧MOSトランジスタを実現する。

【解決手段】 P型ウェル10上に、チャネル領域chを隔てて、ドレイン領域12及びドレイン側ドリフト領域7を含むN型の第一不純物拡散領域と、ソース領域12及びそース側ドリフト領域8を含むN型の第二不純物拡散領域が形成されている。また、第一不純物拡散領域の一部上方、前記チャネル領域の上方、及び前記第二不純物拡散領域の一部上方にわたってゲート酸化膜6を介してゲート電極20が形成されている。ゲート電極20は、N型にドープされており、第一及び第二不純物拡散領域の上方に位置する部分の電極20bの不純物濃度が、前記チャネル領域の上方に位置する部分20aの不純物濃度よりも低濃度である。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】TDDB寿命が改善された容量素子を有する半導体集積回路装置を提供すること。

【解決手段】半導体集積回路装置1は、基板平面に対して突起する第1半導体層を有する第1電極4と、第1電極4の少なくとも一部の側面に形成された側面絶縁膜5と、第1電極4上及び側面絶縁膜5上に形成された上面絶縁膜6と、側面絶縁膜5及び上面絶縁膜6を覆う第2電極7と、を備える。第1電極4、側面絶縁膜5及び第2電極7は容量素子を形成する。上面絶縁膜6の第1電極4と第2電極7間の厚さは、側面絶縁膜5の第1電極4と第2電極7間の厚さよりも厚い。

(もっと読む)

半導体装置

【課題】回路動作の安定性を高め、消費電力の低減を可能とした半導体装置を提供する。

【解決手段】フローティングボディ型のPD−SOI−MOSFET21〜26を有する分周回路を備え、この分周回路の動作時は、MOSFET22、23,24、26の各ゲート(G)に固定電圧が印加されてMOSFET22、24がオンすると共に、MOSFET23、26がオフする。また、MOSFET21、25の各ゲート(G)に振幅電圧が印加されて、MOSFET21、25がオン、オフを繰り返す。このように動作する分周回路において、MOSFET23、26の閾値電圧の絶対値は、例えばチャネルドープにより、MOSFET21、25の閾値電圧の絶対値よりも大きく設定されている。

(もっと読む)

半導体装置の製造方法

【課題】歩留まりが向上して信頼性の高いフラッシュメモリセルを備えた半導体装置の製造方法を提供すること。

【解決手段】第1窓70aを有する第1レジストパターン70を第2絶縁膜69上に形成する工程と、第1レジストパターン70をエッチングマスクにしてコンタクト領域CRが露出する第1開口69dを形成する工程と、第1レジスト部76aを有する第2レジストパターン76を第2導電膜74上に形成する工程と、第2レジストパターン76をエッチングマスクにし、第1、第2導電体67a、74a、フローティングゲート67d、及びコントロールゲート74dを形成する工程と、第3レジストパターン80を各領域I、IIに形成する工程と、第3レジストパターン80をエッチングマスクにして第2窓80a下の第2導電体74aを除去する工程と、を有する半導体装置の製造方法による。

(もっと読む)

基準電圧発生回路装置

【課題】デプレッション型MOSトランジスタとエンハンス型MOSトランジスタによって形成される基準電圧発生回路装置の面積を大きくすることなく基準電圧の温度特性を向上させる。

【解決手段】デプレッション型MOSトランジスタの濃度プロファイルを、第一導電型チャネル領域の基板表面側の不純物濃度が薄く、かつ前記第一導電型チャネル領域と第二導電型の基板領域もしくはウェル領域にて形成されるPN接合付近の前記第一導電型チャネル領域の不純物濃度が濃くなるように制御することで基準電圧の温度特性を向上させる。

(もっと読む)

81 - 100 / 323

[ Back to top ]