Fターム[5F048BB18]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 閾値制御 (2,521) | 閾値電圧が異なる複数MOS (1,778) | 注入量、注入物質が異なるもの (323)

Fターム[5F048BB18]に分類される特許

41 - 60 / 323

半導体装置及びその製造方法

【課題】High-kゲート絶縁膜を用いたMOSFETにおいて、信頼性劣化、チャネル移動度低下及びEOTの増加を抑制する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、シリコン酸化物を含む第1絶縁層104を形成する工程(a)と、第1絶縁層104上に第1金属層105を形成する工程(b)と、第1金属層105上にゲート電極108を形成する工程(c)とを備える。第1絶縁層104及び第1金属層105からゲート絶縁膜を形成する。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】同一のチップに含まれるMISトランジスタの閾値電圧に、ばらつきが生じることを抑制する。

【解決手段】ゲート絶縁膜形成膜上に高融点金属膜16を形成する。次に、高融点金属膜をパターニングして、ゲート絶縁膜形成膜における第1の部分を露出する一方、ゲート絶縁膜形成膜における第2の部分を覆う金属マスク16bを形成すると共に、ゲート絶縁膜形成膜における第3の部分を覆うダミー金属マスク16cを形成する。次に、ゲート絶縁膜形成膜上に、調整用金属化合物膜17を形成する。次に、金属マスク及びダミー金属マスクを導入防止マスクとして、熱処理によりゲート絶縁膜形成膜に調整用金属化合物膜中の調整用金属を導入する。次に、調整用金属化合物膜、金属マスク及びダミー金属マスクを除去する。次に、ゲート絶縁膜形成膜上に、ゲート電極形成膜20を形成する。次に、ゲート電極形成膜及びゲート絶縁膜形成膜をパターニングする。

(もっと読む)

半導体装置およびその製造方法

【課題】pチャネル型の電界効果トランジスタのしきい値電圧を確実に制御して所望の特性が得られる半導体装置と、その製造方法とを提供する。

【解決手段】温度約700〜900℃のもとで施す熱処理に伴い、素子形成領域RPでは、アルミニウム(Al)膜7a中のアルミニウム(Al)がハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)が添加される。また、チタンアルミニウムナイトライド(TiAlN)膜からなるハードマスク8a中のアルミニウム(Al)とチタン(Ti)とがハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)とチタン(Ti)とが添加される。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体装置及びその製造方法

【課題】工数を大幅に増加せず且つ高誘電体からなるゲート絶縁膜にダメージを与えることがない、仕事関数変更用金属不純物膜の効果を有する半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板101と、半導体基板101の上部に形成されたp型活性領域110と、p型活性領域110の上に形成されたゲート絶縁膜150と、ゲート絶縁膜150の上に形成されたゲート電極106とを有している。ゲート絶縁膜150は、二酸化シリコンよりも大きい誘電率を有する高誘電体膜103と、高誘電体膜103の上に形成され、炭素を含む炭素含有膜104とを有している。高誘電体膜103及び炭素含有膜104は、第1の金属としてランタン又はマグネシウムを含み、ゲート電極106は、第2の金属を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート幅が互いに異なる第1,第2のMISトランジスタを備えた半導体装置において、第1,第2のMISトランジスタの閾値電圧を、所望の閾値電圧に制御する。

【解決手段】半導体装置は、第1,第2のMISトランジスタを備えた半導体装置である。第1のMISトランジスタは、第1の高誘電率絶縁膜15aを有する第1のゲート絶縁膜15Aと、第1のゲート電極20Aとを備えている。第2のMISトランジスタは、第2の高誘電率絶縁膜15bを有する第2のゲート絶縁膜15Bと、第2のゲート電極20Bとを備えている。第1,第2のゲート絶縁膜は、調整用金属を含む。第1のMISトランジスタの第1のゲート幅W1は、第2のMISトランジスタの第2のゲート幅W2よりも小さい。第1のゲート絶縁膜中における調整用金属の平均調整用金属濃度は、第2のゲート絶縁膜中における調整用金属の平均調整用金属濃度に比べて低い。

(もっと読む)

半導体装置の製造方法

【課題】FEOLにおいても半導体装置のチャージングを効果的に抑制できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に、被保護素子のゲート絶縁膜となる第1の絶縁膜122を形成する工程(a)と、保護素子部302において第1の絶縁膜122の少なくとも一部を除去する工程(b)と、工程(b)よりも後に、被保護素子部301において第1の絶縁膜122の表面を窒化する工程(c)と、工程(c)よりも後に、被保護素子部301及び保護素子部302の上に跨るように導電膜を選択的に形成することにより、互いに接続された被保護素子のゲート電極141及び保護素子の電極142を形成する工程(d)とを備えている。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】低閾値動作が可能な電界効果トランジスタを提供する。

【解決手段】n型半導体領域2と、半導体領域に離間して形成されたソース領域およびドレイン領域12a、12bと、ソース領域12aとドレイン領域12bとの間の半導体領域上に形成され、シリコンと酸素を含む第1絶縁膜4と、第1絶縁膜上に形成され、Hf、Zr、Tiから選ばれた少なくとも1つの物質と酸素を含む第2絶縁膜8と、第2絶縁膜上に形成されたゲート電極10と、を備え、第1絶縁膜と第2絶縁膜との界面7aを含む界面領域7に、Geが導入されており、Geの面密度が、界面領域7内の第1絶縁膜4側においてピークを有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】電界効果型トランジスタの閾値電圧を精度よく制御することができ、かつその範囲を広くする。

【解決手段】この半導体装置は、ゲート絶縁膜120及びゲート電極130を有する電界効果型トランジスタ101を備える。ゲート絶縁膜120は、界面層110と高誘電率膜112とを積層した構成を有している。高誘電率膜112は、酸化シリコンより誘電率が高い金属酸化物からなる。そしてゲート絶縁膜120は、高誘電率膜112と界面層110の界面近傍に、窒素を含有する窒素含有層を有している。窒素含有層は高誘電率膜112から界面層110に渡って形成されている。窒素含有層において、窒素の濃度は高誘電率膜112と界面層110の界面が最も高い。

(もっと読む)

半導体装置及びその製造方法

【課題】しきい値電圧を制御しやすく、信頼性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、支持基板(Si基板1)、絶縁層(埋め込み絶縁膜2)および、SOI層(極薄Si層3)が順に積層してなる基板と、極薄Si層3上の少なくとも一部に設けられたトランジスタと、を備え、トランジスタの直下の極薄Si層3が、空乏化しており、埋め込み絶縁膜2と極薄Si層3との間の界面に、界面準位生成不純物が位置しており、界面の界面準位生成不純物の濃度は、埋め込み絶縁膜2中の界面準位生成不純物の濃度より高い。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

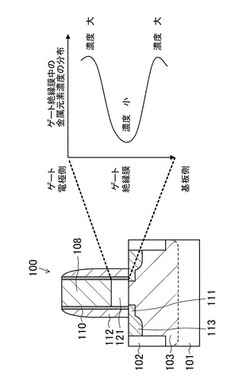

半導体装置

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリ混載ロジックデバイスのRAM領域の閾値電圧のばらつきを低減する。

【解決手段】本発明の半導体装置は、ロジック領域101と、RAM領域102とが設けられたシリコン基板1と、ロジック領域101に形成されたNMOSトランジスタ20と、RAM領域102に形成されたNMOSトランジスタ40と、を備える。NMOSトランジスタ20、40は、ゲート絶縁膜5とメタルゲート電極6との順でシリコン基板1上に積層された積層構造を有する。NMOSトランジスタ20は、シリコン基板1とメタルゲート電極6との間に、構成元素として、ランタン、イッテルビウム、マグネシウム、ストロンチウム及びエルビウムからなる群から選択される元素を含む、キャップメタル4を有する。NMOSトランジスタ40には、キャップメタル4が形成されていない。

(もっと読む)

半導体装置の製造方法

【課題】エンハンスメント型FETとディプレッション型FETとを半導体基板上に集積する場合に製造コストを低減できる半導体装置の製造方法を提供する。

【解決手段】この製造方法は、ディプレッション型電界効果トランジスタの形成予定領域12Daでゲート電極12に開口部32,33を形成する工程と、ゲート電極12をマスクとして、アクティブ領域21に不純物を斜めイオン注入することにより、開口部32,33の下方にゲート電極12の両側の一方から他方にかけて連続的に分布する不純物拡散領域を形成すると同時に、ゲート電極12の両側にそれぞれ不純物拡散領域を形成する工程とを含む。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置

【課題】放電効率の向上と、通常動作時の電位変動の伝達の抑制とを両立させることができる静電気保護素子を有する半導体装置を提供すること。

【解決手段】第1電源電位配線と第1接地電位配線との間にて、電気的に接続された第1回路、及びダイオード接続されたMOSトランジスタを有する第1保護素子と、第2電源電位配線と第2接地電位配線との間にて、電気的に接続された第2回路、及びダイオード接続されたMOSトランジスタを有する第2保護素子と、前記第1接地電位配線と前記第2接地電位配線との間に2つのMOSトランジスタが互いに逆バイアス状態になるように並列にダイオード接続された第3保護素子と、を備え、前記第3保護素子における2つのMOSトランジスタの閾値電圧は、前記第1保護素子及び前記第2保護素子における各MOSトランジスタの閾値電圧よりも大きく設定されている。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得るとともに、ここに提示される更なる構造及び方法は、更なる利益を生み出すように単独あるいはDDCとともに使用され得る。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】注入マスクの低減が図られる半導体装置の製造方法と、そのような半導体装置を提供する。

【解決手段】レジストマスク31と他のレジストマスクを注入マスクとして、NMOS領域RNにボロンを注入することにより、アクセストランジスタおよびドライブトランジスタのハロ領域となるp型不純物領域が形成される。さらに他のレジストマスクを注入マスクとして、PMOS領域RPにリンまたは砒素を注入することにより、ロードトランジスタのハロ領域となるn型不純物領域が形成される。

(もっと読む)

41 - 60 / 323

[ Back to top ]