Fターム[5F048BC02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 形状 (1,394) | 分割ドレイン(ソース) (356)

Fターム[5F048BC02]に分類される特許

121 - 140 / 356

半導体装置

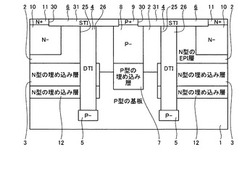

【課題】対基板耐圧が向上しチップシュリンクも実現可能な、DTI構造を有する半導体装置を提供する。

【解決手段】例えばP型の基板1と、この基板1上に形成されたN型のEPI層2と、基板1とEPI層2とにわたって形成されたN型の第1の埋め込み層(埋め込み層3)と、この第1の埋め込み層の下に形成され埋め込み層3よりも不純物濃度の低いN型の第2の埋め込み層(埋め込み層12)と、EPI層2の表面から埋め込み層12、埋め込み層3を貫通して基板1内に達するDTI4と、を備えた半導体装置。

(もっと読む)

半導体集積回路

【課題】トランジスタの特性ばらつきによる遅延回路の遅延時間の変動を抑制することが可能で、更に、製造工程における加工ばらつきに強く、レイアウト拡張性に優れた半導体集積回路を小面積に提供する。

【解決手段】第1の電源VDDと第2の電源(接地電源)との間に直列に接続されたP型MOSトランジスタMP11と2以上のN型MOSトランジスタMN11、MN12とが備えられる。入力端子INは前記P型MOSトランジスタMP11のゲート端子と前記N型MOSトランジスタMN11、MN12のゲート端子とに接続される。更に、P型MOSトランジスタMP11とN型MOSトランジスタMN11の接点である出力端子OUTに接続した1以上の容量素子C1を有し、P型MOSトランジスタMP11の駆動能力を、2以上に直列接続したN型MOSトランジスタMN11、MN12の総駆動能力よりも大きく構成する。

(もっと読む)

半導体装置

【課題】ゲート長によらずトランジスタ特性を向上させることが可能な半導体装置を提供する。

【解決手段】半導体装置は、第1の結晶面上に形成された第1のNチャンネルFinFETと、第1の結晶面上に形成され、第1のNチャンネルFinFETよりもゲート長が長い第2のNチャンネルFinFETとを具備する。第1のNチャンネルFinFETのフィン部の側面と、第2のNチャンネルFinFETのフィン部の側面とは、共に第1の結晶面のキャリア移動度よりも遅いキャリア移動度を有する第2の結晶面に形成されている。第2のNチャンネルFinFETの前記フィン部の幅は、第1のNチャンネルFinFETの前記フィン部の幅よりも広い。

(もっと読む)

回路基板の製造方法、回路基板、電気光学装置及び電子機器

【課題】特性に大きなばらつきのない半導体装置を形成し、これによって動作速度が安定した半導体装置、及び安定した出力の論理を有する論理素子を備えた回路基板、およびその製造方法を提供すること。

【解決手段】1以上のノズル320を備える液体吐出装置310から半導体材料液を吐出して半導体層140を形成する回路基板の製造方法であって、予め設定された1以上の回路形成領域を横切って、互いに平行な第1乃至第nの直線(nは2以上の整数)が予め定められており、前記ノズル320が第1の直線上をスキャンしながら回路基板上に半導体材料液を塗布することで、前記第1の直線方向に延在する複数の半導体層140を形成する工程を有し、前記半導体層140を形成する工程を、それぞれ前記第1乃至第nの直線について行う。

(もっと読む)

半導体装置の製造方法

【目的】層間絶縁膜内の電荷による電界への影響を緩和して、素子のリーク電流の減少と耐圧の向上を図ることができる半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜をSiH4とN2Oから形成される堆積酸化膜2aとTEOSとO2から形成されるTEOS酸化膜2bとの二層の複合膜とすることで、TEOS酸化膜2b中の電荷5による電界への影響を堆積酸化膜2aで緩和できて、素子のリーク電流が低減され、耐圧が向上する。その結果、良品率を向上させることができる。

(もっと読む)

コンパレータ回路

【課題】出力電圧信号の振幅を十分にとれない場合があった。

【解決手段】本発明は、しきい値電圧を決定する参照電圧を入力する第1、第2の端子と、基準電圧を入力する第3の端子と、前記基準電圧を基準とした、検出すべき電圧を入力する第4の端子と、前記第1、第2の端子を制御端子に接続され、前記参照電圧の電位差に応じた電流をそれぞれ流す、第1導電型の第1、第2のトランジスタと、前記第1のトランジスタと前記第4の端子との間に接続される第2導電型の第3のトランジスタと、前記第2のトランジスタと前記第3の端子との間に接続され、前記第3のトランジスタの流す電流に応じたミラー電流を流す第2導電型の第4のトランジスタと、を有し、前記第2、第4のトランジスタの中間ノードの電圧に応じた電圧を出力信号として出力するコンパレータ回路である。

(もっと読む)

半導体装置、スイッチング装置、及び、半導体装置の制御方法。

【課題】 オン電圧が低いIGBTと、逆回復損失が低いダイオードを有する半導体装置を提供する。

【解決手段】 上面に上部電極が形成されており、下面に下部電極が形成されており、縦型のIGBTと縦型のダイオードが形成されている半導体基板を備える半導体装置。IGBTは、n型のエミッタ領域と、p型のボディ領域と、n型のドリフト領域と、p型のコレクタ領域と、エミッタ領域とドリフト領域を分離している範囲のボディ領域に絶縁膜を介して対向しているゲート電極を有している。ダイオードは、p型のアノード領域と、ドリフト領域と連続しているn型のカソード領域と、カソード領域に絶縁膜を介して対向している制御電極を有している。カソード領域の絶縁膜に接する範囲内には、その周囲のカソード領域よりもn型不純物濃度が高い高濃度領域が形成されている。

(もっと読む)

静電気放電保護装置及び方法

【課題】静電気放電保護装置及び方法を提供する。

【解決手段】本発明の実施例は、静電気放電(ESD)保護装置、及び、ESD保護装置を形成する方法に関する。一実施例は、ESD保護装置で、基板に配置されたpウェルと、基板に配置されたnウェルと、基板中のpウェルとnウェルの間に配置された高電圧nウェル(HVNW)と、pウェルに配置されたソースn+領域と、nウェルに配置された複数のドレインn+領域と、からなる。

(もっと読む)

半導体装置

【課題】高耐圧のノイズやサージから内部回路を守るESD保護素子であり、要求される条件により合わせ込みやすい構造のESD保護素子を提供する。

【解決手段】高耐圧を有する半導体装置をノイズやサージから守るLOCOSオフセット型Nチャネル型MOSを利用したESD保護素子100において、ドレイン側のLOCOS酸化膜-コンタクト間距離14の内側に抵抗領域15を設け、この抵抗領域15の距離を変えることにより、ESD保護素子の動作時における寄生バイポーラトランジスタのオン状態を保持する保持電圧を容易に調整することが可能となる。

(もっと読む)

半導体装置

【課題】電界効果トランジスタの誤動作及び電界効果トランジスタが破壊されることを防ぐことができる。

【解決手段】N型ガードリング18のN−MOSFET20側の第1の部分18Aは、複数のコンタクトメタル32を介して第1の配線メタル36Dと接続されている。N−MOSFET20のゲート領域44は、複数のコンタクトメタル32を介して第1の配線メタル36Iと接続されると共に、複数のコンタクトメタル32及び複数のビア34を介して第2の配線メタル38Cと接続されている。ここで、第1の配線メタル36Dと第2の配線メタル38Cとの間に第2の絶縁層が設けられているので、第1の配線メタル36Dと第2の配線メタル38Cとの間に寄生容量45Aが発生するようにN型ガードリングの第1の部分18AとN−MOSFET20のゲート領域44とが容量結合されている。

(もっと読む)

絶縁ゲート型半導体装置

【課題】絶縁ゲート型半導体装置において、ゲートパッド部の下方に保護ダイオードが配置されるためトランジスタセルが配置できず、チップ上の無効領域となっていた。またソース電極層はゲートパッド部を除いて配置され、素子領域の端部のセルではソースパッド部からゲートパッド部を迂回するように電流経路が形成される領域があった。

【解決手段】電極構造を2層とし、ゲートパッド部と非重畳で保護ダイオードを配置する。ゲートパッド部下方にセルおよび1層目のソース電極層を配置でき、ソース電極層内の抵抗の偏りを小さくできる。更に、保護ダイオードを素子領域と隣接してその外側のチップ端部で且つ、ゲートパッド部と直近に配置する。これにより効率的にトランジスタ動作を行える素子領域を大きく確保でき、且つ配線部下方の第1ソース電極層抵抗を低減できる。

(もっと読む)

半導体装置

【課題】論理回路に向けた製造プロセスで製造できるパワーMOSFET及び論理回路を有する半導体装置を提供する

【解決手段】半導体装置は、パワーMOSと論理回路とを有する。第1領域が第1方向及び第1方向と直交する第2方向に並んで複数個配置され、周囲にガードリング領域が設けられて第2領域が構成され、更に第2領域が第1方向及び第2方向に並んで複数個配置されて第3領域で構成される。第1領域は、第1方向に延長され、第2方向に並んで配置された複数のゲート電極及びソース,ドレインを有する複数のMOSFET及びバックゲート領域及びそれぞれを相互に接続する第1配線層を有する。第3領域において、第2方向に延長されてそれぞれ相互に接続する第1配線層同士を接続する第2配線層、第1方向に延長されて第2配線層同士を接続する第3配線層とが設けられてパワーMOSFETが形成される。

(もっと読む)

半導体装置

【課題】 同一基板上に形成された半導体素子間に流れる寄生電流による半導体素子の誤動作を抑制する構造を有する半導体装置を提供することを目的とする。

【解決手段】

p型半導体基板1に電気的に接続されたn型のコレクタ引き出し層53を備えた小信号素子であるバイポーラトランジスタ50と、p型半導体基板1に電気的に接続されたn型拡散層67を備えたパワートランジスタ素子であるDMOSトランジスタ60と、p型半導体基板1に電気的に接続され、かつ、ダミー電極13に接続されたn型のダミーN島10と、p型半導体基板1に電気的に接続され、かつ、フィールド電極23に接続されたp型のフィールド部20と、ダミー電極13とフィールド電極23を接続し、ボンディングパット70に接続する配線30とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラー型SGTを複数並列に接続する際に、配線層を設ける必要のない半導体装置を提供する。

【解決手段】3Dピラー型SGTの上部主電極領域が選択エピタキシャル成長半導体層を含み、少なくとも2つの隣接する3Dピラー型SGTを、各々の選択エピタキシャル成長半導体層を接触させて並列接続する。

(もっと読む)

BiCDMOS構造及びその製造方法

【課題】DMOS電力回路、CMOSデジタル論理回路、及びコンプリメンタリバイポーラアナログ回路の全てを単一の集積化された回路チップ上に実現するBiCDMOS構造及びその製造方法を提供する。

【解決手段】基層10内に下向きに延出し、且つ基層の上に配置されたエピタキシャル層40内に上向きに延出し、かつエピタキシャル層の上側主面の下に配置された埋め込み絶縁領域21Bと、エピタキシャル層内のみに配置され、かつ埋め込み絶縁領域の上側主面から上向きに延出した埋め込みウェル領域44Bと、エピタキシャル層内に配置され、かつエピタキシャル層の上側主面からエピタキシャル層内に下向きに延出し、かつ埋め込みウェル領域の上側主面に接触する下側主面を備えたウェル領域51Bとを有し、バイポーラトランジスタがウェル領域内に形成され、MOSトランジスタがウェル領域外のエピタキシャル層の上側主面に形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧で、基板への電流の漏れが抑制され、かつ、端子に負入力があった場合でも基板から端子への電流の抜けが抑制されたダイオードを基板上に有する半導体装置およびその製造方法を提供すること。

【解決手段】P型基板1と、P型基板1上に順次形成されたN型埋め込み層2、P型埋め込み層3、およびN型エピタキシャル層4と、P型埋め込み層3上に形成されN型エピタキシャル層4を囲むP型拡散層6と、ゲート領域を構成するP型拡散層8およびP型拡散層11と、ソース領域を構成するN型拡散層9、P型拡散層12およびN型拡散層13と、N型エピタキシャル層4の上方に形成されP型拡散層12およびN型拡散層13と短絡したゲート電極と、を備え、N型埋め込み層2はフローティング状態にある。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜を表面研磨する工程を経て形成される半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1の主面s1上に、高耐圧ゲート絶縁膜IG1および高耐圧ゲート電極EG1からなる高耐圧ゲートG1を形成した後、サリサイドブロック膜SAB、層間絶縁膜ILを順に形成し、その層間絶縁膜ILをCMPにより研磨する。サリサイドブロック膜SABは、下層から順に酸化シリコンを主体とする絶縁膜である保護酸化膜t1と、窒化シリコンを主体とする絶縁膜である保護窒化膜t2とによって形成する。また、層間絶縁膜ILの研磨は、高耐圧ゲートG1上面のサリサイドブロック膜SABに達するまで研磨する。

(もっと読む)

半導体装置ならびにそれを用いた電力変換装置

【課題】電力変換用の半導体絶縁ゲート型スイッチング素子の駆動回路の出力段の素子の電流駆動能力を高め小型化することで、駆動回路を集積化したより小型で高性能な駆動回路と、さらにこれを用いることでより小型で高性能な電力変換装置を提供する。

【解決手段】絶遠ゲート型の主半導体スイッチング素子のオン、オフを制御する駆動回路において、前記主半導体スイッチング素子のゲート電圧を制御する回路の出力段に絶縁ゲート制御型のバイポーラ半導体素子、特に、IGBTを用いる。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する、シリサイド化される金属を含有する複数の電気素子要素と、複数の電気素子要素を覆い、電気素子要素に含まれる金属が実質的にシリサイド化しない温度で薄膜形成したシリコンを含む保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、保護絶縁膜は、シリコンおよび窒素を含有できる。保護絶縁膜は、260℃以下の温度で薄膜形成した窒化シリコン膜であってよく、好ましくは100℃以下の温度で薄膜形成した窒化シリコン膜である。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する複数の電気素子要素と、複数の電気素子要素を覆う、シリコンを含まない下層保護絶縁膜と、下層保護絶縁膜の上に配置され、シリコンを含む上層保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、複数の電気素子要素の少なくとも一つは、シリサイド化される金属を含有でき、下層保護絶縁膜は、電気素子要素に含有される金属と上層保護絶縁膜に含有されるシリコンとの接触を阻害できる。下層保護絶縁膜は、比誘電率が10以上の高誘電体層を有してよい。上層保護絶縁膜は、シリコンおよび窒素を含有することができる。

(もっと読む)

121 - 140 / 356

[ Back to top ]