Fターム[5F048BC02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 形状 (1,394) | 分割ドレイン(ソース) (356)

Fターム[5F048BC02]に分類される特許

61 - 80 / 356

半導体装置

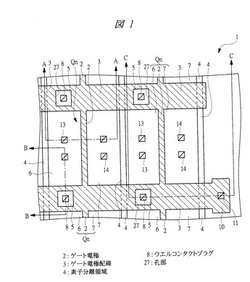

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

半導体装置

【課題】高融点金属を含む多層配線を使用してトランジスタに導入される配線がトランジスタのチャネル幅方向と垂直の方向から導入される場合においても、ESD保護用のMOSトランジスタの全体で均一に動作させることのできる半導体装置を得る。

【解決手段】複数のドレイン領域と複数のソース領域が交互に配置され、前記ドレイン領域と前記ソース領域の間にゲート電極が配置された、複数のトランジスタが一体化した構造を有するESD保護用のMOSトランジスタにおいて、ドレイン領域上に形成されるサリサイド金属領域とゲート電極との距離を、ドレイン領域上のコンタクトと基板コンタクトからの距離に応じて形成した。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、従来の製造方法と比較し、同一ウエハまたは製品上において複数のデバイス耐圧帯と良好なオン抵抗をもったLDMOSを備えた半導体装置およびその製造方法を提供することを目的とするものである。

【解決手段】 第1電界緩和用酸化膜24と第2電界緩和用酸化膜25と素子分離用LOCOS酸化膜17の膜厚を別々に最適化することにより、同一ウエハにおいて複数のデバイス耐圧と良好なオン抵抗を実現する。

(もっと読む)

DC/DCコンバータ用半導体装置

【課題】半導体装置の電源電圧の変換効率を向上させる。

【解決手段】ハイサイドスイッチ用のパワーMOS・FETとローサイドスイッチ用のパワーMOS・FETとが直列に接続された回路を有する非絶縁型DC−DCコンバータにおいて、ローサイドスイッチ用のパワーMOS・FETと、そのローサイドスイッチ用のパワーMOS・FETに並列に接続されるショットキーバリアダイオードD1とを同一の半導体チップ5b内に形成した。ショットキーバリアダイオードD1の形成領域SDRを半導体チップ5bの短方向の中央に配置し、その両側にローサイドのパワーMOS・FETの形成領域を配置した。また、半導体チップ5bの主面の両長辺近傍のゲートフィンガ6aから中央のショットキーバリアダイオードD1の形成領域SDRに向かって、その形成領域SDRを挟み込むように複数本のゲートフィンガ6bを延在配置した。

(もっと読む)

半導体装置

【課題】絶縁ゲート型電界効果トランジスタのスイッチング速度低下を防止し、省スペース化を実現する半導体装置を提供する。

【解決手段】本発明に係る半導体装置90は、絶縁ゲート型電界効果トランジスタとコンデンサが同一チップ上に形成されたものであって、表層において、n−型エピタキシャル層2を挟持するp型ボディ領域5内にそれぞれ配設されたn+型ソース領域6の当該n−型エピタキシャル層2に最近接する端部間に亘る領域上に配設された絶縁層7と、絶縁層7を介してn−型エピタキシャル層2と対向されるコンデンサ上部電極40と、絶縁層7上でコンデンサ上部電極40の両サイドに絶縁分離されるように、かつチャネル形成可能な位置に配設されたゲート電極31を備える。コンデンサC1は、コンデンサ上部電極40を上部電極とし、これと絶縁層7を介して対向配置されるn−型エピタキシャル層2を下部電極とする。

(もっと読む)

半導体装置およびDC−DCコンバータ

【課題】半導体装置の耐圧を向上させ、より高速のスイッチング動作を可能にする。

【解決手段】第1導電型の半導体層の第1主面側に選択的に設けられた第2導電型のベース領域と、ベース領域内に選択的に設けられた第1導電型の拡散領域と、拡散領域に接触しベース領域を貫通して半導体層にまで到達するトレンチ内に絶縁膜を介して設けられた制御電極と、半導体層の第1主面側から第2主面側の方向に延伸し、ベース領域とは離間して設けられた、少なくとも1つの第2導電型の第1の半導体領域と、隣り合うトレンチ間に、トレンチとは離間して設けられた第2導電型の第2の半導体領域と、拡散領域、半導体層、第1の半導体領域および第2の半導体領域に電気的に接続された第1の主電極と、半導体層の第2主面側に電気的に接続された第2の主電極と、を備え、第2の半導体領域は、ベース領域を貫通して半導体層にまで到達している。

(もっと読む)

半導体装置

【課題】半導体装置の小型化を図ることを課題とする。

【解決手段】炭化珪素基体1と、炭化珪素基体1上に形成された第1導電型のドリフト領域2と、ドリフト領域2の主面に接するようにドリフト領域2内に形成された第2導電型のウェル領域3と、ドリフト領域2の主面に接するようにウェル領域3内に形成された第1導電型のソース領域4と、ドリフト領域2とソース領域4に挟まれたウェル領域3上にゲート絶縁膜5を介して形成されたゲート電極6と、ウェル領域3とソース領域4に接続されたソース電極7と、炭化珪素基体1に接続されたドレイン電極9とを備えたトランジスタと、ドリフト領域2に形成された第2導電型の拡散領域10からなるアノードと、第2導電型の拡散領域10内に形成された第1導電型の拡散領域11からなるカソードとを備え、カソードはゲート電極6に接続されて構成されたダイオード12とを有することを特徴とする。

(もっと読む)

絶縁ゲート型半導体装置

【課題】低オン電圧と低スイッチング損失とを両立することができる絶縁ゲート型半導体装置を提供する。

【解決手段】間引き型のIGBT素子において、ダミーセルのP型のフロート層18にN型のホールストッパー層19を設ける。また、このホールストッパー層19により分割された第1の層18aをエミッタ電極21に接地する。これにより、コレクタ電極24からフロート層18を介してゲート電極17に到達する経路に形成される帰還容量の中に溜まる電荷はほとんど無くなるため、スイッチング損失を低減できる。さらに、P型のフロート層18に設けられたN型のホールストッパー層19が電位の壁となるので、半導体基板10からフロート層18を介してエミッタ電極21にホールが抜けてしまうことを抑制することができる。このため、半導体基板10の抵抗が下がり、IGBT素子のオン電圧を下げることができる。

(もっと読む)

半導体装置

【課題】電子回路の小型化を実現する。

【解決手段】MOSトランジスタ20が、格子状に形成されたゲート電極22と、ゲート電極22で囲まれたソース領域23およびドレイン領域24と、ゲート電極22の格子の一方向に沿って配置され、ソース領域23およびドレイン領域24とコンタクトを介して接続するソース用メタル配線27およびドレイン用メタル配線28を有する。ソース領域23およびドレイン領域24のそれぞれは、各メタル配線の長さ方向に長辺を有する長方形状に形成される。ソース用メタル配線27およびドレイン用メタル配線28は、その長さ方向にジグザグ形状に形成されて、それぞれソース用コンタクト25およびドレイン用コンタクト26に接続する。

(もっと読む)

トレンチ型絶縁ゲート半導体装置及びその製造方法

【課題】トレンチ型絶縁ゲート半導体素子と多結晶シリコンダイオードを同一チップ上に形成して性能を高める。

【解決手段】本発明では、半導体基板上の半導体層の主面に形成されたトレンチ型絶縁ゲート半導体素子のトレンチ溝の外側には、トレンチ溝に連なる多結晶シリコン層を形成する。また、トレンチ溝の外側には、前記トレンチ溝に連なる多結晶シリコン層とは別の多結晶シリコン層が形成され、この多結晶シリコン層には多結晶シリコンダイオードが形成され、そして、この多結晶シリコンダイオードが形成された多結晶シリコン層の膜厚が、前記トレンチ溝に連なる多結晶シリコン層の膜厚よりも薄くなるように形成することを特徴とする。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

電界効果型トランジスタ

【課題】電流許容値の低下を抑制する。

【解決手段】Y方向に沿って延在する延在ゲート電極G11と、Y方向に沿って延在するダミーゲート電極DM1と、Y方向に沿って延在する延在ソース電極S11と、Y方向に沿って延在する延在ドレイン電極D11とを含む。延在ソース電極G11は、X方向においてダミーゲート電極DM1を覆う形状を有する。また、延在ドレイン電極G11は、X方向においてダミーゲート電極DM1を覆う形状を有する。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路(1000)が、中央配置のドレイン拡散領域(1008)及び分散型SCR端子(1010)を備える1つのドレイン構造(1006)と、分散型ドレイン拡散領域(1016)及びSCR端子(1018)を備える別のドレイン構造(1012)とを含むSCRMOSトランジスタを有する。中央配置のドレイン拡散領域とソース拡散領域との間のMOSゲート(1022)がソース拡散領域へ短絡される。SCRMOSトランジスタを有する集積回路を形成するためのプロセスも開示される。  (もっと読む)

(もっと読む)

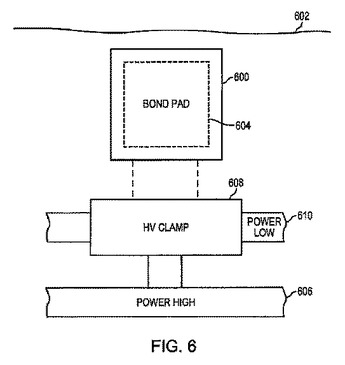

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

パワー・スイッチの構造および方法

【課題】低RDSonおよび低電流制限の両方を提供する一方で、ホット・スポットおよび熱暴走の効果を低減する回路を提供する。

【解決手段】本発明の一実施例において、パワー・スイッチング・デバイス(33)は、第1MOSFETデバイス(41)および第2MOSFETデバイス(42)を含む。第1ゲート電極(48,87)を含む分割ゲート構造(84)は、第1MOSFETデバイス(41)を制御する。第2ゲート電極(49,92)は、第2MOSFETデバイス(42)を制御する。電流制限デバイス(38)は、第1ゲート電極(48,97)に結合され、電流制限モード中に第1MOSFETデバイスをオンにする。比較器デバイス(36)は、第2ゲート電極(49,92)に結合され、パワー・スイッチング・デバイス(33)が電流制限モードでなくなったときに、第2MOSFETデバイス(42)をオンにする。

(もっと読む)

半導体装置の製造方法

【課題】 半導体基板等を損傷することなく、結晶欠陥形成のために行われるイオン等の照射において用いる放射線遮蔽マスクを除去する。

【解決手段】 半導体装置の製造方法は、半導体を材料とする素子形成層と、素子形成層の下面側に設けられ、開口部を有するマスク層と、素子形成層とマスク層の間に設けられ、素子形成層およびマスク層と異なる材料によって形成されている境界層と、を有する材料ウェハを準備する材料ウェハ準備工程と、マスク層の下面側から、荷電粒子の照射を行って、素子形成層に結晶欠陥を形成する結晶欠陥形成工程と、境界層と反応し、かつ、素子形成層と反応しないエッチング材を用いて、境界層をエッチングによって除去するマスク層除去工程とを含む。半導体基板等を損傷することなく、結晶欠陥形成のために行われる荷電粒子の照射において用いる遮蔽マスクを除去することが可能となる。

(もっと読む)

マルチフィン高さを有するFinFET

【課題】マルチフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、半導体基板と、半導体基板上のFinFETと、を含む。FinFETは、半導体フィンと、半導体フィンの頂面および側壁上のゲート誘電体と、ゲート誘電体上のゲート電極と、半導体フィン一端に位置するソース/ドレイン領域と、を備える。一対の第一STI領域は、ソース/ドレイン領域の一部分の真下に位置する部分を含み、一対の第一STI領域は、半導体ストリップにより分離され、且つ、半導体ストリップに隣接する。一対の第一STI領域は、更に、第一頂面を有する。一対の第二STI領域は、ゲート電極の真下に位置する部分を含み、一対の第二STI領域は、半導体ストリップにより互いに分離され、且つ、半導体ストリップに隣接する。第二STI領域は、第一頂面より高い第二頂面を有する。

(もっと読む)

トレンチ型パワーMOSトランジスタおよびその製造方法

【課題】パワーMOSトランジスタにおいて、高い降伏電圧、高い出力電流および高速の動作速度を備えるのみならず、水平構造を備えるために、CMOSの製造工程で製作された一般的な集積回路と同一のチップ上に整合させる。

【解決手段】本発明のトレンチ型パワーMOSトランジスタはゲート導電体312と、絶縁層310とを備えたトレンチ型ゲート領域を具備する。絶縁層310は、ゲート導電体312と井戸領域308との間で薄い側壁領域を形成しており、ゲート導電体312と二重拡散のドーピング領域306との間で厚い側壁領域を形成するとともに、ゲート導電体312と深井戸領域304との間で厚い最下部領域を形成している。

(もっと読む)

集積回路構造、及び集積回路の製造方法

【課題】異なるフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、第1装置領域の第1部分と、第2装置領域の第2部分と、を有する半導体基板からなる。第1半導体フィンは半導体基板上にあり、第1フィン高さを有する。第2半導体フィンは半導体基板上にあり、第2フィン高さを有する。第1フィン高さは第2フィン高さより高い。

(もっと読む)

半導体装置

【課題】三次元半導体であるsurrounding gate transistor(SGT)のオン電流を増加させることにより、SGTの高速動作を実現する半導体装置を提供することを課題とする。

【解決手段】ソース、ドレイン及びゲートが、基板上に階層的に配置される半導体素子であって、シリコン柱と、前記シリコン柱の側面を取り囲む絶縁体と、前記絶縁体を囲むゲートと、前記シリコン柱の上部又は下部に配置されるソース領域と、前記シリコン柱の上部又は下部に配置されるドレイン領域であって、前記シリコン柱に対して前記ソース領域と反対側に配置されるドレイン領域とを備え、前記シリコン柱と前記ソース領域との接触面は、前記シリコン柱と前記ドレイン領域との接触面より小さい半導体素子を提供することにより上記課題を解決する。

(もっと読む)

61 - 80 / 356

[ Back to top ]