Fターム[5F048BC02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 形状 (1,394) | 分割ドレイン(ソース) (356)

Fターム[5F048BC02]に分類される特許

21 - 40 / 356

半導体装置

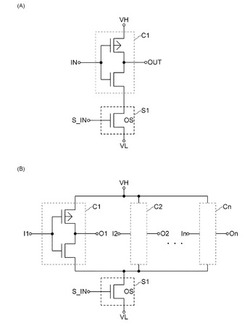

【課題】待機電力を十分に低減した新たな半導体装置を提供することを目的の一とする。

【解決手段】第1の電源端子と、第2の電源端子と、酸化物半導体材料を用いたスイッチ

ングトランジスタと、集積回路と、を有し、前記第1の電源端子と、前記スイッチングト

ランジスタのソース端子またはドレイン端子の一方は電気的に接続し、前記スイッチング

トランジスタのソース端子またはドレイン端子の他方と、前記集積回路の端子の一は電気

的に接続し、前記集積回路の端子の他の一と、前記第2の電源端子は電気的に接続した半

導体装置である。

(もっと読む)

半導体デバイスのための非対称スペーサ構造体を形成する方法

【課題】 デバイスのゲートとソースとの間の低い直列抵抗を維持し、同時に、ゲートからドレインへの過剰なオーバーラップによって形成される悪影響を最小限にするFETデバイスの製造を可能にする。

【解決手段】半導体基板の上に少なくとも1対の隣接して離間配置された、オフセット・スペーサ114を備えるゲート構造体102の上にスペーサ層132を形成するステップであって、ゲート構造体は、スペーサ層がゲート構造体間の領域で第1の厚さで形成され、その他の場所で第2の厚さで形成されるように離間配置され、第2の厚さは第1の厚さより厚い、ステップと、1対の隣接して離間配置されたゲート構造体のオフセット・スペーサに隣接して非対称スペーサ構造体124a、bを形成するようにスペーサ層をエッチングするステップとを含み、非対称スペーサ構造体は、ソース及びドレイン領域の画定において用いられる。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 基板表面にパターンニングされたポリシリコン層(ゲート配線や保護ダイオード)が閉ループ状の場合、特にウエハの周辺部分に配置されるチップでは、層間絶縁膜形成時にSOG膜のスピンコートでチップコーナー部分などにおいてSOG液の液だまりが生じ、層間絶縁膜の膜厚が不均一となり、厚膜化した箇所ではコンタクトホールの形成不良が発生する問題があった。

【解決手段】 ゲート配線と保護ダイオードが連続した閉ループ状とならないように、ゲート配線のコーナー部と、ゲート配線および保護ダイオードの隣接部分に開放部を設ける。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 MOSFETの素子領域の外側の周辺領域において、ドレイン‐ソース間にpn接合ダイオードを形成し、逆起電力による電流の経路を確保してアバランシェ破壊を防止している。しかし、チップサイズの小型化や素子領域の面積の拡大を目的として周辺領域の面積を縮小した場合、pn接合ダイオードの配置領域が縮小し、電流経路が少なくなるためアバランシェ破壊に弱くなる問題があった。

【解決手段】 ゲート引き出し配線8で区画される周辺ゲート領域25において、p+型不純物領域24とソース電極17を接続する第2コンタクト部10の単位面積当たりの合計面積を、素子領域20のソース領域15とソース電極17とを接続する第1コンタクト部9の単位面積当たりの合計面積より大きくする。周辺領域の面積を縮小した場合であっても逆起電力による電流の経路を確保できアバランシェ耐量の劣化を防げる。

(もっと読む)

半導体装置

【課題】半導体装置の定格温度(−50℃〜+150℃)において高精度の温度検出を行うことのできる半導体装置を提供すること。

【解決手段】n型基板1の第1主面に、p型ベース領域3と該ベース領域3表面層のn型エミッタ領域4と、前記基板1からなるn型ドリフト層1表面と前記エミッタ領域4表面とに挟まれるp型ベース領域3表面上にゲート酸化膜7を介して設けられるゲート電極8と、前記エミッタ領域4表面と前記ベース領域3表面に共通に接触するエミッタ電極6と、第2主面のp型コレクタ層2とを有するIGBTと、該IGBTに離間して第1主面に形成されるn型ウェル領域15表面層にn型カソード領域11とp型アノード領域12を有する温度センサダイオードを備え、前記n型ウェル領域15がp型ウェル領域16の表面層に形成され、前記温度センサダイオードのライフタイムが1μs以下に設定されている半導体装置とする。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、半導体素子、特にパワー半導体素子を提供する。

【解決手段】半導体基材100と、上記半導体基材100内の、半導体材料からなるドリフト領域2と、ドリフト領域2に対し、少なくとも部分的に隣り合って配置され、接続電極19を含む、半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3との間に配置された蓄積誘電体4と、第1素子領域8と、第1素子領域8との間にドリフト領域2が配置され、第1素子領域8から離れて配置された第2素子領域5と、ドリフト制御領域3の接続電極19および第1素子領域8の間に接続された容量性素子50とを含む。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体装置の製造方法

【課題】信頼性と電気的特性の確保を両立した半導体装置を提供する。

【解決手段】同一の半導体基板1上に形成されたパワーMOSFETと保護回路を備える。パワーMOSFETがトレンチゲート縦型PチャネルMOSFETであって、そのゲート電極6の導電型をP型とする。また、保護回路がプレーナゲート横型オフセットPチャネルMOSFETを備え、そのゲート電極10の導電型をN型とする。これらゲート電極6とゲート電極10は別工程で形成される。

(もっと読む)

シンクロナス整流器或いは電圧クランプ用の3端子パワーMOSFETスイッチ

【課題】パワー変換器に於けるシンクロナス整流器として適するMOSFETスイッチを提供する。

【解決手段】互いに接続されソース及びボディが、ドレンよりはより正の側に高い電圧にバイアスされたN−チャネルパワーMOSFETを製造する。ゲートはスイッチ(1184)により制御され、ゲートを、ソース及び当該MOSFETのチャネルを完全にオンにするのに十分な電圧(VCP)のいずれか一方に選択的に接続する。ゲートがソースに接続されたとき、デバイスは、比較的低い電圧でオンし、従来のPN接合よりは低い導通抵抗を有する「擬似ショットキー」ダイオードとして機能する。ゲートが、前記した正の電圧に接続されたとき、MOSFETのチャネルは完全にオンとなる。このMOSFETスイッチは、電力損及び“break-before-make”時間に於ける蓄積電荷を低減する。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数を削減して生産性を向上できる構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体層1にトレンチ20を形成する工程と、トレンチ2の内壁およびトレンチ2外の表面を覆うように半導体層1上に絶縁膜3を形成する工程と、トレンチ2を埋め尽くし、トレンチ2外の絶縁膜3上に堆積されるように導電性のポリシリコン膜4を形成する工程と、トレンチ2内、およびトレンチ2外の絶縁膜3上の所定領域にポリシリコン膜4が残るように、当該ポリシリコン膜4を選択的に除去するポリシリコンエッチング工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、セルの有効面積を増やし、アンバランス動作等を抑制可能な半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、第1層間絶縁膜8に覆われない上面を介して、ゲート電極20と接続された、第1ゲート配線5と、第1ゲート配線5の、上面の一部を除く領域を覆って、第1層間絶縁膜8上に形成された、第2層間絶縁膜80と、第2層間絶縁膜80に覆われない上面を介して、第1ゲート配線5と接続された、第2ゲート配線16とを備え、平面視において、第2ゲート配線16の幅は、第1ゲート配線5の幅よりも広い。

(もっと読む)

半導体装置

【課題】低オン抵抗且つ高アバランシェ耐量の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第2導電型の第1のソースコンタクト領域21と第1導電型のバックゲートコンタクト領域22とを有する第1のソース部S1と、第2導電型の第2のソースコンタクト領域24を有し、第1導電型のバックゲートコンタクト領域を有さない第2のソース部S2と、第2導電型のドレインコンタクト領域15と、第1のソースコンタクト領域21側に形成された第2導電型の第1のドリフト領域16と、第2のソースコンタクト領域24側に形成された第2導電型の第2のドリフト領域17とを有するドレイン部Dと、を備え、第2のドリフト領域17の方が第1のドリフト領域16よりもチャネル長方向の長さが長い。

(もっと読む)

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

半導体装置

【課題】特性をさらに向上する半導体装置を提供する。

【解決手段】高電圧側電界効果トランジスタ20aの高電圧側ドレイン電極11aと、高電圧側ドレイン電極11aの一側方に間隔をおいて形成される高電圧側ゲート電極12aと、高電圧側ゲート電極12aの一側方に間隔をおいて形成され、高電圧側電界効果トランジスタ20aのソース電極であり、低電圧側電界効果トランジスタ21aのドレイン電極であるソース兼ドレイン電極13aと、ソース兼ドレイン電極13aの一側方に間隔をおいて形成される低電圧側電界効果トランジスタ21aの低電圧側ゲート電極14aと、低電圧側ゲート電極14aの一側方に間隔をおいて形成される低電圧側電界効果トランジスタ21aの低電圧側ソース電極15aとを有する。

(もっと読む)

半導体装置および携帯電話機

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】RXスルートランジスタ群TH(RX)は、互いに直列に接続されたMISFETQ1〜Q5において、それぞれのMISFETのボディ領域と、隣接するMISFETのソース領域あるいはドレイン領域とを、それぞれ、ダイオード(整流素子)を介して接続する。そして、特に、nチャネル型MISFETの場合、MISFETのボディ領域から隣接するMISFETのソース領域あるいはドレイン領域へ向う向きが順方向となるようにダイオードを接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域をライン上に形成することで、コンタクト領域のばらつきを抑制し、リセスゲート電極を用いて隣接するトランジスタ間の分離を行う構造を提供する。

【解決手段】半導体基板中に第1の方向に延在して形成される素子分離領域で分離された活性領域と、第1の方向と交差する第2の方向に延在し、素子分離領域及び活性領域に連通する溝内に形成されたリセスゲート電極と。リセスゲート電極で分断された活性領域であって、リセスゲート電極の底面より浅い領域に形成されるMOSトランジスタのソース/ドレイン領域とを備えた半導体装置であって、リセスゲート電極は、MOSトランジスタのゲート電極を構成する制御ゲート電極162tと、第1の方向に隣接するMOSトランジスタを素子分離する補助ゲート電極162iで構成される。

(もっと読む)

半導体素子

【課題】ゲート閾値の変動を抑制または防止できる半導体素子を提供する。

【解決手段】半導体素子1は、n型エピタキシャル層8と、n型エピタキシャル層8の表層部に形成されたボディ領域12と、ボディ領域12の表層部に形成されたn型ソース領域16と、n型エピタキシャル層8上に形成されたゲート絶縁膜19と、ゲート絶縁膜19上に形成されたゲート電極20およびゲート保護ダイオード30とを含む。ゲート保護ダイオード30は、第1のp型領域31とn型領域32と第2のp型領域33とを含む。第1のp型領域31とn型領域32によって第1のダイオード30Aが構成されている。n型領域32と第2のp型領域33によって第2のダイオード30Bが構成されている。第1のp型領域31はゲート電極20に接続されている。第2のp型領域33はソース電極27を介してソース電極27に接続されている。

(もっと読む)

電力増幅器

【課題】 電力増幅器に発生するホットキャリアの影響を抑制する。

【解決手段】 一つの実施形態の電力増幅器には、半導体層に形成され、少なくとも1つ以上から構成され、電力増幅動作する第1のグロースリングゲート構造体と、半導体層に形成され、第1のグロースリングゲート構造体を取り囲むように隣接配置され、第1の構造体が電力増幅動作するときに、逆バイアスが印加されて空乏化領域が形成され、第1の構造体を周囲からアイソレートする複数の第2のグロースリングゲート構造体とが設けられる。

(もっと読む)

21 - 40 / 356

[ Back to top ]