Fターム[5F048BF11]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | 多層配線(2層) (1,460)

Fターム[5F048BF11]の下位に属するFターム

3層以上配線 (358)

Fターム[5F048BF11]に分類される特許

161 - 180 / 1,102

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

半導体装置

【課題】貫通電流を低減させることができる相補型の論理回路を用いることで、消費電力を抑えることができる半導体装置の提案を目的の一とする。或いは、貫通電流を低減させることができる相補型の論理回路を用いることで、発熱を抑えることができる半導体装置の提案を目的の一とする。

【解決手段】通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられたnチャネル型トランジスタ、或いはpチャネル型トランジスタを、相補型の論理回路に用いる。そして、オフ電流が極めて小さい絶縁ゲート電界効果型トランジスタをスイッチング素子として用い、上記第2のゲート電極の電位を制御する。上記スイッチング素子として機能するトランジスタは、シリコン半導体よりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料を、チャネル形成領域に含む。

(もっと読む)

双方向素子および半導体装置

【課題】高耐圧でオン電圧を低くできる双方向素子および半導体装置を提供すること。

【解決手段】分割半導体領域にpオフセット領域5とその表面に第1、第2nソース領域9、10を形成することで、第1、第2nソース領域9、10の平面距離を短縮してセルの高密度化を図り、トレンチに沿って耐圧を維持させることで高耐圧化を図り、ゲート電極7の電圧を第1、第2nソース電極11、12より高くすることで、トレンチ側壁にチャネルを形成して、双方向へ電流が流れる高耐圧で低オン電圧の双方向LMOSFETとすることができる。

(もっと読む)

半導体装置とその製造方法

【課題】良好な特性を有し且つ微細化を実現した半導体装置とその製造方法を提供する。

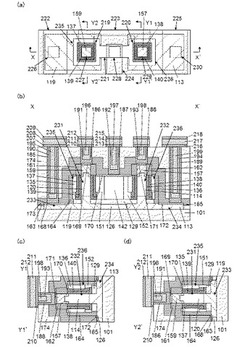

【解決手段】半導体装置は、平面状シリコン層212上の柱状シリコン層208、柱状シリコン層208の底部領域に形成された第1のn+型シリコン層113、柱状シリコン層208の上部領域に形成された第2のn+型シリコン層144、第1及び第2のn+型シリコン層113,144の間のチャネル領域の周囲に形成されたゲート絶縁膜140、ゲート絶縁膜140の周囲に形成され第1の金属シリコン化合物層159aを有するゲート電極210、ゲート電極210と平面状シリコン層212の間に形成された絶縁膜129a、柱状シリコン層208の上部側壁に形成された絶縁膜サイドウォール223、平面状シリコン層212に形成された第2の金属シリコン化合物層160、及び第2のn+型シリコン層144上に形成されたコンタクト216を備える。

(もっと読む)

交流スイッチ

【課題】高耐圧の用途に適用可能な交流スイッチ(半導体リレー)を提供する。

【解決手段】交流スイッチ1は、ソース(S)同士を接続した第1化合物半導体MOSFET11および第2化合物半導体MOSFET12と、第1化合物半導体MOSFET11のドレイン(D)に接続された第1出力端子13と、第2化合物半導体MOSFET12のドレイン(D)に接続された第2出力端子14とを含む。交流スイッチ1は、オフ時の第1出力端子13および第2出力端子14の間の耐圧が400V以上(より好ましくは600V以上)であり、オン時の第1出力端子13および第2出力端子14の間の抵抗が20mΩ以下(より好ましくは10mΩ以下)である。

(もっと読む)

半導体装置の製造方法

【課題】高電圧仕様の受動素子と低電圧仕様の容量素子とを備える半導体装置の製造方法であって、低電圧仕様の容量素子の容量を確保できると共に、高電圧仕様の受動素子の当該高電圧仕様に対する耐圧を確保すると共に、製造時に高電圧仕様の受動素子の特性が変動することを防止できる半導体装置の製造方法を提供する。

【解決手段】半導体基板102上に絶縁膜116bを上部に有する下部電極110bと絶縁膜116aを上部に有する下部電極110aとを形成し、下部電極110b上の絶縁膜116bの膜厚を薄くし、半導体基板102上にゲート電極144を形成し、膜厚を薄くした第1の絶縁膜116b上に上部電極140を形成し、ゲート電極144および上部電極140を形成した後、全面に絶縁膜を形成し、絶縁膜を異方性エッチングしてゲート電極144の側面にサイドウォール148を形成する。

(もっと読む)

SOI基板の作製方法

【課題】エアボイドなどの貼り合わせに起因する欠陥を十分に抑制できるSOI基板の作製方法を提案することを目的の一とする。

【解決手段】ボンド基板とベース基板を対向させ、ボンド基板またはベース基板の端部に圧力をかけてボンド基板とベース基板の貼り合わせを開始させる時、または前に、ボンド基板表面、または、ベース基板表面の貼り合わせの開始地点における接平面に対して、ボンド基板における貼り合わせの終了地点がベース基板から離れるようにボンド基板を反らせ、および/または、ベース基板における貼り合わせの終了地点がボンド基板から離れるようにベース基板を反らせ、貼り合わせを開始させた後に、ボンド基板の反り量、および/または、ベース基板の反り量を制御することにより、ボンド基板とベース基板の貼り合わせに係る速度を制御する、SOI基板の作製方法である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

半導体基板の保持用トレイ、並びに半導体基板および半導体装置の作製方法

【課題】複数枚の絶縁層被覆単結晶半導体基板に対して効率よくイオン注入を行い、大面積の単結晶半導体層を備えた半導体基板の作製方法を提供することを課題の一とする。

【解決手段】半導体基板の作製工程において、表面のファンデルワールス力を調整した保持用トレイに表面に絶縁層が形成された複数枚の単結晶半導体基板を貼り合わせ、複数枚の単結晶半導体基板にイオン照射工程を行うことで複数枚の単結晶半導体基板の所定の深さに脆化層を形成し、複数枚の単結晶半導体基板にファンデルワールス力を調整したベース基板を貼り合わせることでファンデルワールス力の差を利用して保持用トレイを選択的に分離し、剥離加熱処理を行い劈開面を形成して単結晶半導体基板をベース基板から分離することにより、絶縁層を介して単結晶半導体基板をベース基板に転載する。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置の作製工程数を減少させること、半導体装置の歩留まりを向上させること、半導体装置の作製コストを低減することを課題とする。

【解決手段】基板上に、単結晶半導体層をチャネル形成領域に有する第1のトランジスタと、当該第1のトランジスタと絶縁層を介して分離され、酸化物半導体層をチャネル形成領域に有する第2のトランジスタと、当該単結晶半導体層及び酸化物半導体層を有するダイオードを有する半導体装置、及び、その作製方法に関する。

(もっと読む)

半導体薄膜基板および半導体薄膜基板を用いた半導体装置の作製方法

【課題】一層の半導体層から膜厚の異なる半導体層を有する半導体薄膜基板を提供することを目的の一とする。または、半導体薄膜基板を適用した半導体装置を提供することを目的の一とする。

【解決手段】基板上に半導体層を形成し、半導体層を加工して第1の島状半導体層および第2の島状半導体層を形成し、第1の島状半導体層にレーザー照射を行うことにより第1の島状半導体層を溶融させ、第1の島状半導体層から第2の島状半導体層より膜厚が厚い第3の島状半導体層を形成する、半導体薄膜基板の作製方法である。

(もっと読む)

半導体素子、及びその形成方法

【課題】 信頼性が向上する半導体素子、及びその形成方法を提供する。

【解決手段】 半導体素子の形成方法は、半導体基板100の上にゲート電極120及びゲート電極120の両側にスペーサー110を形成する段階、ゲート電極120の上にキャッピングパターン170を形成する段階、ゲート電極120の間にメタルコンタクト195を形成する段階を含み、キャッピングパターン170の幅はゲート電極120の幅より大きく形成される。これにより、形成された半導体素子は、メタルコンタクト195とゲート電極120との間での電気的な短絡を效果的に防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの特性を劣化させることなくポリシリコン抵抗素子を製造できる半導体装置の製造方法を提供する。

【解決手段】半導体基板30の抵抗素子形成領域に抵抗素子となるポリシリコン膜35aを形成するとともに、トランジスタ形成領域にポリシリコンゲート35b及び高濃度不純物領域40を形成する。その後、全面に絶縁膜41を形成した後、トランジスタ形成領域をフォトレジスト膜42で覆い、ポリシリコン膜35aに導電性不純物をイオン注入する。次いで、フォトレジスト膜42をアッシングにより除去する。このとき、トランジスタは絶縁膜41に覆われているため、アッシングによるダメージが回避される。また、抵抗素子領域に導入された導電性不純物が大気中のO及びHと反応して酸が発生しても、ポリシリコンゲート及び高濃度不純物領域40が酸により溶解することが回避される。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】結晶欠陥の発生を抑制しながら、深い素子分離膜を形成する。

【解決手段】半導体装置100は、基板(半導体基板1)と、基板に形成され、素子形成領域4を他の領域と分離する素子分離膜2と、素子形成領域4にて基板上に形成された半導体層3と、を有する。素子分離膜2は、基板上に形成された第1絶縁膜21と、第1絶縁膜21上に形成された第2絶縁膜22と、を含む。第1絶縁膜21の底面21Aは下方に向けて膨出する凸曲面状である。

(もっと読む)

スタンダードセル、スタンダードセルを備えた半導体装置、およびスタンダードセルの配置配線方法

【課題】複数のスタンダードセルを有する半導体装置のチップ面積をさらに小さくする。

【解決手段】半導体装置SD1は第1および第2スタンダードセルSC1,SC2を備える。第1スタンダードセルSC1は、拡散領域An11、拡散領域An11に対向する機能素子領域FE1、および金属層MT11を有する。第2スタンダードセルSC2は、拡散領域An11に連続する拡散領域An21、拡散領域An21に対向する機能素子領域FE2、ならびに拡散領域An21および機能素子領域FE2の間に形成された拡散領域CR21を有する。金属層MT11および機能素子領域FE2は、拡散領域An11、拡散領域An21、および拡散領域CR21通して電気的に接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】配線層の平坦性を維持しつつ、配線とインダクタとの間に生じる寄生容量を低減させた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に形成された第1の層間絶縁膜506と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた配線106と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた第1のダミーパターン107と、第1の層間絶縁膜506のうちインダクタ領域内に位置する部分に埋め込まれた第2のダミーパターン108と、第1の層間絶縁膜506の上方に形成された第2の層間絶縁膜と、第2のダミーパターン108の上方であって、第2の層間絶縁膜のうちインダクタ領域内に位置する部分に埋め込まれたインダクタ111とを備える。第2のダミーパターン108として金属が形成されていない。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造の縦型のMISFETの提供

【解決手段】Si基板1上に、一部に空孔4を有する絶縁膜2が設けられ、空孔4上及び絶縁膜2の一部上に横方向半導体層6が設けられ、半導体層6の側面の一部に導電膜3が接して設けられ、絶縁膜2により素子分離されている。半導体層6上の、空孔4直上部に縦方向半導体層7が設けられ、半導体層7の上部にドレイン領域(10,9)が設けられ、離間し、相対して下部にソース領域8が設けられ、ソース領域8は延在して、半導体層6全体に設けられている。半導体層7の全側面には、ゲート酸化膜11を介してゲート電極12が設けられ、ドレイン領域10、ゲート電極11及び導電膜3を介したソース領域8には、バリアメタル18を有する導電プラグ19を介してバリアメタル21を有する配線22が接続されている縦型のMISFET。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多層配線構造を使って、キャパシタンスが大きく、かつキャパシタンス値が安定なキャパシタ素子を半導体基板上に集積化する。

【解決手段】多層配線構造18は、少なくとも第1層目の層間絶縁膜16と、第1層目の層間絶縁膜中に埋設された第1配線層と、を含み、第1配線層は、第1の電源に接続され前記第1の層間絶縁膜中に埋設された第1の配線パタ―ン15C1と、第2の電源に接続され前記第1の層間絶縁膜中に埋設された第2の配線パタ―ン15C2と、を含み、第1の配線パタ―ンと前記第2の配線パタ―ンとは容量結合して第1のキャパシタを形成し、第1の配線パタ―ンは積層配線パタ―ン13C上に形成されて、前記第4の電極パターン13Gと容量結合して第2のキャパシタを形成し、第4の電極パターンは第2の配線パタ―ンに電気的に接続されている。

(もっと読む)

161 - 180 / 1,102

[ Back to top ]