Fターム[5F048BF11]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | 多層配線(2層) (1,460)

Fターム[5F048BF11]の下位に属するFターム

3層以上配線 (358)

Fターム[5F048BF11]に分類される特許

121 - 140 / 1,102

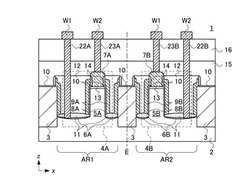

半導体装置

【課題】バイアス切替の前後でドレイン電流の大きさが変化しない縦型トランジスタを実現する。

【解決手段】半導体装置1は、第1の下部拡散層6A、第1の上部拡散層7A、及び第1のゲート電極9Aを有する第1の縦型トランジスタ4Aと、第2の下部拡散層6B、第2の上部拡散層7B、及び第2のゲート電極9Bを有する第2の縦型トランジスタ4Bと、第1及び第2のゲート電極9A,9Bに接続されるゲート配線と、第1の下部拡散層6A及び第2の上部拡散層7Bに接続される第1の配線W1と、第1の上部拡散層7A及び第2の下部拡散層6Bに接続される第2の配線W2とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】低電圧トランジスタ及び高電圧トランジスタの双方の要求を満たし、高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】ボロン又はリンを含む第1の不純物層と、第1の不純物層上に形成された第1のエピタキシャル層と、第1のエピタキシャル層上に第1のゲート絶縁膜を介して形成された第1のゲート電極と、第1のソース/ドレイン領域とを有する第1のトランジスタと、ボロン及び炭素又は砒素を含む第2の不純物層と、第2の不純物層上に形成された第2のエピタキシャル層と、第2のエピタキシャル層上に、第1のゲート絶縁膜よりも薄い第2のゲート絶縁膜を介して形成された第2のゲート電極と、第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

半導体装置および携帯電話機

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】RXスルートランジスタ群TH(RX)は、互いに直列に接続されたMISFETQ1〜Q5において、それぞれのMISFETのボディ領域と、隣接するMISFETのソース領域あるいはドレイン領域とを、それぞれ、ダイオード(整流素子)を介して接続する。そして、特に、nチャネル型MISFETの場合、MISFETのボディ領域から隣接するMISFETのソース領域あるいはドレイン領域へ向う向きが順方向となるようにダイオードを接続する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル不純物の拡散を抑制し、高性能・高信頼性を実現しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板第1及び第2の領域に非晶質化のためのイオン注入を行い、第1の領域及び第2の領域に第1の不純物及び第2の不純物をそれぞれイオン注入し、注入した不純物を活性化して第1の不純物層及び第2の不純物層を形成し、不純物層を形成した半導体基板上に半導体層をエピタキシャル成長し、第1及び第2の領域上にゲート絶縁膜を成長し、第1及び第2のゲート絶縁膜上に第1及び第2のゲート電極をそれぞれ形成する。

(もっと読む)

SOI基板の作製方法

【課題】貼り合わせ不良を十分に低減できるSOI基板を提供する。

【解決手段】半導体基板に絶縁層を形成し、絶縁層が形成された半導体基板にイオンを照射することにより脆化領域を形成し、ベース基板を加熱することで、ベース基板表面に付着した水分量を低減し、加熱されたベース基板と、脆化領域が形成された半導体基板と、を対向して接触させることにより貼り合わせ、貼り合わされたベース基板と半導体基板とを加熱して、脆化領域において分離させることにより、ベース基板上に半導体層を形成するSOI基板の作製方法。これにより、貼り合わせ不良を十分に低減できるSOI基板を提供することができる。

(もっと読む)

半導体装置

【課題】プロセスを簡素化し低コスト化を実現するとともに、さらに、システムを簡素化しノイズ対策を可能にするMEMSレゾネータ及びMEMSレゾネータの製造方法を提供する。

【解決手段】MEMSレゾネータの製造方法は、基板10上に形成された半導体デバイスとMEMS構造体部4とを有するMEMSレゾネータ2の製造方法であって、半導体デバイスは、上部電極30と下部電極26とを有するONOキャパシタ部6と、CMOS回路部8と、を含み、ONOキャパシタ部6の下部電極26を、第1シリコン層26を用いて、形成する。MEMS構造体部4の下部構造体16とONOキャパシタ部6の上部電極30とを、第2シリコン層52を用いて、形成する。及び、MEMS構造体部4の上部構造体18とCMOS回路部8のゲート電極34とを、第3シリコン層54を用いて、形成する。

(もっと読む)

半導体装置の製造方法、および電気機器

【課題】半導体装置の製造方法において、高電圧トランジスタのゲート耐圧を確保し得る程度の厚いゲート酸化膜の形成時に、この厚いゲート酸化膜が素子領域とトレンチ分離領域との境界で薄膜化するのを抑制することができ、しかも、サイズの小さい低電圧トランジスタの活性領域で、トレンチ分離溝の側壁部分での基板材料の酸化に起因した結晶欠陥が発生するのを防止する。

【解決手段】半導体基板101の表面に、半導体素子が形成されるべき素子領域を分離するようトレンチ分離領域100c、100f、100gを形成した後、該トレンチ分離領域を覆い、かつトレンチ分離領域からはみ出して該トレンチ分離領域に接する素子領域に一部重なるようシリコン窒化膜(酸化防止膜)109を形成し、該素子領域上に該酸化防止膜をマスクとして、該複数の半導体素子のうちの所定サイズの半導体素子で必要となる熱酸化膜の厚さより厚い熱酸化膜110を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】サイドウォール間に層間絶縁膜を埋め込むときに埋め込み不良の発生を防止できる半導体装置の製造方法を提供する。

【解決手段】シリコン基板2の表面上に、ゲート酸化膜6、ポリシリコン層(第1ゲート層)9、タングステンシリサイド層(第2ゲート層)10および絶縁層8が形成される。絶縁層8が所定のゲートパターンにエッチングされる。タングステンシリサイド層10が前記所定のゲートパターンにエッチングされる。タングステンシリサイド層10の側壁が後退される。この後、ポリシリコン層9が前記所定のゲートパターンにエッチングされる。ゲート酸化膜6が前記所定のゲートパターンにエッチングされる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板上に形成されたFETのソース側のエクステンション領域の抵抗値を低減し、半導体装置の動作速度を向上することができる技術を提供する。

【解決手段】ゲート電極4dの側壁に、ゲート電極4dのゲート長方向の幅が異なる第1サイドウォール6wおよび第2サイドウォール6nをそれぞれ形成する。これにより、第1サイドウォール6wおよび第2サイドウォール6nの形状によって第1サイドウォール6wおよび第2サイドウォール6nの下部に自己整合的に形成されるエクステンション領域37、38の半導体基板SBの上面の幅をそれぞれ異なる長さで形成する。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜にハフニウムを含む絶縁膜を使用したMISFETを有する半導体装置において、MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】本発明では、nチャネル型コア用トランジスタQ1のゲート絶縁膜と、pチャネル型コア用トランジスタQ2のゲート絶縁膜の構成を相違させている。具体的に、nチャネル型コア用トランジスタQ1では、ゲート絶縁膜に酸化シリコン膜SO1とHfZrSiON膜HK1の積層膜を使用している。一方、pチャネル型コア用トランジスタQ2では、ゲート絶縁膜に酸化シリコン膜SO1とHfSiON膜HK2の積層膜を使用している。

(もっと読む)

半導体集積回路及び半導体集積回路装置

【課題】従来技術と比較して占有面積が小さく、かつ基板電流が流れる経路の抵抗を低く抑え、寄生バイポーラトランジスタの動作を抑制することができる半導体集積回路及び半導体集積回路装置を提供する。

【解決手段】p型半導体基板10に形成されたドレイン領域D1、ソース領域S1、及びp型活性領域Bと、ドレイン領域D1とソース領域S1との間に形成されたゲート電極TG1と、ドレイン電極TD1と、ソース電極TS1と、基板電極TB1とを備えたNMOSトランジスタMN1と、ソース領域S1とp型活性領域Bとの間に形成されたドレイン領域D2及びソース領域S2と、p型活性領域Bと、ドレイン領域D2とソース領域S2との間に形成されたゲート電極TG2と、ドレイン電極TD2と、ソース電極TS2と、基板電極TB2とを備えたNMOSトランジスタMN2とを備え、NMOSトランジスタMN2は、基板電極TB1とソース電極TS1との間に接続される。

(もっと読む)

半導体装置

【課題】2つのトランジスタを混載した半導体装置において、ダミー配線を介して配線間で短絡が発生するのを防止し、信頼性の高い混載デバイスを実現可能にする。

【解決手段】本発明の半導体装置は、微細CMOS4Aと、微細CMOS4Aに接続される微細配線15とを有する微細CMOS領域と、微細CMOS4Aよりも耐圧が高い高耐圧デバイス4Bと、高耐圧デバイス4Bに接続され、平面視において微細配線15よりも配線幅が広いドレイン配線115及びソース配線116と、を有する高耐圧デバイス領域と、を具備し、高耐圧デバイス領域には、電気的に孤立したダミー配線14が少なくともドレイン配線115及びソース配線116に隣接して配置されない。

(もっと読む)

半導体装置の製造方法

【課題】多結晶シリコン層の表面平坦性を向上できる半導体装置の製造方法を提供する。

【解決手段】本実施形態によれば、半導体装置の製造方法は、基板上に非晶質シリコン膜を形成する工程と、前記非晶質シリコン膜を結晶化して多結晶シリコン膜を形成する工程と、プラズマドーピング法を用いて、前記多結晶シリコン膜にイオンを注入する工程と、前記イオンを注入した前記多結晶シリコン膜の表面を研磨する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの新規な閾値電圧制御技術を提供する。

【解決手段】半導体装置の製造方法は、半導体基板のp型領域上に、ゲート絶縁膜を形成する工程と、ゲート絶縁膜上に、化学量論組成よりも酸素量の少ない酸化アルミニウム膜を形成する工程と、酸化アルミニウム膜上に、タンタルと窒素とを含むタンタル窒素含有膜を形成する工程と、タンタル窒素含有膜上に、導電膜を形成する工程と、導電膜をパターニングして、ゲート電極を形成する工程と、ゲート電極をマスクとして、p型領域にn型不純物を注入する工程と、タンタル窒素含有膜の形成後に、熱処理を行う工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISデバイスにおいて、pチャネル型電界効果トランジスタの動作特性を劣化させることなく、ひずみシリコン技術を用いたnチャネル型電界トランジスタの動作特性を向上させる。

【解決手段】所望する濃度プロファイルおよび抵抗を有するnMISのソース/ドレイン(n型拡張領域8およびn型拡散領域13)およびpMISのソース/ドレイン(p型拡張領域7およびp型拡散領域11)を形成した後、所望するひずみ量を有するSi:C層16をn型拡散領域13に形成することにより、nMISのソース/ドレインにおいて最適な寄生抵抗と最適なSi:C層16のひずみ量とを得る。また、Si:C層16を形成する際の熱処理を1m秒以下の短時間で行うことにより、すでに形成されているp型拡張領域7およびp型拡散領域11のp型不純物の濃度プロファイルの変化を抑える。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜とメタルゲート電極を有するCMISFETを備えた半導体装置において、nチャネル型MISFETおよびpチャネル型MISFETのしきい値電圧の上昇を防ぐことができる技術を提供する。

【解決手段】CMISFETのしきい値を調整する目的で、高誘電率ゲート絶縁膜であるHf含有絶縁膜5に希土類元素またはアルミニウムを導入する際に、酸素をほとんど含まないランタン膜からなるしきい値調整層8bおよび酸素をほとんど含まないアルミニウム膜からなるしきい値調整層8aをnMIS形成領域1BおよびpMIS形成領域1AのHf含有絶縁膜5上にそれぞれ形成する。これにより、しきい値調整層8aおよびしきい値調整層8bからHf含有絶縁膜5および半導体基板1の主面に酸素が拡散することを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】イオン注入で所定の元素をゲート電極に導入して、異なる仕事関数を有するゲート電極のMOSトランジスタを形成する際に、製造工程の増加を抑制して低コストの半導体装置を提供する。

【解決手段】半導体装置の製造方法では、導電膜上5a,5bにおいて、第1の領域1aから第2の領域1bまでを覆う第1のマスク6b、第2の領域の上方にスペース部7b、及び第2の領域1bから第3の領域1cまでを覆う第2のマスク6cを有するマスクパターンを設ける。スペース部内、並びに第1及び第2のマスクの第1の側面にサイドウォール膜7aを設ける。第1の側面に接するサイドウォール膜の下に位置する導電膜の領域内に不純物を注入する。サイドウォール膜をマスクに用いて異方性エッチングを行うことによりゲート絶縁膜及びゲート電極を形成してMOSトランジスタ。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において工程数の削減を図ること。

【解決手段】領域HVp、LVn、LLnに第1〜第3のゲート電極36a〜36cを形成する工程と、領域LVnを覆い、かつ、領域HVpと領域LLnを露出するマスクパターン40を形成する工程と、マスクパターン40をマスクにしたイオン注入でp型ソースドレインエクステンション41とp型ポケット領域42を形成する工程と、マスクパターン40をマスクにしたイオン注入でn型ソースドレインエクステンション45を形成する工程と、領域HVpと領域LLnを覆い、かつ、第2の領域LVnを露出するマスクパターン52を形成する工程と、マスクパターン52をマスクにしてインジウムをシリコン基板1にイオン注入し、p型ポケット領域54を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

121 - 140 / 1,102

[ Back to top ]