Fターム[5F049PA14]の内容

受光素子−フォトダイオード・Tr (21,418) | 製造方法(工程) (2,065) | エッチング (375)

Fターム[5F049PA14]に分類される特許

141 - 160 / 375

pinダイオードを備えた集積回路構造の製造方法

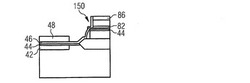

【課題】簡単に設計された、感度の高い、無線周波数の使用に適した、pinダイオード、を備えた集積回路構造を提供する。

【解決手段】集積回路構造において、保護される材料82が隣接している少なくとも1つの段を含んだ形状を形成し、段をも覆う保護層を形成し、上記保護層を形成した後、スペーサ素子層を形成し、スペーサ素子層に異方性エッチングを行い、段に少なくとも1つのスペーサ素子を形成し、スペーサ素子によって覆われていない領域において、保護層を薄膜化するか、または、完全に除去し、上記保護される材料82に沿って、保護層の少なくとも1つの残余領域150が残っており、保護層を薄膜化または除去した後、有効層を形成し、有効層をパターン形成すると同時に、スペーサ素子を除去して、保護される材料82を、残余領域150によって保護する。

(もっと読む)

光デバイス、半導体基板、光デバイスの製造方法、および半導体基板の製造方法

【課題】高品質な光デバイスをシリコン基板上にモノリシックに形成する。

【解決手段】シリコンを含むベース基板と、ベース基板上に設けられた複数のシード結晶と、複数のシード結晶に格子整合または擬格子整合する複数の3−5族化合物半導体とを備え、複数の3−5族化合物半導体のうちの少なくとも1つに、供給される駆動電流に応じて光を出力する発光半導体、または光の照射を受けて光電流を発生する受光半導体を含む光電半導体が形成されており、複数の3−5族化合物半導体のうち、光電半導体を有する3−5族化合物半導体以外の少なくとも1つの3−5族化合物半導体にヘテロ接合トランジスタが形成されている光デバイスを提供する。

(もっと読む)

プレーナ・アバランシェ・フォトダイオード

【課題】安価で、効果的な臨界制御で製造することのできる単純かつ効果的なアバランシュ・フォトダイオードを提供する。

【解決手段】本発明は、プレーナ接触領域を定める第1のn型半導体層とp型拡散領域を有する第2のn型半導体層とを有するプレーナ・アバランシェ・フォトダイオードを備える。本発明の構造のさらなる特徴は、n型半導体多重層と、n型半導体吸収層と、p型接触層とを備える。さらなる実施形態は、プレーナ接触領域を定める第1のn型半導体層と、n型半導体多重層と、n型半導体吸収層と、p型接触層に電気的に結合されたp型半導体層とを有するプレーナ・アバランシェ・フォトダイオードを備える。

(もっと読む)

窒化物半導体層の剥離方法、半導体装置の製造方法、及び半導体装置

【課題】第1基板から窒化物半導体層を容易に剥離する。

【解決手段】SiC基板101の表面で単層又は複数層のグラフェン層111が成長する工程と、グラフェン層との界面で、共有結合性を有することなく、原子レベルのポテンシャルの規則性のみを用いた結合力を伴って窒化物半導体層114が形成される工程と、窒化物半導体層114とグラフェン層111aとの間、あるいはグラフェン層相互間111a,111b,111cのポテンシャルによる接合力以上の力で、窒化物半導体層がSiC基板から剥離される工程とを備える。また、剥離された窒化物半導体層が第2基板130の表面に接合される。

(もっと読む)

半導体基板およびその製造方法、並びに半導体装置

【課題】段差部において膜厚の急激な変動が抑制された半導体膜を含む半導体基板、およびその製造方法、並びに、その半導体基板を備える半導体装置を提供する。

【解決手段】本発明に係る半導体基板1は、下地基板10と、下地基板10上の一部に形成されている金属膜20と、金属膜20を覆うようにして下地基板10上に形成されている絶縁膜30と、絶縁膜30上に形成され、かつ結晶化された半導体膜40とを備えている。絶縁膜30は、金属膜20の端部において段差部を有し、当該段差部の下地基板10に対して垂直な断面形状が、外に膨らむ「R」形状を呈している。上記段差面は、その上端部から下端部に向かって、テーパー角度ψが略0°から徐々に大きくなって、略40°〜90°であるテーパー角度θになるように形成されている。

(もっと読む)

長波長放射を検出することができる光検出器

【課題】長波長放射を検出することができる装置を提供する。

【解決手段】

長波長放射を検出することができる光検出器であって、絶縁層の近位端上に配置されたソースと、絶縁層の遠位端上に配置されたドレインと、近位端と遠位端との間でソース及びドレインを結合する少なくとも1つのナノアセンブリと、ソースとドレインとの間に配置され、少なくとも1つのナノアセンブリの長手方向に少なくとも1つのナノアセンブリと並置された少なくとも2つの表面プラズモン導波路とを備え、少なくとも2つの表面プラズモン導波路のうちの一方は、少なくとも1つのナノアセンブリの第1の側に沿って配置され、少なくとも2つの表面プラズモン導波路のうちの他方は、第1の側に対向する少なくとも1つのナノアセンブリの第2の側に沿って配置される長波長放射を検出することができる光検出器を実現する。

(もっと読む)

赤外線検出素子及びその製造方法

【課題】 信頼性の高い赤外線検出素子及びその製造方法を提供する。

【解決手段】

本発明に係る赤外線検出素子1は、基板2と、第1のPN接合部9と第2のPN接合部10とが交互に並ぶように基板2の一方の側の主面Aに沿って線状に延在すると共に、主面上で隣り合う部位が溝15によって仕切られたPN半導体層3と、第1のPN接合部9が一方の側に露出するように第2のPN接合部10の一方の側に設けられ、第2のPN接合部9を短絡させる中間電極4と、PN半導体層3の両端部E1,E2に設けられ、一方の側からの赤外線の入射によって第1のPN接合部9で発生した電荷による電位の変化を出力するための端子電極5,6と、を備える。

(もっと読む)

半導体アバランシェ増幅による低レベル信号検出

単一の独立した個別増幅器を用いることによる、又は入力信号を個別に増幅される個別成分に分散させることによる、光又は電気入力信号の検出のためのシステム及び方法を提供する。入力信号は、950nmより長い波長における光吸収プロセスの結果又は低レベル電気信号とすることができる。個別増幅器は、非ゲートモードで降伏領域内又はそれを越えたバイアス電圧を受けながら動作可能なアバランシェ増幅器であり、入力信号検出及び増幅半導体層にモノリシックに統合された複合誘電体フィードバック層を含む。 (もっと読む)

半導体受光素子および半導体受光素子の製造方法

【課題】耐久性が高く、かつ、高速応答性能を有する半導体受光素子およびその製造方法を提供すること。

【解決手段】半導体受光素子1は、入力部121と、第一出力部122と、第二出力部123とを含み、入力部121から入力した光を偏光分離せずに、入射光よりも強度の低い光に分岐して、第一出力部122、第二出力部123から出力する光分波器12と、第一出力部122からの光を伝播させる第一光導波路13Aと、第二出力部123からの光を伝播させる第二光導波路13Bと、第一光導波路13Aの光射出側端面、第二光導波路13Bの光射出側端面に接続された半導体光吸収層142とを備える。第一光導波路13Aからの光は、第二光導波路13Bからの光とは異なる方向から前記半導体光吸収層142に入射する。

(もっと読む)

半導体光検出素子及び半導体光検出素子の製造方法

【課題】シリコンを用いた半導体光検出素子であって、近赤外の波長帯域に十分な分光感度特性を有している半導体光検出素子及び半導体光検出素子の製造方法を提供すること。

【解決手段】フォトダイオードPD1は、第1導電型の半導体領域と第2導電型の半導体領域とで形成されたpn接合を有するn−型半導体基板1を備えている。n−型半導体基板1には、n−型半導体基板1の第2主面1b側にアキュムレーション層7が形成されていると共に、第1主面1a及び第2主面1bにおける少なくともpn接合に対向する領域に不規則な凹凸10が形成されている。n−型半導体基板1の第1主面1a及び第2主面1bにおけるpn接合に対向する領域は、光学的に露出している。

(もっと読む)

光電変換装置の製造方法

【課題】表面表域の注入プロファイルのばらつきを抑制する。

【解決手段】半導体基板の上に第1の絶縁膜202iを形成する第1の工程と、前記第1の絶縁膜の上に導電層を形成し、ゲート電極203を形成する第2の工程と、前記ゲート電極をマスクとして前記第1の絶縁膜の露出した表面をエッチングする第3の工程と、前記第1の絶縁膜におけるエッチングされた部分を介して第1導電型の不純物イオンを前記半導体基板に注入することにより、光電変換部における電荷蓄積領域となるべき半導体領域206iを形成する第4の工程と、前記第4の工程の後に、前記薄膜化された部分を除去する第5の工程と、前記半導体基板及び前記ゲート電極を覆うように第2の絶縁膜207を形成する第6の工程と、前記第2の絶縁膜を介して第2導電型の不純物イオンを前記半導体基板に注入することにより、前記光電変換部における表面領域208を形成する第7の工程とを備える。

(もっと読む)

メサ型フォトダイオード及びその製造方法

【課題】メサ上に再成長される半導体層によるメサの被覆性を、工程の追加を行わずに向上させることができるようにする。

【解決手段】メサ(受光領域メサ19)の側壁は、当該メサの裾が広がる方向に傾斜する斜面である。メサの少なくとも側壁112は、その上に成長された、第1導電型、第2導電型、半絶縁型、ないしノンドープの半導体層(例えば、ノンドープInP層17)により被覆されている。メサの下端部における斜面の傾斜角度θ1よりも、メサの上端部における斜面の傾斜角度θ3の方が小さい。

(もっと読む)

アバランシェホトダイオード及びこれを用いた光受信モジュール

【課題】増倍率が低い状態においても、光吸収層内で発生した電子の、光吸収層と電界調整層の界面への蓄積が抑制され、素子破壊に至る光信号強度を増加させることが可能な光吸収層を有するアバランシェホトダイオード及びこれを用いた光受信モジュールの提供。

【解決手段】電気調整層のうち、積層方向の少なくとも一部における伝導帯端のエネルギー準位が、光吸収層における伝導帯端のエネルギー準位より高く、増倍層の伝導帯端のエネルギー準位より低いことを特徴とする。

(もっと読む)

多結晶ウルツ鉱型半導体素子及びその製造方法

【課題】低コストで、かつ、高効率の光学デバイスを製造する。

【解決手段】多結晶ウルツ鉱型半導体素子200の製造方法であって、層状物質であり、かつ、六回対称結晶構造を有するグラファイト基板201の主面に、表面処理を行うことにより表面を荒らす表面処理ステップと、表面処理ステップで表面処理された主面に、複数の結晶粒104を有する多結晶ウルツ鉱型半導体103を主面の垂直方向に成長させる成膜ステップとを含む。

(もっと読む)

アバランシェフォトダイオードおよびその製造方法

【課題】簡単な工程でガードリング構造を作り込むことのできるアバランシェフォトダイオードの製造方法を提供する。

【解決手段】拡散によりpn接合を形成する工程で、拡散マスク26の開口部28の一部に、拡散制御層24を設ける。拡散マスクを経てZnを窓層20に拡散し、受光部とガードリングとを同時に形成する。拡散制御層と窓層とで拡散係数がほぼ等しい場合、単純に拡散制御層の厚さに相当する厚みが拡散フロントでの深さの差となる。

(もっと読む)

半導体装置

【課題】メサ型のフォトダイオードを有する光通信用素子等の半導体装置において、メサ上部への配線の寄生容量を低減し、応答特性の高速化を図る。

【解決手段】基板11表面に形成されフォトダイオードのカソードなるn型高濃度層12a上にn型クラッド層12b、吸収層12c、p型クラッド層12d及びp型高濃度層12eの積層体をメサ型に形成する。当該積層体の側面及びn型高濃度層12aの側面は、互いに連続して基板11表面からp型高濃度層12eまで段差なく到達する壁面を形成する部分を有する。基板11上に配置された水平配線19aとフォトダイオードのアノードとなるp型高濃度層12eとの層間を接続する配線19dは当該壁面に沿って配置される。

(もっと読む)

半導体集積光デバイス及びその作製方法

【課題】作製時の歩留まりが高く、且つ光導波路と半導体光素子との結合効率を高めることができる半導体集積光デバイス及びその作製方法を提供する。

【解決手段】半導体集積光デバイス1Aは、n型InP基板3と、n型InP基板3上に設けられ、III−V族化合物半導体を含む光導波路110を有する半導体レーザ領域10と、半導体レーザ領域10と並んでn型InP基板3上に設けられ、光導波路110と光学的に結合されn型InP基板3の主面に沿って延びる光導波路21a〜21eを有する光導波領域20とを備える。光導波領域20は、n型InP基板3と光導波路21a〜21eとの間に設けられた下部クラッドとしての酸化シリコン層23を更に有し、光導波路21a〜21eは、III−V族化合物とは異なる半導体からなる。

(もっと読む)

光電変換装置の製造方法

【課題】光電変換装置外部と電気的に接続される領域となる端子部は、その製造工程中に、フォトダイオードのドライエッチング雰囲気、パッシベーション層のフッ酸系ウェットエッチング雰囲気に等に晒される。また、各工程におけるレジスト剥離に伴うプラズマアッシング雰囲気にも晒される。そのため、エッチング工程による端子部の表面でダメージが蓄積され、接触抵抗の増加、密着性の低下等の不良が発生する。

【解決手段】端子部10Bを、AlNd合金を用いた導電金属層210と、TiN、MoまたはCrを主成分とする耐エッチング層211により構成した。AlNd合金を用いた導電金属層210の電気的抵抗値は小さく、高い導電性を有している。対して耐エッチング層211は、ドライ・ウェット両雰囲気に対して耐性を持つため、エッチングプロセスで生じる表面荒れが抑制され、接触抵抗の増加、密着性の低下等の不良発生が防げる。

(もっと読む)

固体撮像素子の製造方法

【課題】製造の容易化、集光特性の向上を図る。

【解決手段】SOI基板310の上部の単結晶シリコン層312内に、光照射面となる単結晶シリコン層312表面から同基板の酸化シリコン層311の方向に光電変換素子320を形成し、単結晶シリコン層312上部に、第1の支持基板330を形成し、ウェーハを反転して、SOI基板310及び酸化シリコン層311を除去し、単結晶シリコン層312の第1の支持基板330と反対側の面に配線層を形成し、配線層上に、第2の支持基板を貼り合わせ、ウェーハを反転して、第1の支持基板330を除去する。

(もっと読む)

pin型受光素子

【課題】 リーク電流の低減に基づいた低暗電流と素子容量の低減による高速応答及び高い受光感度を備えたpin型受光素子を提供する。

【解決手段】 InP等からなる半導体基板20上に、SiドープしたGaInAsからなるn型半導体層30、アンドープGaInAsからなるi型半導体層31及びZnドープGaInAsからなるp型半導体層32が順次積層されており、i型半導体層31及びp型半導体層32の周囲はメサ型に形成されており、そのメサ部の周囲にはパッシベーション半導体層40を有している。さらに、p型半導体層32のメサ中央部の受光領域の厚みh2は、その周囲の厚みh1よりも薄くなっている。このような構造のpin型受光素子では、低い暗電流特性を保持しながら、空乏層容量が低減し応答速度が格段に向上する。さらに、p型半導体層32での光吸収が低減され、受光感度も大幅に向上する。

(もっと読む)

141 - 160 / 375

[ Back to top ]