Fターム[5F058BA06]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜形成の目的、効果 (3,596) | 膜厚の制御 (334)

Fターム[5F058BA06]に分類される特許

161 - 180 / 334

絶縁膜の形成方法

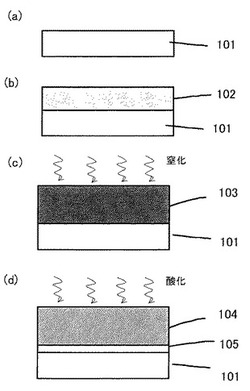

【課題】高誘電率ゲート絶縁膜としての使用に適し、高誘電率窒化金属シリケート膜を含んでなる絶縁膜を形成する。

【解決手段】金属原子及びシリコン原子が酸化反応を生じ難い雰囲気中にてスパッタ法によりシリコン基体101上に金属及びシリコンからなる膜102を堆積する第1の工程と、膜102を窒素プラズマを用いて窒化して窒素、金属及びシリコンからなる膜103を形成する第2の工程と、膜103を酸素プラズマを用いて酸化して窒化金属シリケート膜104を形成する第3の工程とを含む。第1の工程の終了から第2の工程の開始までの間、膜102を、その酸化反応が生じ難い雰囲気中に保持する。第3の工程により、膜104の下のシリコン基体101の表層部を酸化してシリコン酸化膜105を形成する。金属は、少なくともハフニウム及びジルコニウムのうちのいずれかを含む。

(もっと読む)

半導体装置、および半導体装置の作製方法

【課題】良好な品質を有する微結晶半導体膜を有する半導体装置及び該半導体装置の作製方法を提供することを課題とする。

【解決手段】微結晶半導体膜を用いて形成される薄膜トランジスタにおいて、成膜初期に形成される微結晶半導体膜の品質を向上するため、ゲート絶縁膜最上層に、蛍石型構造を持つイットリア安定化ジルコニア膜を形成する。その上に微結晶半導体膜を堆積させることにより、特に下地との界面付近は下地の結晶性に影響を受け良好な結晶性が得られる。また、微結晶半導体膜を形成する前に、表面プラズマ処理を行い、下地の結晶性に影響されやすい状態で微結晶半導体膜を堆積する。さらに、下地のイットリア安定化ジルコニアと微結晶半導体膜の結晶が一致しやすいように、微結晶半導体膜にゲルマニウムを添加する。

(もっと読む)

高誘電率薄膜を用いた半導体装置の製造方法

【課題】高誘電率薄膜形成時および成膜後の各種工程での界面反応層の成長を制御・抑制することができる、電気的特性に優れた高誘電率薄膜を用いた半導体装置の製造方法の提供。

【解決手段】高誘電率薄膜の成膜工程又は成膜後の処理工程において、雰囲気中残留酸素分圧及び残留水分圧を所定の値以下に設定することにより、気相中から高誘電率薄膜を透過してシリコン基板との界面に供給される酸素量を低減してシリコン基板界面に形成される界面反応膜の膜厚を原子層レベルに制御し、ゲート絶縁膜として用いるZrO2等の高誘電率薄膜の膜厚を大きくすることにより、ゲート層を流れるトンネル電流の低減を図る。

(もっと読む)

半導体メモリ素子の素子分離膜形成方法

【課題】 本発明は、トレンチの底面に流動性の第1の絶縁膜を満たし、第2の絶縁膜を形成した後に乾式エッチング工程及び湿式エッチング工程を行ってトレンチの上部の幅を広げながら第2の絶縁膜に含まれるフッ素(F;fluorine;フローリン)の量を減少させることができる半導体メモリ素子の素子分離膜形成方法を提供することを可能にすることを目的としている。

【解決手段】 トレンチが形成された半導体基板が提供される段階と、トレンチを含む半導体基板上に第1の絶縁膜を形成する段階と、第1の絶縁膜の一部を除去する第1のエッチング工程を行ってトレンチの開口部の幅を広げる段階と、第2のエッチング工程を行って第1の絶縁膜内に含まれた不純物を除去する段階と、第1の絶縁膜を含む半導体基板上に第2の絶縁膜を形成する段階とを含む構成としたことを特徴とする。

(もっと読む)

成膜装置、成膜方法及び成膜プログラム

【課題】成膜の停止時の機械的なシャッタ8動作のための遅延時間を抑制でき、再現性良く成膜を行うことができる成膜装置を提供する。

【解決手段】プラズマを発生させるプラズマ源4と、プラズマ源4と被処理体12との間に配置されたシャッタ8と、被処理体12の表面方向に誘導するようにプラズマに含まれる荷電粒子の進行方向を屈曲させる磁場フィルタ15と、シャッタ8が開いた状態において磁場フィルタ15を通過した荷電粒子により被処理体12上に成膜された膜の膜厚を検知する検知部14と、検知結果から成膜を停止するか否か判断する判断部101と、成膜を停止すると判断したときに、磁場フィルタ15をオフするように制御するフィルタ制御部102とを備える。

(もっと読む)

半導体装置および、その製造方法

【課題】LDDサイドウォール形成時に、NMOS/PMOS境界領域の2重エッチングによる不具合を克服する。

【解決手段】NMOS/PMOS境界領域にゲートレベル配線を形成し、LDDサイドウォール形成時に2重エッチングされるゲートレベル配線の最上層に、サイドウォール絶縁膜層とエッチング選択比のとれる膜107をハードマスクとして形成しておくことで、ゲートレベル配線に接続するプラグコンタクト112形成時にゲート電極のオーバーエッチによる堆積物の付着を防止する。

(もっと読む)

半導体装置およびその製造方法

【課題】 表示性能の優れたディスプレイパネルを安価に得るため、直接成長多結晶シリコン膜をチャネル層に用いたボトムゲート構造TFTを実現するために、ゲート絶縁膜中の固定電荷を低減し、かつ直接成長法による半導体多結晶膜の成膜温度を低温化する。

【解決手段】 シリコン酸窒化膜をゲート絶縁膜に用いることにより、膜全体の固定電荷密度を低減させるとともに半導体膜成膜時の原料原子の吸着をうながす。さらに、半導体膜成膜初期にゲルマニウムを含むガスを混合して表面吸着を促し成膜を促進する。これらにより半導体多結晶膜の成膜温度を下げる。

(もっと読む)

半導体装置の製造方法

【課題】枚葉式成膜装置によってウェーハを連続処理する際に、1枚目と2枚目以降とにおいて同様のウェーハ面内膜厚分布を得る。

【解決手段】半導体装置の製造方法は、活性種を含む反応ガスを用いて、複数の半導体基板上に順に薄膜を形成する成膜工程を備える。成膜工程は、反応室において複数の半導体基板に対して1枚ごとに行なうと共に、複数の半導体基板のうち1枚目の半導体基板上に薄膜を形成する工程(a)と、工程(a)の後に、複数の半導体基板のうち2枚目以降の半導体基板上に薄膜を形成する工程(b)とを含み、工程(a)は、工程(b)とは異なる条件をもって行なう。

(もっと読む)

セラミック状酸化ケイ素系被膜の形成方法、セラミック状酸化ケイ素系被膜を有する無機質基材の製造方法、セラミック状酸化ケイ素系被膜形成剤および半導体装置

【課題】ハイドロジェンシロキサン系ポリマーを使用して、無機質基材上の凹凸、段差を平坦化でき、クラック、ピンホールがなく、シラノール基等を実質的に含有していないセラミック状酸化ケイ素系被膜を形成する方法、かかる被膜を有する無機質基材の製造方法、かかる被膜に変換可能な被膜形成剤および半導体装置を提供する。

【解決手段】無機質基材にオルガノハイドロジェンシロキサン・ハイドロジェンシロキサンコポリマーを被覆し不活性ガス又は酸素ガス含有不活性ガス(酸素ガスは20体積%未満である)中で高温加熱して、該被膜をセラミック状酸化ケイ素系被膜に変換することによる、セラミック状酸化ケイ素系被膜の形成方法、該被膜を有する無機質基材の製造方法。オルガノハイドロジェンシロキサン・ハイドロジェンシロキサンコポリマー又はその溶液からなるセラミック状酸化ケイ素系被膜形成剤。無機質基板の酸化ケイ素系被膜上に少なくとも半導体層が形成されている半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】 構成元素として窒素とシリコンとを含む絶縁膜の形成時に、窒素原子の過度の拡散を抑制し、かつその絶縁膜の窒素濃度を高めることが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板上に、窒素とシリコンとを含む第1の絶縁膜を形成する。(b)第1の絶縁膜を還元性雰囲気に晒す。(c)工程bの後、第1の絶縁膜を窒化性雰囲気に晒す。

(もっと読む)

反応性スパッタリング装置

【課題】シリコン基板上のMOSFETにおいて、非常に薄い厚みを有し、膜質の高い均一性を有し、より高い誘電率を有する誘電体膜を堆積する装置を提供する。

【解決手段】反応性スパッタリング装置であって、ウエハー22が配置されるウエハーホルダ11と、ウエハーホルダ11の回転軸から外れた上方に傾斜して設けられたターゲット12と、ウエハーホルダ11の下方に該ウエハーホルダ11を挟んでそれぞれ設けられたガス導入部17と排気ポート16とを設ける。

(もっと読む)

表面処理方法およびプラズマ処理装置

【課題】本発明は、被処理物の表面に形成された凹凸部にピッチ寸法が相対的に短い部分が設けられている場合であっても、均一な厚みの処理層を得ることができる表面処理方法およびプラズマ処理装置を提供する。

【解決手段】処理チャンバ内を大気圧よりも減圧し、前記処理チャンバ内に反応ガスを導入し、前記処理チャンバ内にプラズマを発生させ、前記プラズマにより前記反応ガスを分解、活性化し、前記プラズマと被処理物との間に設けた電荷透過制御部の電界を調節することににより、前記被処理物の表面における電荷の量を制御しつつ前記被処理物の処理を行うこと、を特徴とする表面処理方法が提供される。

(もっと読む)

シリコン含有膜を形成する方法

シリコン含有膜を形成する方法であって、基板を反応チャンバーに供給すること、前記反応チャンバー中に少なくとも1つのシリコン含有化合物を注入すること、前記反応チャンバー中に少なくとも1つのガス状共反応物質を注入すること、および前記基板、シリコン含有化合物、およびガス状共反応物質を550℃以下の温度で反応させ、前記基板上に蒸着されたシリコン含有膜を得ることを含む方法。窒化シリコン膜を調製する方法であって、シリコンウェーハを反応チャンバーに導入すること、シリコン含有化合物を前記反応チャンバー中に導入すること、前記反応チャンバーをイナートガスでパージすること、および窒素を含有するガス状共反応物質を、前記シリコンウェーハ上に窒化シリコンの単分子層を形成するために適切な条件下で、前記反応チャンバーに導入することを含む方法。  (もっと読む)

(もっと読む)

半導体装置

【課題】ゲート電極と高誘電率ゲート絶縁膜の間に生じる反応を抑制でき、高集積化および高速化に適した素子構造を有する半導体装置を提供する。

【解決手段】絶縁ゲート電界効果トランジスタを有する半導体装置であって、この絶縁ゲート電界効果トランジスタは、高誘電率膜を含むゲート絶縁膜と、第1の導電層およびこの第1の導電層より抵抗率の低い第2の導電層を含む積層構造をもつゲート電極を有し、第1の導電層は、前記高誘電率膜上に接して設けられ、密度5g/cm3以上の窒化チタンからなる半導体装置。

(もっと読む)

プラズマ処理装置、プラズマ処理方法および終点検出方法

【課題】 プラズマ処理において、その終点を精度よく検出する。

【解決手段】 プラズマ処理装置100は、チャンバー1内でプラズマを生成させるプラズマ生成手段と、被処理体(ウエハW)へ向けて移動するプラズマ中の活性種の粒子数の積算値を計測する計測部60と、計測された粒子数の積算値が設定値に達した場合に、プラズマ処理を終了させるように制御する制御部50と、を備えている。計測部60は、光源部61から所定のレーザー光をプラズマへ向けて照射し、VUVモノクロメーターを備えた検知部63で受光することにより活性種の粒子数を測定する。

(もっと読む)

半導体デバイスの製造方法。

【課題】高誘電体膜とシリコン基板とを分離する、極薄かつ緻密な界面層を形成する半導体デバイスの製造方法を提供する。

【解決手段】本発明の半導体デバイスの製造方法は、シリコン基板表面にシリコン酸化膜を形成する工程(酸化膜形成ステップ)と、シリコン酸化膜を所望膜厚だけ残してエッチングする工程(エッチングステップ)と、エッチング後のシリコン酸化膜上に高誘電体膜を形成する工程(高誘電体膜形成ステップ)とを有する。

(もっと読む)

窒化シリコン膜の製造方法

【課題】PCVD法によるSiN膜の成膜後の表面平坦性を向上させる手段を提供する。

【解決手段】反応室内に投入した半導体ウェハに、PCVD法を用いて窒化シリコン膜を成膜する窒化シリコン膜の製造方法において、反応室内に、酸素を残留させた状態で、窒化シリコン膜を成膜するための半導体ウェハを投入する。

(もっと読む)

酸化膜形成方法及びその装置

【課題】大型基板に対して膜厚分布が均一となるように製膜する。

【解決手段】複数種類の有機シリコンが気化状態となる温度領域のもとで前記反応ガスを前記基板に供給する。酸化膜形成装置1は基板9を格納する処理炉2を備える。基板9にはガス供給系4からオゾンガスと複数種類の有機シリコンガスとを含んだ反応ガスが供給される。処理炉2は炉内温度が前記複数種類の有機シリコンが気化状態となる温度領域に調節される。複数種類の有機シリコンガスとしてはテトラメチルシランとヘキサメチルジシラザンとが例示される。

(もっと読む)

基板処理装置

【課題】液体原料の気化ガスの処理室への供給を安定させる。

【解決手段】基板処理装置は、液体原料を貯留する液体原料タンク320,340と、液体原料タンク320にキャリアガスを供給するキャリアガス供給ライン312と、液体原料タンク320の液体原料を液体原料タンク340へ圧送する原料供給ライン322と、液体原料タンク340にキャリアガスを供給するキャリアガス供給ライン322と、液体原料タンク340の液体原料の気化ガスを処理室201へ供給する原料供給ライン232bと、キャリアガスの流量を制御するマスフローコントローラ314と、液体原料の気化ガスの流量を検出するマスフローコントローラ344と、マスフローコントローラ344の検出結果をマスフローコントローラ314にフィードバックするフィードバック装置と、を有する。

(もっと読む)

金属酸化物材料を堆積する方法

本発明は、原子層堆積(ALD)プロセス又はALD型プロセスによって作製される金属酸化物被膜の均一性を高めるための方法に関する。ハロゲン化金属含有前駆体と酸素含有前駆体(好ましくは水)の交互パルスを使用し、必要に応じてパージすることによって層が作製される。酸素含有前駆体のパルス後に改質剤のパルスを導入すると、層の均一性に好ましい効果(一般には、特に密に配置された基板を含むアプリケーションにおいて勾配を示す)を与える。特に、層厚さの均一性が改善される。本発明によれば、1〜3個の炭素原子を有するアルコールを改質剤として使用することができる。 (もっと読む)

161 - 180 / 334

[ Back to top ]