Fターム[5F064EE33]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線材料 (810) | 金属 (713) | アルミニウム (222)

Fターム[5F064EE33]に分類される特許

1 - 20 / 222

半導体装置

半導体装置

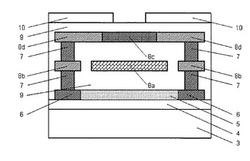

【課題】抵抗体とヒューズ素子が並列に接続された半導体装置において、ヒューズ素子切断時に抵抗体への損傷がなく、抵抗体とヒューズ素子とを積層すること。

【解決手段】半導体基板上に第1の絶縁膜を介して形成された抵抗体を設け、抵抗体の上に第2の絶縁膜を介して形成された遮光層を設け、遮光層の上に第3の絶縁膜を介して形成されたヒューズ素子のヒューズ部を有し、抵抗体と遮光層とヒューズ部を重畳した半導体装置とする。

(もっと読む)

半導体集積回路

【課題】設計する回路の中で電流の多く流れる信号線を容易に見つけ出すことができ、容

易にその部分の電流を測定できるスタンダードセルを提供することを課題とする。

【解決手段】電流検出用テストパッドを少なくとも2つ有するスタンダードセルを自動レ

イアウトで配置する。そして、2つのテストパッド間を接続する配線を切断することで、

該2つのテストパッドを電流測定用テストパッドとして利用する。なお、スタンダードセ

ル内の2つのテストパッド間は、過電流が流れることにより電流の流れる経路が遮断され

る配線によって接続される構成としてもよい。また、2つのテストパッド間をつなぐ配線

部にメモリ又はアナログスイッチを設ける構成としてもよい。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑えつつ、多数の配線間の時定数を一致させる。

【解決手段】半導体装置は、第1のサイズを持つ第1の外部端子と、第1のサイズよりも小さな第2のサイズを持つ複数の第2の外部端子と、第1の外部端子及び複数の第2の外部端子が、前記第1のサイズを基準として配列される外部端子領域と、外部端子領域に隣接して形成され、複数の第2の外部端子にそれぞれ対応付けられる複数の回路と、複数の第2の外部端子とそれら対応付けられた複数の回路との間をそれぞれ接続する複数の配線とを備える第1のチップを含む。複数の第2の外部端子及びそれらに接続された複数の配線は複数のインタフェースを構成し、複数のインタフェースの夫々は、互いに実質的に等しい時定数を持つように、時定数を調整する調整部を少なくとも一つ含む。調整部の少なくとも一部は、外部端子領域内の第1のサイズと第2のサイズとの差により生じるマージン領域に配置される。

(もっと読む)

半導体ダイ上にフィーチャをめっきするためのヒューズバス

【課題】半導体ダイ上に相互接続部又はボンドパッドなどのフィーチャ構造を電気めっきする方法を提供する。

【解決手段】方法は半導体基板の上方に複数のヒューズ(208)を形成する工程と、半導体基板の上方の複数の相互接続層(400〜408)と、該複数の相互接続層の上面の複数の相互接続パッド(502)とを形成する工程と、を含む。シールリング(202)が、半導体基板(302)と、前記複数の相互接続パッド(502)と、前記複数のヒューズ(208,320)とに形成された能動回路を包囲する。各ヒューズ(208,320)は、対応する相互接続パッド(502)とシールリング(202)とに電気的に接続される。各ヒューズ(208)が導通状態にあるとき、該ヒューズは対応する相互接続パッド(502)をシールリング(202)に電気的に接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】トリミングヒューズの上の絶縁膜が、トリミングヒューズの機能を高めるために適正な状態を維持することが可能な半導体装置を提供する。

【解決手段】表面を有する絶縁膜III上のヒューズ配線F1と、ヒューズ配線F1上の層間絶縁層II1,II2,PIと、層間絶縁層II1,II2,PIの内部に位置する、ヒューズ配線F1と平面視において重ならない領域に形成された電極部PDとを備える。上記ヒューズ配線F1の真上のうち少なくとも一部の第1の領域において、層間絶縁層II1,II2,PIの厚みが、第1の領域以外の第2の領域における層間絶縁層II1,II2,PIの厚みより薄くなるようにトリミング開口部LTCが形成される。トリミング開口部LTCの内側において側壁および底面の少なくとも一部を覆うアルミニウム薄膜部SALを備える。アルミニウム薄膜部SALは、側壁の少なくとも一部から、底面より上側において上記表面に沿う方向に連なる。

(もっと読む)

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電圧の供給を停止しても論理回路の結線状態を保持可能なプログラマブルロジックデバイスにおける処理速度の向上及び低消費電力化を図ることを目的の一とする。

【解決手段】論理状態を切り替え可能な複数の演算回路と、演算回路の論理状態を切り替えるコンフィグレーション状態切り替え回路と、演算回路の電源電圧の供給または停止を切り替える電源制御回路と、複数の演算回路の論理状態及び電源電圧の状態を記憶する状態記憶回路と、状態記憶回路の記憶情報に応じて、コンフィグレーション状態切り替え回路及び電源制御回路の制御を行う演算状態制御回路と、を有し、演算回路とコンフィグレーション状態切り替え回路との間に、酸化物半導体層にチャネル形成領域が形成されるトランジスタが設け、電源制御回路からの電源電圧の停止時に該トランジスタの導通状態を保持する。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

半導体装置

【課題】プログラマブルなアナログデバイスを提供する。また、電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルにおいて、ユニットセルのスイッチとして、第1乃至第4のトランジスタを用い、第1のトランジスタと第2のトランジスタとが接続された第1のノード、及び、第3のトランジスタと第4のトランジスタが接続された第2のノードの電位を制御することで、ユニットセルの出力を導通状態、非導通状態、又はアナログ素子を介した導通状態のいずれかに切り替える半導体装置を提供する。

(もっと読む)

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップ面積の増大を抑制しつつ、ダミー配線パターンの配置にかかる工数を低減する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、レイアウト領域に対して、半導体集積回路の配置配線(S1)を行った後、レイアウト領域に配置されているバルクセルを抽出し(S2)、レイアウト領域において、抽出したバルクセルの周囲に、所定の大きさを備える空き配線領域が存在するかどうかを検索し(S3)、検索の結果、所定の大きさを備える空き配線領域を検出した場合、抽出したバルクセルの座標を基準にして、検出した空き配線領域にダミー配線パターンを配置(S4)する。

(もっと読む)

半導体集積回路

【課題】フリップフロップにおけるアクティブ領域のレイアウトの凹凸を低減する。

【解決手段】半導体チップには、クロック領域CR1、ラッチ領域LR1およびバッファ領域BR1が設けられ、クロック領域CR1にはアクティブ領域AK5、AK6が形成され、ラッチ領域LR1にはアクティブ領域AK1、AK2が形成され、バッファ領域BR1にはアクティブ領域AK3、AK4が形成され、アクティブ領域AK1〜AK6の幅をそれぞれにおいて均一の幅として分割されている。

(もっと読む)

半導体装置における電流による配線破壊箇所の予測方法

【課題】半導体装置の電流による配線破壊箇所の予測方法において、解析時間を短縮する。

【解決手段】下層配線14A,14Bをそれぞれ一つの直列抵抗で、第1の下層ビア15A,第2の下層ビア15Bを1個の抵抗で、第1の上層ビア17A、第2の上層ビア18Bを1個の抵抗で、第1及び第2の上層配線16A,16Bを抵抗ブリッジ回路で、パワートランジスタTRを直列抵抗で、それぞれモデリングしてなる解析モデルをモデリング用計算機により生成する。回路シミュレータ3により、解析モデルにおけるパワートランジスタTRに電流を供給し、解析モデルにおける各抵抗に流れる電流に基づいて、第1及び第2の下層配線14A,14B、第1及び第2の上層配線16A,16Bにおける各抵抗の電流密度を計算し、各抵抗の電流密度と、配線破壊を起こす電流密度閾値とを比較器4により比較することにより、配線破壊箇所を予測する。

(もっと読む)

電気ヒューズ及びその製造方法

【課題】発熱体である抵抗から熱容量の大きいアノード領域への放熱を阻止し、ジュール熱を効率的に抵抗で消費するようにして、電気ヒューズの切断電力の低減化を図る。

【解決手段】絶縁膜5上にポリシリコン層6を形成し、該ポリシリコン層6上の一部に絶縁膜マスクを形成する。次に、該絶縁膜マスク層で被覆された以外のポリシリコン層6上にシリサイド層7を形成する。次にフォトエッチング工程を経てシリサイド層7、ポリシリコン層6をエッチングし、アノード領域1、カソード領域2及びアノード領域1とカソード領域2を接続するリンク領域3からなる電気ヒューズを形成する。電気ヒューズは、アノード領域1とリンク領域3の境界を挟んでリンク領域3方向からアノード領域1の一部に延在する非シリサイド領域を具備する。リンク領域3の非シリサイド領域は高抵抗領域11を構成し、アノード領域1の非シリサイド領域は熱伝導阻止層1bを構成する。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体装置

【課題】半導体装置の電源線および接地線の高抵抗化を抑制する。

【解決手段】第1の方向に延伸された第1の回路セル列及び第2の回路セル列と、第1の方向に延伸され、第1の回路セル列上に配置され、第1の電源線には第1の電源電位が供給される、第1及び第2の電源線と、第1の方向に延伸され、第2の回路セル列上に配置され、第2の電源電位が供給される第3の電源線と、第2の電源線と第3の電源線との間に接続され、導通状態において第2の電源線と第3の電源線とを接続して第3の電源線から第2の電源線に第2の電源電位を供給し、非導通状態において第2の電源線と第3の電源線とを電気的に切り離す第1のトランジスタと、第1の回路セル列に配置され、第1の電源線から供給される第1の電源電位と第2の電源線から供給される第2の電源電位との間の電源電圧で動作する第1の回路素子とを備える。

(もっと読む)

半導体装置

【課題】多層配線構造を有する半導体装置にダミーパタンを配線空隙に効率よく製造容易的に形成する。

【解決手段】多層配線構造の半導体装置において、狭い配線空隙(Area_S1)に、広い配線空隙(Area_S2)に形成されたダミーパタン(22,23)と異なる向きのダミーパタン(21)が形成されている。

(もっと読む)

半導体集積回路

【課題】製造コストを増大させずに、半導体集積回路の電源配線、接地配線の電圧降下を減少させる。

【解決手段】半導体チップ1上の第1の方向に延びる電源配線12Aが配置され、半導体チップ1上の第2の方向に延びると共に、第2の方向から第1の方向に屈曲し、電源配線12Aの一部と重畳する屈曲部24Aを有する電源引き出し配線22Aが配置されている。また、第1の方向に延びる接地配線12Bが配置され、第2の方向に延びると共に、第2の方向から、第1の方向とは逆方向の第3の方向に屈曲し、接地配線12Bの一部と重畳する屈曲部24Bを有する接地引き出し配線22Bが配置されている。電源引き出し配線22Aと接地引き出し配線22Bを覆う第1の層間絶縁膜13の中には、電源配線12Aと屈曲部24Aを接続する電源配線ビアコンタクト14Aと、接地配線12Bと屈曲部24Bを接続する接地配線ビアコンタクト14Bが配置されている。

(もっと読む)

1 - 20 / 222

[ Back to top ]