Fターム[5F083AD03]の内容

Fターム[5F083AD03]の下位に属するFターム

トレンチゲートトランジスタ(単孔にゲートを埋込むもの) (266)

突起状半導体柱の側面全体をゲート電極で覆うもの (130)

Fターム[5F083AD03]に分類される特許

41 - 60 / 145

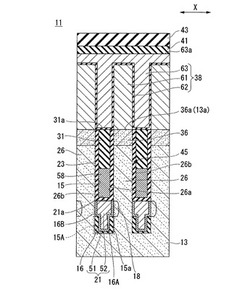

半導体装置及びその製造方法

【課題】本発明は、微細化された埋め込みビット線を容易に形成可能であると共に、埋め込みビット線の抵抗値を低くすることで高性能化を実現可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板13の主面13aに形成された第1の溝15と、第1の溝15の底面15a、及び第1の溝15の底部15Aに位置するピラー26の側壁面26a,26bに設けられ、側壁面26aを露出する第1の開口部16A、及び側壁面26bを露出する第2の開口部16Bを有した絶縁膜16と、第1の開口部16Aから露出された側壁面26aに形成された半導体基板と反対導電型の下部不純物拡散領域18と、絶縁膜16を介して、第1の溝15の底部15Aに設けられ、第1及び第2の開口部16A,16Bを埋め込むと共に、下部不純物拡散領域18及び側壁面26bと接触し、かつ金属膜よりなる埋め込みビット線21と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】微細な配線を高アスペクト比かつ高密度で形成できる、半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜に隣り合う第1配線溝と第2配線溝を形成し、第1配線溝内に第1配線とその上の空間および第2配線溝内に第2配線とその上の空間を設け、等方性エッチングを行って、第1配線溝の幅が拡大されてなる第1マスク溝と第2配線溝の幅が拡大されてなる第2マスク溝を形成し、第1マスク溝及び第2マスク溝にマスク用絶縁材料を充填して、第1マスク溝内の第1マスク絶縁膜と第2マスク溝内の第2マスク絶縁膜を形成し、第1マスク絶縁膜及び第2マスク絶縁膜をマスクとして利用する異方性エッチングを行って、第1配線と第2配線との間を通過し上記層間絶縁膜を貫通するホールを、第1マスク絶縁膜と第2マスク絶縁膜に対して自己整合的に形成し、このホールに導電材料を充填してプラグを形成する、半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】側壁接合領域を有した半導体装置の製造方法を提供する。

【解決手段】基板をエッチングしてトレンチを形成するステップと、前記トレンチ底面の基板内に接合領域を形成するステップと、前記トレンチ底面を一定の深さエッチングして側壁接合領域を形成するステップと、前記側壁接合領域に接続するビットラインを形成するステップと、を含む半導体装置の製造方法。

(もっと読む)

垂直型トランジスタと埋め込みビットラインとを有する半導体メモリ素子及びその製造方法

【課題】垂直型トランジスタのドレイン領域と埋め込みビットラインとの間に抵抗接点(ohmic contact)を形成しつつも、その製造工程が簡単な半導体メモリ素子及びその製造方法を提供すること。

【解決手段】基板に形成されたトレンチによって上部へ突出した形のアクティブ領域と、アクティブ領域の上部に配置される第1の不純物領域と、アクティブ領域の下部に配置される第2の不純物領域と、第1の不純物領域と第2の不純物領域との間のアクティブ領域の側面に沿って配置されるゲート絶縁膜と、ゲート絶縁膜上に配置されるゲート電極膜と、そして、トレンチの下部でライナー膜によって第2の不純物領域と離隔するように配置される金属膜と、金属膜上で前記第2の不純物領域と直接接触されるように配置されるポリシリコン膜とからなる埋め込みビットラインとを備えることを特徴とする。

(もっと読む)

垂直型トランジスタの不純物領域の形成方法及びこれを利用する垂直型トランジスタの製造方法

【課題】位置及び不純物濃度を精密に制御できるようにする垂直型トランジスタの不純物領域の形成方法及びこれを利用する垂直型トランジスタの製造方法を提供すること。

【解決手段】半導体基板に対するイオン注入を行って半導体基板の下部に不純物イオン接合領域を形成するステップと、そして、半導体基板に対するエッチングによりトレンチを形成し、エッチングは、不純物イオン接合領域の一部が除去されるようにして、不純物イオン接合領域のうち、除去されずに残っている領域がトレンチ下部で露出して埋め込みビットライン接合領域として機能するように行うステップとを含むことを特徴とする。

(もっと読む)

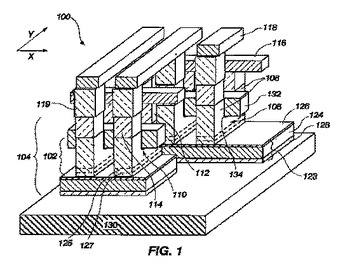

シングルゲートフィンFET及びその製造方法

【課題】新規なFinFET構造及びその製造方法を提供する。

【解決手段】シングルゲートフィンFET構造100は、2つの拡大された頭部、及び当該拡大された頭部と下層の超薄型ボディとを連結する2つの徐々に細くなる首部を有するアクティブフィン構造を含む。2つのソース/ドレイン領域102,104が、2つの拡大された頭部にそれぞれドープされる。絶縁領域26が、2つのソース/ドレイン領域の間に挿入される。溝分離構造24が、音叉形状のフィン構造の一方の側に配置される。片面サイドウォールゲート電極12bが、アクティブフィン構造における、溝分離構造とは反対側の垂直なサイドウォールに配置される。

(もっと読む)

半導体装置の製造方法

【課題】溝内の一部のみを覆うマスクパターンを、フォトレジスト膜を用いて形成する必要のない半導体装置の製造方法を提供する。

【解決手段】半導体基板1に、第1溝7を形成する工程と、第1溝7に第1絶縁膜8を形成する工程と、上面が第1絶縁膜の上端よりも下方になるように第1溝7内に第1導電膜9を充填する工程と、第1溝7の側面にカーボン膜10を形成する工程と、第1溝7内を第2絶縁膜11で充填する工程と、第1溝7内の側面の一方を覆うカーボン膜10を除去し、第1絶縁膜8の一部を露出させる工程と、第2絶縁膜11と露出された第1絶縁膜8を除去し、半導体基板1の一部を露出する工程と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ビット線材料埋設体の形状のばらつきに起因するビット線の配線抵抗値のばらつきを防ぐ半導体装置の製造方法を提供する。

【解決手段】製造方法は、第一溝4内に第一のビット線材料埋設体6および第二のビット線材料埋設体10からなるビット線11を形成する第一工程と、ビット線11に含まれる不純物を拡散させて第一不純物拡散領域13を形成する第二工程と、ピラー部1bを形成する第三工程と、ピラー部1bに対向する配線17を第二溝15内に形成する第四工程と、ピラー部1bの先端部に、第二不純物拡散領域19を形成する第五工程と、を具備し、第一工程が、第一溝4を完全に埋め込むように第一ビット線材料を形成した後に第一ビット線材料表面を平坦化し、第一溝4底部に残るように第一ビット線材料をエッチバックする工程を具備する。

(もっと読む)

半導体装置の製造方法

【課題】リーク電流が小さく、信頼性に優れたキャパシタを有する半導体装置を提供する。

【解決手段】半導体装置の製造方法は、下部電極上に、アモルファス状態の結晶核を形成した後、熱処理を行うことにより、結晶核を結晶化させる。下部電極上に、結晶核と同じ材料から構成されるアモルファス状態の容量絶縁膜を形成した後、熱処理を行うことにより、アモルファス状態の容量絶縁膜を結晶化させる。容量絶縁膜上に、上部電極を形成することによりキャパシタを得る。

(もっと読む)

半導体装置の製造方法

【課題】工程数が多く、煩雑になる問題を解決する半導体装置の製造方法を提供する。

【解決手段】半導体基板1に第1絶縁膜2を形成し、第1領域Aに第1導電型の第1ウエル層31を形成し、第1領域A以外の第1絶縁膜2上に第1半導体膜3を形成し、第1ウエル層31にトランジスタを形成し、第1半導体膜3及び第1領域Aの第1絶縁膜2の上に、トランジスタのビットコンタクトを兼ねる第2半導体膜7を形成する工程、第2半導体膜7上に、第2領域用B1のマスク8を積層してから、第1または第2導電型ドーパントを注入して第2ウエル層32を形成し、次いで、第2領域B1の少なくとも第2半導体膜7に、ドーパントを注入する工程、第2半導体膜7上に導電膜を積層してから、第1、第2半導体膜3,7及び導電膜を部分的にエッチングして、第1領域Aにトランジスタのビット配線層を、第2領域B1,B2に別の配線層を形成する工程、を具備する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造途中における下部電極の倒壊が効果的に防止され、微細化可能であり、歩留まりよく製造できる半導体装置およびその製造方法を提供する。

【解決手段】下部電極13と、下部電極13と容量絶縁膜を挟んで対向配置された上部電極15とを有するキャパシタ素子Caを備える半導体装置の製造方法であって、キャパシタ素子Caを形成する工程が、不純物を含有する酸化シリコンからなる層間絶縁膜12に埋め込まれて基板1の厚み方向に延びる外壁13Bを有する複数の下部電極13の外壁13Bと接触して、隣接する2以上の下部電極13間を繋ぐように、下部電極13と平面視で重ならない領域の一部に、不純物を含有しない酸化シリコンからなる支持部14Sを形成する工程と、湿式エッチングにより層間絶縁膜12を除去し、外壁13Bを露出させる工程とを有する半導体装置の製造方法とする。

(もっと読む)

半導体装置

【課題】信号経路に挿入されたフローティングボディ型のトランジスタを用いて高速動作と低消費電力動作が可能な半導体装置を提供する。

【解決手段】本発明の半導体装置において、フローティングボディ型のトランジスタQ10は、センスアンプの出力ノードNS(第1の回路ノード)とローカル入出力線LIO(第2の回路ノード)との間に挿入されている。トランジスタQ10のゲートにカラム選択信号YS(第1の信号)が供給され、カラム選択信号YSがトランジスタQ10を非導通に保つ第1の論理レベルと導通方向に導く第2の論理レベルとの間で変化する。トランジスタQ10を利用しない回路状態時に、第2の論理レベルに近い第1及び第2の電圧レベルが出力ノードNS及びローカル入出力線LIOに供給される。これにより、フローティングボディ型のトランジスタQ10のCV特性を適切に制御し、ゲート容量を抑制することができる。

(もっと読む)

半導体用配線

【課題】500℃酸化処理でも導電性を失わず、仕事関数がTiN以上であって、しかも貴金属よりも安価な配線材料を提供する。

【解決手段】NiTi混合膜であって、Ti/(Ni+Ti)で表されるTi含有量が60−80at.%なる組成比である配線材料を用い、この配線材料を500℃以上の高温酸化プロセスによりNiとTiO2とを含む混合膜に変換する。

(もっと読む)

半導体装置及びその製作方法

【課題】半導体記憶装置に適するトランジスタ構造及びその製作方法の提供。

【解決手段】デュアルチャネルトランジスタ50は、少なくとも、第一方向に沿って伸展する第一STI(シャロートレンチアイソレーション)と第二方向に沿って伸展する第二STIにより分離され、第一STIと第二STIが交差する半導体アイランド22と、第二方向に沿って伸展し、半導体アイランドの表面から内側に向かって凹んだゲートトレンチ26と、第二方向に沿って伸展し、ゲートトレンチ内に設けられたゲート30と、第二方向に沿って設けられ、半導体アイランドの上面に設けられた第一ソース/ドレイン領域と、第一ソース/ドレイン領域の間に設けられた第一U字型チャネル領域60と、第二方向に沿って設けられ、半導体アイランドの上面に設けられた第二ソース/ドレイン領域と、第二ソース/ドレイン領域の間に設けられた第二U字型チャネル領域62とを備える。

(もっと読む)

浮遊ボディセル、浮遊ボディセルを含むデバイス、ならびに浮遊ボディセルの形成方法。

バックゲート上に配置される浮遊ボディセルのアレイと、バックゲートから間隔の開いた浮遊ボディセルのソース領域およびドレイン領域と、を含む浮遊ボディセル構造。浮遊ボディセルは、ピラーの間に伸長するチャネル領域を有する大量の半導電性材料を各々含み、ピラーは、U形状トレンチなどの間隙によって分離されうる。アレイの浮遊ボディセルは、別のゲートに電気的に結合され、別のゲートは、大量の半導電性材料の側壁上に配置されてもよいし、大量の半導電性材料の間隙内に配置されてもよい。浮遊ボディセルデバイスを形成する方法も開示される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】第1の溝を埋め込み特性に優れたSOD膜で埋め込むことで、ショートの発生を抑制することのできる半導体装置及びその製造方法を提供する。

【解決手段】第1の溝17に第1のSOD(Spin On Dielectric)膜を埋め込み、第1のSOD膜を高温で改質させることで第1の絶縁膜45を形成し、第1の絶縁膜45上に位置する部分の第1の溝17に、第1のSOD膜と同じ材料よりなる第2のSOD膜46を埋め込み、第1のSOD膜を改質させる温度よりも低い温度で、第2のSOD膜46を改質させることで、第2の絶縁膜27を形成し、その後、ウエットエッチングにより第1の絶縁膜45を除去する。

(もっと読む)

半導体素子の製造方法

【課題】埋込みビットラインのビットラインコンタクトの形成方法を提供する。

【解決手段】半導体基板をエッチングして複数のピラー115を形成するステップと、ピラーの側壁に第1保護膜120を蒸着するステップと、第1保護膜が蒸着されたピラーをマスクとして半導体基板を1次エッチングするステップと、1次エッチングされた半導体基板及びピラーの側壁に第1絶縁膜125を形成するステップと、第1絶縁膜が形成されたピラーをマスクとして半導体基板を2次エッチングするステップと、2次エッチングされた半導体基板の表面に第2保護膜130及び第2絶縁膜135を形成するステップと、第2絶縁膜を含むピラーの側壁にバリア膜140を蒸着するステップと、ピラーの一側面のバリア膜、第1及び第2絶縁膜を除去し、第1保護膜及び第2保護膜により画成されるコンタクトホールを形成するステップと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】3次元レイアウトトランジスタにおいて、隣接するピラー間のビットラインを1本にして、微細化を図る。

【解決手段】隣接した第1および第2の半導体ピラー間に第1の絶縁膜7を介して形成されたビットライン8と、第1の半導体ピラーの側面および第1のビットライン上に形成され、第1のビットラインと第1の半導体ピラーとを電気的に接続する導電体10と、を備える半導体装置の製造方法において、導電体10を接続する第1の半導体ピラーの側面の第1の絶縁膜7を除去するため、第2の半導体ピラー側面に保護膜を残し、ビットライン8上の第1の絶縁膜7を選択的に除去する、あるいは第2の半導体ピラー側面に保護膜を残す際にビットライン8上の第1の絶縁膜7を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】DRAM素子のような半導体装置において、周辺回路領域に配置する回路の占有面積が削減でき、チップサイズの小さな半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に、不純物をドープして形成したメモリセル拡散層72を含むメモリセル領域7と、周辺回路拡散層82とゲート電極4を含む周辺回路領域8を備え、メモリセル領域7ではメモリセル拡散層72に接続されるビット配線10Aとして設けられ、周辺回路領域8では周辺回路拡散層82あるいはゲート電極42の何れかに接続する第1中間配線層10Bとして設けられる第1配線と、メモリセル領域7ではメモリセル拡散層72と接続されるキャパシタ用容量パッド20Aとして設けられ、周辺回路領域8では、コンタクトプラグの積層構造を介して周辺回路拡散層82あるいはゲート電極42の何れか一方に接続する第2中間配線層20Bとして設けられる第2配線20とを具備する。

(もっと読む)

半導体装置

【課題】ビット線が階層構造を有する半導体装置を改良する。

【解決手段】同時にアクセスされる2つのメモリセルMC(a),MC(b)に対するセンス動作を2つのセンスアンプSA0,SA0Aを用いて時分割で行い、その後、リストア動作を同時に行う。これにより、グローバルビット線GBLT0,GBLB0の途中にスイッチを介在させる必要がなくなるとともに、時分割でリストア動作を行う場合の問題が生じない。また、センスアンプSA0とセンスアンプSA0Aの寄生CRモデルが互いに同じとなることから、高いセンス感度を確保することも可能となる。

(もっと読む)

41 - 60 / 145

[ Back to top ]