Fターム[5F083AD11]の内容

Fターム[5F083AD11]の下位に属するFターム

PN接合容量型(Hi−Cを含む) (4)

プレーナ型 (103)

トレンチ型 (221)

スタック型 (2,622)

プレート電極 (218)

キャパシタ誘電体膜の多層化 (161)

粗面化 (103)

Fターム[5F083AD11]に分類される特許

61 - 80 / 81

高誘電体膜形成用組成物とその製造方法

【課題】MOD法によるペロブスカイト型誘電物質からなる高誘電体薄膜の形成において、クラックの発生がなく、膜の収縮が小さく、かつ誘電特性に優れた誘電体薄膜を形成することができる高誘電体膜形成用組成物とその効率的な製造方法を提供する。

【解決手段】金属成分としてバリウム、ストロンチウム、マグネシウム及びカルシウムからなる群から選ばれる少なくとも1種のアルカリ土類金属元素と、チタン、スズ、又はジルコニウムから選ばれる少なくとも1種の元素を含有する複合有機酸塩液と、アルコール系溶剤及びそれとエーテル系溶剤又はエステル系溶剤からなる有機溶剤に、エチルヘキサン酸類及び/又はメチルペンタン酸類からなるカルボン酸を添加してなる混合有機液相とを含み、かつ、アルコール系溶剤の含有量は、混合有機液相の全体に対して40〜60容量%であることを特徴とする。

(もっと読む)

金属酸化物絶縁膜内に電荷保存ナノクリスタルを有する集積回路メモリ装置のゲート構造物及びその形成方法

【課題】金属酸化物絶縁膜内に電荷保存ナノクリスタルを有する集積回路メモリ装置のゲート構造物及びその形成方法を提供する。

【解決手段】集積回路メモリ装置のゲート構造を形成する方法は、集積回路基板100上に金属酸化物絶縁膜150を形成することを含む。絶縁膜内に周期律表のIV族から選択され、0.5cm2/s以下の熱拡散度を有するGe等の元素のイオンを注入して絶縁膜内に電荷保存領域を形成するが、電荷保存領域の下部にトンネル絶縁膜135を、電荷保存領域の上部にキャッピング絶縁膜140を有するように形成する。絶縁膜150を含む基板100は、熱処理されて電荷保存領域内に複数の分離された電荷保存ナノクリスタル130_NCが形成される。ゲート電極層160は、絶縁膜150上に形成される。

(もっと読む)

キャパシタおよびそれを用いた回路装置

【課題】ナノワイヤを用いた新規なキャパシタを提供する。

【解決手段】導電性のナノワイヤからなる第1の電極1と、第1の電極の外周を部分的に被覆する誘電体層2と、誘電体層の外周を被覆する第2の電極3と、を有するキャパシタ。導電性のナノワイヤからなり、第1の端部と第2の端部とを有する第1の電極と、第1の端部における外周を被覆し、第1の端部から前記第2の端部側に向かって、第1の電極の外周を被覆し、且つ前記第2の端部を被覆していない誘電体層と、誘電体層の外周を被覆する第2の電極と、を有するキャパシタ。

(もっと読む)

キャパシタと電界効果型トランジスタとを有する回路装置及び表示装置

【課題】電界効果型トランジスタとキャパシタとをナノワイヤを用いて構成した新規な回路装置を提供する。

【解決手段】電界効果型トランジスタとキャパシタとを有する回路装置であって、

前記電界効果型トランジスタは、第1のナノワイヤからなるチャネルを有し、

前記キャパシタは、導電性を有する第2のナノワイヤからなる第1の電極と、前記第1の電極の外周を部分的に被覆する誘電体層と、前記誘電体層の外周を被覆する第2の電極とを含み構成され、

前記電界効果型トランジスタのゲート電極、ソース電極及びドレイン電極の少なくとも一つに、前記キャパシタの前記第1又は第2の電極が接続されている。

(もっと読む)

コンデンサの製造方法

【課題】誘電率が高く、リーク電流が大きく劣化しない誘電体層を有するコンデンサの製造方法を提供する。

【解決手段】チタン、バリウム、ストロンチウム、及びIA族元素を含む誘電体前駆体溶液を基材上に塗布して塗膜を形成する塗布工程と、前記塗膜を700〜900℃で熱処理し、高誘電体膜を得る熱処理工程とを有し、前記高誘電体膜は誘電体100重量部に対し1.5〜5重量部のIA族元素を含むコンデンサの製造方法である。

(もっと読む)

微小構造体及び微小電気機械式装置の作製方法

【課題】微小構造体の空間を形成するために設ける犠牲層に使用されるフォトマスクの枚数を低減し、製造コストを削減する。

【解決手段】同一のフォトマスクを用いてパターニングされたレジストマスクにより犠牲層を形成する。レジストマスクにより第1の犠牲層をエッチングして形成した後に、同一のフォトマスクを使用してパターンを形成されたレジストマスクを用いて第2の犠牲層をエッチングして形成する。レジストマスクは一方の犠牲層のエッチング前に外形寸法を拡大又は縮小する等して変形することで、大きさの異なる犠牲層を形成することができる。

(もっと読む)

半導体装置

【課題】同一基板上に、同一工程で設けられた微小構造体と半導体素子とを有する半導体装置を提供する。

【解決手段】基板101上の微小構造体となる領域に第1の犠牲層103、その上に構造層105が設けられる。また半導体素子となる領域には半導体層104を成膜する。構造層には金属を用いて結晶化された多結晶シリコンを用いる。この多結晶シリコンは一般的な多結晶シリコンと異なり結晶粒界で共有結合が途切れず破壊応力が高く構造層に好適となる。またこの多結晶シリコンは半導体層104としても使うことが可能で、微小構造体と半導体素子を同一基板上に設けることができる。続けて構造層の上には第2の犠牲層108が設けられ、半導体層の上には導電層等が設けられる。最終的には第1と第2の犠牲層は除去され、構造層の下方と上方に空間を有する微小構造体とする。

(もっと読む)

ナノ混合の誘電膜、それを有するキャパシタ及びその製造方法

【課題】10Å以下のEOTを有し、漏れ電流の特性に優れたナノ混合の誘電膜、それを有するキャパシタ及びその製造方法を提供すること。

【解決手段】キャパシタの誘電膜は、ZrO2及びTiO2が、ナノ混合の状態に混ざり合ったナノ混合の誘電膜を備え、キャパシタは、下部電極と、該下部電極上にZrO2及びTiO2がナノ混合の状態に混ざり合って形成されたナノ混合の誘電膜と、該ナノ混合の誘電膜上の上部電極とを備え、キャパシタの誘電膜の製造方法は、原子層蒸着法を用いて、[ZrO2蒸着サイクル]及び[TiO2蒸着サイクル]をそれぞれm回及びn回反復して行い、ZrO2及びTiO2が、ナノ混合の状態に混ざり合ったナノ混合の誘電膜を形成するステップと、前記ナノ混合の誘電膜を緻密化するステップとを含む。

(もっと読む)

Bi系誘電体薄膜形成用組成物およびBi系誘電体薄膜

【課題】800℃未満の低温焼成によってもBi系誘電体の結晶化薄膜を得ることができるBi系誘電体薄膜形成用組成物とBi系誘電体薄膜を提供する。

【解決手段】少なくともSr、Bi、Taおよびランタノイド系元素Aの各金属または複合金属のアルコキシド、有機塩あるいは錯体を反応させることによって得られる化合物を含有させてBi系誘電体薄膜形成用組成物を構成する。この組成物の塗膜を800℃未満の低温で焼成することにより、下記一般式(1)

Sr1-XAβBi2+Y(Ta2-ZNbZ)O9+α・・・・・(1)

(式中、Aは、ランタノイド系元素を表す。X、Y、αは、それぞれ独立に0以上1未満の数を表し、Zは、0以上2未満の数を表し、βは、0.09以上0.9以下の数を表す。)で表されるBi系誘電体の結晶化薄膜を得る。

(もっと読む)

処理管

【課題】バッチ式リモートプラズマ処理装置における処理管を提供する。

【解決手段】バッチ式リモートプラズマ処理装置に適用される処理管は、複数枚のウエハ1が積層して収容される処理室12と、処理室12から区画され、処理ガス41が供給される放電室33であって、少なくともこの放電室33内でプラズマ40を生成する一対の電極部を収容可能な放電室33と、を備えている。処理管は放電室33内のプラズマ40で活性化させた粒子42を処理室12へ供給することができる。

(もっと読む)

半球粒状シリコン及びナノ結晶粒サイズのポリシリコンのための単一ウエハ熱CVDプロセス

半球粒状シリコン層とナノ結晶粒サイズのポリシリコン層を堆積させる方法が提供される。半球粒状シリコン層とナノ結晶粒サイズのポリシリコン層は、単一基板化学気相堆積チャンバ内で堆積される。半球粒状シリコン層とナノ結晶粒サイズのポリシリコン層は、半導体デバイスにおいて電極層として用いることができる。一態様において、二ステップ堆積プロセスは、粗さが減少したナノ結晶粒サイズのポリシリコン層を形成するために提供される。 (もっと読む)

金属箔上におけるチタン酸バリウムストロンチウムを含む多層構造

【解決手段】本発明は、多層構造に関しており、該多層構造は、結晶化した又は部分的に結晶化したチタン酸バリウムストロンチウム(BST)薄膜複合体と、金属箔基材とを有している。障壁層が、金属箔基材と誘電体薄膜の間に挿入されてよい。さらに、本発明は、このような複合体を含む多層構造を具えるキャパシタに関する。  (もっと読む)

(もっと読む)

電極層および誘電体層を含む積層体ユニット

本発明にかかる積層体ユニットは、シリコン単結晶によって形成された支持基板と、支持基板上に、酸化シリコンによって形成されたバリア層と、異方性および導電性を有し、かつ、その上で、ビスマス層状化合物を含む誘電体材料をエピタキシャル成長させることができるBi2Sr2CaCu2O8で表わされる化学量論組成を有するBSCCOによって形成され、c軸方向に配向された電極層と、電極層上で、SrBi4Ti4O15で表わされる組成を有するビスマス層状化合物を含む誘電体材料をエピタキシャル成長させて形成され、c軸方向に配向された誘電体層を備えている。  (もっと読む)

(もっと読む)

半導体記憶装置およびそのレイアウト方法

【課題】 クロストークを低減し、読み出し電位差を十分にとることができ誤動作を防止することの可能な半導体記憶装置を提供する。

【解決手段】 ビット線、または裏打ちビット線とシールド線を有し、シールド線が少なくとも1箇所で分割され、ビット線、または裏打ちビット線がシールド線と接する面積を小さくしてビット線容量を低減しつつ、ビット線、または裏打ちビット線間のノイズを分割されたシールド線により低減する。

(もっと読む)

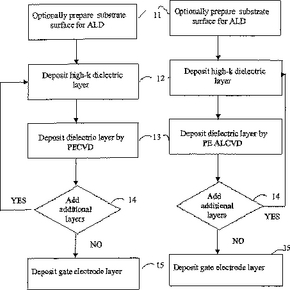

誘電体スタックの形成方法

本発明は、集積回路の中に誘電体スタックを形成する方法を提供し、(i)半導体基板上に高−k誘電体層を形成するステップと、(ii)高−k誘電体層を有する半導体基板を、プラズマ化学気相成長方法(PECVD)またはプラズマ原子層化学気相成長法(PEALCVD)において、窒素含有気相反応物およびケイ素含有気相反応物で処理するステップとを含む。さらに、本発明は、(i)少なくとも高―k材料を含む高―k誘電体層と、(ii)少なくともケイ素および窒素を含む誘電体層と、(iii)前記高―k誘電体層と前記誘電体層の間に配設された中間層とを含む集積回路中の誘電体スタックを提供し、前記中間層は前記高―k材料、ケイ素および窒素を含む。  (もっと読む)

(もっと読む)

微粒子含有体及び微粒子含有体の製造方法並びに記憶素子、半導体装置及び電子機器

【課題】良好な特性が得られる微粒子含有体と、比較的少ない手間で良好な特性の微粒子含有体を製造できる微粒子含有体の製造方法を提供すること。

【解決手段】シリコン基板100の表面に、膜厚が約50nmのシリコン酸化膜110を熱酸化によって形成する。シリコン酸化膜110中に、約30keVの注入エネルギーで、負イオン注入法によって銀を注入する。銀が注入されたシリコン酸化膜110を、200℃よりも高く、かつ、銀の融点未満の温度で熱処理して、銀微粒子を形成する。酸化雰囲気中で熱処理をして、微粒子の表面部分を酸化して、被覆層としての酸化銀140を形成する。ナノメートルサイズの複数の微粒子130および被覆層140を、少ない工程で形成する。

(もっと読む)

誘電体薄膜キャパシタの製造方法

【課題】 表面が十分平滑でクラック等の発生も少なく、かつ、十分に高い誘電率を持つ誘電体薄膜キャパシタを得ることのできる誘電体薄膜キャパシタの製造方法を提供する。

【解決手段】 基板10上に下部導体30を形成する工程と、前記下部導体30上に原料溶液を塗布して前駆体膜を形成する工程と、前記前駆体膜の結晶化温度よりも50℃〜150℃高い温度で1回目の熱処理を行い、前記前駆体膜を結晶化させて誘電体薄膜40を得る工程と、前記誘電体薄膜40上に上部導体51,52を形成する工程と、1回目の熱処理温度よりも100℃以上高い温度で2回目の熱処理を行う工程と、によって誘電体薄膜キャパシタを製造する。

(もっと読む)

高誘電率膜の処理装置および処理方法

【課題】効率の良い高誘電率膜の処理装置および処理方法を提供する。

【解決手段】

CVD(Chemical Vapor Deposition)処理、有機CVD処理あるいはMO−CVD(Metal Organic Chemical Vapor Deposition)処理などの高誘電率膜に所定の処理を施す処理装置であって、マイナスイオンを用いて、高誘電率膜の不純物と酸化反応させる。すなわち、膜中に残った炭素などの有機物と反応し、除去することを特徴とする。マイナスイオンは、酸化物高誘電率膜中の酸素欠陥に、効率良く選択的(優先的)に結合するため、酸化するイオンの量を制御することで、酸化がさらに抑制される。

(もっと読む)

ストロンチウム・ルテニウム酸化物焼結体の製造方法

【課題】 酸化ルテニウムより安価なルテニウム原料を用い、酸素加圧炉を用いることなく、スパッタリングターゲットとして所定の組成を有するストロンチウム・ルテニウム酸化物焼結体を、簡単且つ低コストで製造する方法を提供する。

【解決手段】 ストロンチウム源とルテニウム源からなる原料粉を仮焼成し、仮焼粉を粉砕成形し、1550〜1750℃で焼結する方法において、上記ルテニウム源として、最大粒子径が105μm以下、D50が5〜25μmの金属ルテニウム粉末を用いる。仮焼粉を粉砕する際の媒体は脱水アルコールが好ましい。

(もっと読む)

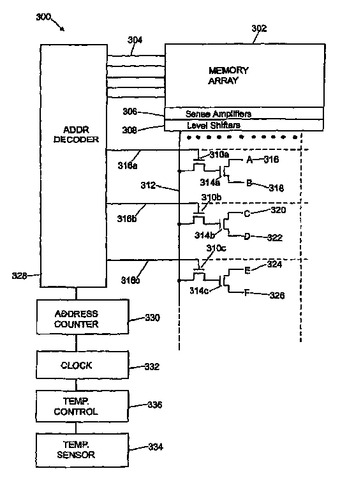

フラッシュ/ダイナミックランダムアクセスメモリフィールドプログラマブルゲートアレイ

集積回路デバイスにおいて2つのノードを選択的に相互接続するための回路は、複数のワード線及び複数のビット線を有するメモリアレイを含む。リフレッシュトランジスタは複数のビット線のうち一本に接続されたソース、ダイナミックランダムアクセスメモリワード線に接続された制御ゲート、及びドレインを有する。スイッチトランジスタはリフレッシュトランジスタのドレインに接続されたゲート、一番目のノードに接続されたソース、及び二番目のノードに接続されたドレインを有する。アドレスデコーダはワード線とダイナミックランダムアクセスメモリワード線に周期信号を供給する。  (もっと読む)

(もっと読む)

61 - 80 / 81

[ Back to top ]