Fターム[5F083EP22]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 制御機構 (7,428) | CGを有するもの (4,415)

Fターム[5F083EP22]の下位に属するFターム

スタックゲート (1,853)

スプリットゲート (271)

CGがFGを覆う構造 (414)

CGを複数有するもの (58)

Fターム[5F083EP22]に分類される特許

201 - 220 / 1,819

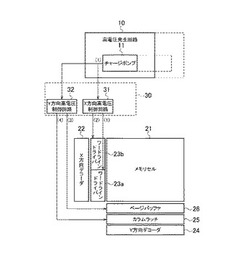

半導体記憶装置及びその高電圧制御方法

【課題】チャージポンプ等の高電圧生成部の回路面積を削減する。

【解決手段】半導体記憶装置は、ワードライン及びビットラインが接続されマトリクス状に配置された複数のメモリセル21と、ワードラインを駆動する複数のワードラインドライバ23a及び23b、電源電圧を昇圧して高電圧を生成するチャージポンプ11と、複数のメモリセル21のうちアクセスに関係のある箇所には高電圧が印加され、アクセスに関係のない箇所には電源電圧が印加されるように制御するX方向高電圧制御回路31及びY方向高電圧制御回路32とを備える。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の駆動方法

【課題】新たな構造の半導体装置、及びその駆動方法を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のpチャネル型トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電荷を保持させることで行う。また、保持期間において、メモリセルを選択状態とし、且つ、読み出し用トランジスタのソース電極およびドレイン電極を同電位とすることで、ノードに蓄積された電荷を保持する。

(もっと読む)

記憶素子、記憶装置、信号処理回路、記憶素子の駆動方法

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶素子を提供する。消費電力の低減可能な信号処理回路を提供する。

【解決手段】クロック信号に同期してデータを保持する記憶素子において、酸化物半導体層にチャネルが形成されるトランジスタ及び容量素子を用いることより、電源電圧の供給が停止した間もデータ保持ができる。ここで、電源電圧の供給を停止する前に、クロック信号のレベルを一定に保った状態で当該トランジスタをオフ状態とすることにより、データを正確に容量素子に保持させることができる。また、このような記憶素子を、CPU、メモリ、及び周辺制御装置のそれぞれに用いることによって、CPUを用いたシステム全体で、電源電圧の供給停止を可能とし、当該システム全体の消費電力を削減することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、窒素、リン、又は砒素など15族元素のいずれか一以上の元素が添加されている。

(もっと読む)

フラッシュEEPROM(FLASHEEPROMMEMORY)の消去方法

【課題】電荷の蓄積を制御することによりメモリセルを消去するフラッシュEEPROMの消去方法を提供する。

【解決手段】フラッシュメモリの消去方法は、F/Nトンネリング期間において、ウェル電極と第二半導体領域に対し正極性の第一電圧バイアスを印加し、且つコントロールゲート電極に対し負極性の第二電圧バイアスを印加するステップと、F/Nトンネリング期間のあとのトラップ減少期間において、ウェル電極と第二半導体領域に対し正極性の第三電圧バイアスを印加し、且つコントロールゲート電極に対し第一ゼロ電圧バイアスを印加するステップと、トラップ減少期間のあとのトラップアシストトンネリング期間において、コントロールゲート電極に対し負極性の第四電圧バイアスを印加し、且つウェル電極と第二半導体領域に対し第二ゼロ電圧バイアスを印加するステップと、を有する。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体記憶装置の製造方法

【課題】製造が容易なNAND型半導体記憶装置の製造方法を提供する。

【解決手段】製造方法は、基板101上に第1絶縁膜105及び第2絶縁膜106を交互に積層して積層体110を形成する工程と、第1絶縁膜105及び第2絶縁膜106の積層方向に延び、積層体110を貫通する貫通孔114を形成する工程と、貫通孔114の内面上に、MONOS116を構成するブロック絶縁膜、チャージトラップ膜及びトンネル誘電体膜の少なくとも一部を形成する工程と、トンネル誘電体膜上にチャネル半導体117を形成する工程と、積層体110にトレンチ121を形成する工程と、トレンチ121を介してエッチングを施すことにより、第2絶縁膜106を除去する工程と、第2絶縁膜106を除去した後の空間内に導電材料を埋め込む工程と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】面積の縮小を図る。

【解決手段】不揮発性半導体記憶装置は、複数のメモリストリング200を具備し、各メモリストリングは、一対の柱状部A、および一対の柱状部の下端を連結させるように形成された連結部Bを有する半導体層SPと、柱状部に直交したコントロールゲートCGと、一対の柱状部の一方と直交し、コントロールゲートの上方に形成された第1選択ゲートSGSと、一対の柱状部の他方と直交し、コントロールゲートの上方に形成され、第1選択ゲートと同一レベルでかつ一体である第2選択ゲートSGDと、柱状部とコントロールゲートとの各交差部に形成されたメモリセルトランジスタMTrと、柱状部と第1選択ゲートとの交差部に形成された第1選択トランジスタSSTrと、柱状部と第2選択ゲートとの交差部に形成された第2選択トランジスタSDTrと、を含む。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】複数のメモリセルを3次元状に配置し、かつ、メモリセルにMONOS型トランジスタを使用するNAND型不揮発性メモリにおいて、データ保持特性の劣化を抑制することができる技術を提供する。

【解決手段】ギャップ絶縁層GIL1の右端部側に凹部CUが形成されている。このとき、この凹部CUの形状を反映するように、凹部CUの内部に上部電位障壁層EB2と電荷蓄積層ECが形成されており、この凹部CUの形状を反映した電荷蓄積層ECの内側に形成される下部電位障壁層EB1によって、凹部CUが完全に埋め込まれている。このため、凹部CUを埋め込んだ下部電位障壁層EB1の表面は平坦になっており、この平坦になっている下部電位障壁層EB1の内側に柱状半導体部PSが形成される。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

半導体装置

【課題】同一ワード線上の各メモリセルの電位を一括で確定する事で、書き込み動作を短縮させることを可能とした半導体メモリ装置を提供する。

【解決手段】1つの電位制御回路に、複数のスイッチング特性を有するトランジスタを接続することで、書き込み電位を一括で確定する。電位を段階的に変化(上昇又は下降)させ続け、推移させながら所望の書き込み電位を確定し、書き込まれたデータに対する読み出しの結果のデータの正誤を常に監視することで、高精度な書き込み動作と高精度な読み出し動作を実現する。また酸化物半導体を用いたトランジスタの良好なスイッチング特性と高い保持特性を利用する。

(もっと読む)

半導体記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能(不揮発性)で、且つ、書き込み回数にも制限が無い、新たな構造の半導体記憶装置を提供する。

【解決手段】半導体記憶装置に、複数のメモリセルがマトリクス状に配設されたメモリセルアレイと、制御信号に応じて、複数のメモリセルの中から動作を行うメモリセルを選択するデコーダと、デコーダに対して制御信号を出力するか否かを選択する制御回路と、を設ける。なお、複数のメモリセルのそれぞれは、酸化物半導体によってチャネル領域が形成される選択トランジスタをオフ状態とすることによってデータの保持を行う。

(もっと読む)

半導体記憶装置へのデータの書込み方法及び半導体記憶装置

【課題】半導体記憶装置のメモリセルの参照セルとなる副記憶領域の読出し電流の変動を抑制して、メモリセルの読出し電流の判定時における誤判定を低減することができる半導体記憶装置へのデータの書込み方法及び半導体記憶装置を提供する。

【解決手段】メモリセルの第1不純物領域及び第2不純物領域に印加される電圧の大小関係が互いに異なる2つのデータ書込みステップによってメモリセルにデータの書込みをなす。

(もっと読む)

不揮発性記憶素子及びその製造方法

【課題】 信頼性を向上可能な不揮発性記憶素子及びその製造方法を提供する。

【解決手段】 不揮発性素子は、基板100、基板100の上に形成され、制御ベースゲート120a及び制御ベースゲート120aの上に形成される制御金属ゲート125anを有する制御ゲート電極137、制御ゲート電極137と基板100との間に形成される電荷格納領域110a、制御ゲート電極137の上に形成される制御ゲートマスクパターン130、及び制御ゲートマスクパターン130及び制御ベースゲート120aの間に形成された制御金属ゲート125aの側壁の上に形成される酸化防止スペーサ135aを備える。このとき、制御金属ゲート125anの幅は、制御ゲートマスクパターン130の幅より小さくなるように形成されている。これにより、制御金属ゲート125anが酸化工程又は酸化物等によって酸化されることを防止することができる。

(もっと読む)

半導体記憶装置

【課題】リフレッシュ時間のマージンを十分に確保しつつ、微細化が可能な半導体記憶装置を提供することを目的とする。

【解決手段】メモリセルを、読み出しトランジスタ、書き込みトランジスタ、キャパシタにより構成する。かかる構成において、キャパシタは読み出しトランジスタのゲートにかかる電位を制御する。書き込みトランジスタは、データの書き込みおよび消去を制御するとともに、キャパシタに蓄積された電荷が、該書き込みトランジスタのリーク電流で消失しないように、オフ時の電流が小さいトランジスタで構成する。書き込みトランジスタを構成する半導体層は、読み出しトランジスタのゲート電極とソース領域の間を架橋するように設ける。キャパシタは、読み出しトランジスタのゲート電極と重畳するように設ける。

(もっと読む)

半導体装置の製造方法

【課題】ウィンドウ特性の向上とリテンション特性の向上とを同時に図ることのできる半導体装置の製造方法を提供する。

【解決手段】シリコン基板上に、トンネル酸化膜、チャージトラップ膜、ブロッキング酸化膜、ゲート電極が、下側からこの順で形成された積層構造を有する半導体装置を製造する方法であって、前記ブロッキング酸化膜を形成する工程が、前記チャージトラップ膜上に結晶質膜を形成する結晶質膜形成工程と、前記結晶質膜の上層にアモルファス膜を形成するアモルファス膜形成工程とを具備し、前記結晶質膜形成工程と、前記アモルファス膜形成工程とを同一の処理容器内で連続的に行う。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】消費電力の少ない新規の半導体メモリ装置を提供する

【解決手段】書き込みトランジスタWTr_n_mのソースと読み出しトランジスタRTr_n_mのゲートとキャパシタCS_n_mの一方の電極を接続し、書き込みトランジスタWTr_n_mのゲートとドレインを、それぞれ書き込みワード線WWL_nと書き込みビット線WBL_mに、キャパシタCS_n_mの他方の電極を読み出しワード線RWL_nに、読み出しトランジスタRTr_n_mのドレインを読み出しビット線RBL_mに接続した構造とする。ここで、読み出しビット線RBL_mの電位はフリップフロップ回路FF_mのような反転増幅回路に入力され、反転増幅回路によって反転された電位が書き込みビット線WBL_mに出力される構造とする。

(もっと読む)

半導体基板の作製方法

【課題】半導体基板の欠陥を低減する。また、歩留まり高く欠陥の少ない半導体基板を作製する。また、歩留まり高く半導体装置を作製する。

【解決手段】支持基板に酸化絶縁層を介して半導体層を設け、該半導体層の端部における、支持基板及び酸化絶縁層の密着性を高めた後、半導体層の表面の絶縁層を除去し、半導体層にレーザ光を照射して、平坦化された半導体層を得る。半導体層の端部において、支持基板及び酸化絶縁層の密着性を高めるために、半導体層の表面から、レーザ光を照射する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリブロック内で選択的に消去動作を実行することが可能な積層型の不揮発性半導体記憶装置を提供する。

【解決手段】メモリブロック中の少なくとも1つのサブブロックを選択的に消去する消去動作を実行する際、選択された第1のサブブロックにおいては、ビット線及びソース線に第1電圧を印加する一方、ワード線には第1電圧よりも小さい第2電圧を印加する。ドレイン側選択ゲート線、及びソース側選択ゲート線には、第1電圧よりも所定の値だけ低い第3電圧を印加する。非選択とされた第2のサブブロックにおいては、ドレイン側選択ゲート線、及びソース側選択ゲート線には、第1電圧と略同一の第4電圧を印加する。

(もっと読む)

201 - 220 / 1,819

[ Back to top ]