Fターム[5F083GA18]の内容

Fターム[5F083GA18]に分類される特許

1 - 20 / 115

リレーデバイスを有するメモリ要素

【課題】メモリ要素有する集積回路を提供すること。

【解決手段】上記集積回路は、基板において形成された回路網と、回路網の上における複数の機械的リレーメモリ回路とを含む。集積回路は、回路網と複数の機械的リレーメモリ回路との間に配置された誘電スタックをさらに含む。誘電スタックは、複数の金属ルーティング層およびビア層を含む。回路網は、相補型金属酸化物半導体回路網を含む。回路網は、複数の機械的リレーメモリ回路に対する制御信号を生成するように動作可能である。

(もっと読む)

半導体装置及びその製造方法

【課題】放射線耐性能力をさらに向上することができる半導体装置を提供する。

【解決手段】半導体基板1の上方に形成された第1絶縁膜12と、第1絶縁膜12の上方に形成され、下部電極17と上部電極19に挟まれる強誘電体膜18を有するキャパシタQと、キャパシタの上に形成される第2絶縁膜26と、を有し、第1絶縁膜12と下部電極17の間に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第3絶縁膜16、38と、

を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域における上記プラグと、活性領域の外部における上記プラグとの双方を有する、微細化された半導体装置において、枠付け絶縁膜を確実に形成し、かつ導電性などの機能を最適化することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に形成される活性領域と、平面視における活性領域の周辺に形成されるゲート接続領域と、活性領域上に形成される複数の第1のトランジスタTGに挟まれる領域に形成される、第1のトランジスタTGと第1のトランジスタTGよりも上側の層とを電気的に接続するための第1の接続層CTと、ゲート接続領域上に形成される第2のトランジスタTGと、第2のトランジスタTGよりも上側の層とを電気的に接続するための第2の接続層とを備えている。上記第1の接続層CTには第1の導電部PP1aと第2の導電部PP2aとを含み、第2の接続層SNCには第3の導電部PP2bを含む。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のトランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電位を保持させることで行う。メモリセルの読み出しは、ビット線にプリチャージ電位を供給した後ビット線への電位の供給を止め、ビット線の電位がプリチャージ電位に保たれるか、または電位が下がるか、により行う。

(もっと読む)

記憶装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な記憶装置、及び該記憶装置を有する半導体装置を提供する。

【解決手段】第1の入力端子、及び第1の入力端子の入力信号の反転信号が入力される第2の入力端子、並びに第1の信号が出力される第1の出力端子、及び第1の信号の反転信号が出力される第2の出力端子、を有するレベルシフタと、第1の信号が入力される第3の入力端子、及び第1の信号の反転信号が入力される第4の入力端子、並びに第3の出力端子を有する第1のバッファと、第1の信号の反転信号が入力される第5の入力端子、及び第1の信号が入力される第6の入力端子、並びに第4の出力端子を有する第2のバッファと、を有し、第1のバッファの第3の出力端子から出力される信号が、レベルシフタの第1の入力端子に入力され、第2のバッファの第4の出力端子から出力される信号が、レベルシフタの第2の入力端子に入力される。

(もっと読む)

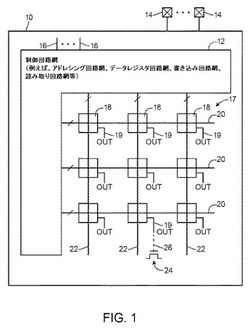

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

回路及び回路の駆動方法

【課題】消費電力を低減する。

【解決手段】入力信号を元に論理演算処理を行い、論理演算処理の結果に応じて設定される電位を記憶データとして保持し、記憶データに応じた値の信号を出力信号として出力する機能を有する演算回路を具備し、演算回路は、論理演算処理を行う演算部と、記憶データの電位を、論理演算処理の結果に応じた電位に設定するか否かを制御する第1の電界効果トランジスタと、記憶データの電位を、基準電位に設定するか否かを制御する第2の電界効果トランジスタと、記憶データに応じた値の信号を出力信号として出力するか否かを制御する第3の電界効果トランジスタと、を備える。

(もっと読む)

トランジスタ及び半導体装置

【課題】SEU耐性が高く、高性能で低価なトランジスタ及び半導体装置を提供すること。

【解決手段】絶縁性基板12上に形成されたシリコン層と、シリコン層に形成され、第1導電型であるボディ(P−)15、第2導電型であるソース(N+)13、ドレイン(N+)14からなる部分と、ボディ(P−)15及びソース(N+)13にボディ(P−)15と同一導電型で接合され、ソース(N+)13と同じもしくは高い電位が供給されるボディ端子(P+)16と、を具備する。ボディ(P−)15において放射線によって発生した負電荷は、ボディ端子(P+)16を介して当該トランジスタ外に流出する。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、電源電圧が選択的に供給され、第1の高電源電位が選択的に与えられる第1のノードを有する回路と、第1のノードの電位を保持する不揮発性の記憶回路とを有する。不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなる第2のノードとを有する。トランジスタはエンハンスメント型のnチャネル型のトランジスタである。トランジスタのゲートには、第2の高電源電位または接地電位が入力される。電源電圧が供給されないとき、トランジスタはゲートに接地電位が入力されてオフ状態を維持する。第2の高電源電位は、第1の高電源電位よりも高い。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を増加させることなく電源供給配線の電気抵抗を下降させることが可能な、TFTを有する半導体装置を提供することである。

【解決手段】表面を有する絶縁膜II4と、絶縁膜II4の表面上に形成され、かつチャネル領域TP2と、チャネル領域TP2を挟む1対のソース/ドレイン領域TP1,TP4とを含む半導体層と、ソース領域TP1に電源を供給するための電源供給配線TP1とを備えている。上記絶縁膜II4の表面には凹部TRが形成されている。上記電源供給配線TP1は、半導体層と同一の層から形成された層を含み、かつ絶縁膜II4の表面上に形成された第1の部分TP1Aと、凹部内に形成された第2の部分TP1Bとを有している。上記第2の部分TP1Bの底面全体が絶縁体II4で覆われている。

(もっと読む)

半導体記憶装置

【課題】不揮発性の記憶装置を有するCAMとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また、メモリセルの高密度化が可能な不揮発性の記憶装置を提供する。

【解決手段】酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参照回路を有し、参照回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索機能を可能にした半導体記憶装置である。

(もっと読む)

半導体記憶装置

【課題】SOI構造のDRAMの提供

【解決手段】

半導体基板1上に複数層の絶縁膜(2、3、4、5)が選択的に設けられ、絶縁膜5上より、絶縁膜5が設けられていない領域上に延在して選択的に半導体層(8、9、10)が設けられ、半導体層の一部9の全周囲にゲート絶縁膜16を介し、絶縁膜4上に包囲構造のゲート電極17が設けられ、ゲート電極に自己整合し、直下に空孔7を有する半導体層の一部10にドレイン領域(14、15)が、半導体層の一部8にソース領域(12、13)が設けられた構造のMIS電界効果トランジスタと、ソース領域12の側面に一部を接し、絶縁膜(3、5)中にトレンチが設けられ、トレンチの側面に電荷蓄積電極19が設けられ、電荷蓄積電極の側面及び上部にキャパシタ絶縁膜20を介してセルプレート電極21が設けられた構造のトレンチ型キャパシタと、により構成されたDRAM。

(もっと読む)

半導体素子および作製方法

【課題】ソフトエラー率を有意に低下させる半導体素子およびその作製方法に関する。

【解決手段】半導体基板(100)には、第1の型の不純物でドープされた第1ウェル領域(104)の下に第1の型の第1ドープ領域(102)がある。第1ウェル領域は、第1ドープ領域と電気的に接続されている。第1ウェル領域と第1ドープ領域(102)との間に分離領域(206)を形成する。分離領域は第2ウェル領域と電気接続されている。分離領域および第2ウェル領域は、第1の不純物型と反対の型の第2の不純物型でドープされている。前記方法はさらに、第1ウェル領域内および分離領域下に第2ドープ領域を形成する工程をさらに有し得る。第1の型の不純物を有する第3ドープ領域を、分離領域の上に形成することができる。

(もっと読む)

ジルコニウム酸化膜を有する半導体素子のキャパシタ及びその製造方法

【課題】70nm以下の金属配線を有する次世代DRAMで要求される容量および良好な漏れ電流特性を確保できるキャパシタ及びその製造方法を提供する。

【解決手段】キャパシタ形成方法は、ストレージ電極65を形成するステップと、ストレージ電極65の表面をプラズマ窒化66A処理するステップと、該表面がプラズマ窒化66A処理されたストレージ電極65上にZrO2薄膜67を蒸着するステップと、ZrO2薄膜67の表面をプラズマ窒化処理して、表面が窒化66BされたZrO2薄膜を形成するステップと、窒化66Bされた前記ZrO2薄膜上にプレート電極68を形成するステップとを含む。

(もっと読む)

スタティックランダムアクセスメモリ

【課題】第1の導電型の共通ウェルが形成された半導体基板と、前記半導体基板上の前記共通ウェルに行列状に配列されたメモリセルよりなり、列方向に整列して共通のビット線に接続される一群のメモリセルがメモリセルカラムを形成するメモリセルアレイからなるスタティックランダムアクセスメモリにおいて、隣接カラム群間のソフトエラーの伝搬を抑制する。

【解決手段】隣接する第1および第2のカラム群において、前記第1のカラム群CG1で選択される一のメモリセルカラムの第1導電型ウェルPW(01)と、第2カラム群CG2で同時に選択されるメモリセルカラムの第1導電型ウェルPW(05)は、いずれか一方が、共通ウェル11から、第2導電型の深いウェルDNW1により遮断されており、前記第2導電型の深いウェルDNW1は、行方向に測った場合の一つのカラム群の寸法を超えない寸法を有する。

(もっと読む)

半導体メモリセルおよびその製造方法

【課題】ストレージキャパシタが選択トランジスタ(AT)に接続されている半導体メモリセルの集積度を向上させながら、製造コストを低減できる半導体メモリセルおよびその製造方法を提供する。

【解決手段】ストレージキャパシタは、ソース領域Sまたはドレイン領域Dのための少なくとも1つのコンタクトホールにおいて、コンタクトホールキャパシタKKとして形成されている。このような半導体メモリセルは、特にコスト効率よく製造することができ、かつ高集積度を達成できる。

(もっと読む)

半導体記憶装置

【課題】SRAMのゲート配線形成にあたって、ゲート形状を複雑に変形させることなく転写及び加工マージンを確保する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1組及び第2組のドライバトランジスタ11、ロードトランジスタ12及びアクセストランジスタ13とを備えたメモリセルが半導体基板上に2次元配列されたメモリセルアレーと、複数のワードラインと、複数のビットラインと、第1組のドライバトランジスタ11とロードトランジスタ12とを接続し、直線状の側辺を有する長方形状の第1ゲート配線3aと、アクセストランジスタ13と接続され、直線状の側辺を有する長方形状の第2ゲート配線3cと、第1ゲート配線3aと、第2組のドライバトランジスタ11とロードトランジスタ12とを接続する第1コネクタ5aと、第2ゲート配線3cとワードラインとを接続する第2コネクタ5cとを備える。

(もっと読む)

半導体装置、および、その製造方法、電子機器

【課題】製造効率の向上、コストダウン、信頼性の向上、小型化を容易に実現させる。

【解決手段】各配線111h,211hにおいて、第1半導体チップ100および第2半導体チップ200の側端部にて露出した側面を、導電層401で被覆される。これにより、導電層401によって両配線111h,211hの間が電気的に接続させる。

(もっと読む)

ノードコンタクト構造体

【課題】ノードコンタクト構造体を有する半導体素子と、その製造方法を提供する。

【解決手段】半導体基板の上に形成されソース/ドレイン領域を有するバルクモストランジスタを備える。該バルクモストランジスタ上に層間絶縁膜が形成され、該層間絶縁膜上にソース/ドレイン領域を有する薄膜トランジスタが形成される。該バルクモストランジスタのソース/ドレイン領域上に半導体プラグが形成され、該半導体プラグは該層間絶縁膜の少なくとも一部を介して延長される。該薄膜トランジスタのソース/ドレイン領域及び該半導体プラグは金属プラグと接触し、該金属プラグは該層間絶縁膜の少なくとも一部を介して延長される。該半導体プラグ及び該金属プラグは多層のプラグを構成する。

(もっと読む)

1 - 20 / 115

[ Back to top ]