Fターム[5F083JA40]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 金属窒化物 (3,610)

Fターム[5F083JA40]に分類される特許

61 - 80 / 3,610

半導体装置の製造方法

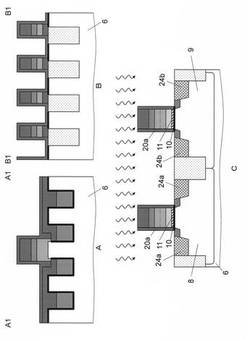

【課題】第1の領域において、第2の絶縁膜からゲート絶縁膜への酸化剤の侵入を防止する。第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去する。

【解決手段】半導体装置の製造方法では、基板の第1の領域には第1の積層体を形成し第2の領域には複数の第1の配線を形成する。第1の絶縁膜をマスクとして、第1の領域の主面に第1の不純物のイオン注入を施す。第1の積層体の側壁を覆いかつ複数の第1の配線間を埋設するように第2の絶縁膜を形成する。第2の絶縁膜をマスクとして、第1の領域の主面に第2の不純物のイオン注入を施す。第1のエッチングにより、第2の絶縁膜を第1の絶縁膜に対して選択的に除去した後、基板に熱処理を行う。

(もっと読む)

圧電体前駆体溶液、圧電セラミックスの製造方法、圧電素子の製造方法、液体噴射ヘッドの製造方法、及び、液体噴射装置の製造方法

【課題】少なくともBi、Ba、Fe及びTiを含む圧電体層を有する圧電素子、液体噴射ヘッド及び液体噴射装置の性能を向上させることにある。

【解決手段】少なくともビスマス、バリウム、鉄及びチタンを含むペロブスカイト型酸化物を形成するための圧電体前駆体溶液は、少なくとも、ビスマス塩、バリウム塩、鉄塩、並びに、チタンの部分アルコキシド(チタンにアルコキシ基及び該アルコキシ基以外の官能基が結合したチタン化合物)を含む。圧電セラミックスの製造方法は、前記圧電体前駆体溶液を塗布する工程と、該塗布した前駆体溶液を結晶化させてペロブスカイト型酸化物を含む圧電セラミックスを形成する工程と、を備える。圧電素子の製造方法は、前記圧電セラミックスに電極を形成する工程を備える。液体噴射ヘッドの製造方法は、前記圧電素子の製造方法により圧電素子を形成する工程を備える。

(もっと読む)

半導体装置およびその作製方法

【課題】ノーマリーオフの電気特性を有し、オン電流の高い、酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを用いた高速動作が可能な半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳して設けられたゲート電極と、少なくともゲート電極を覆って設けられた、開口部を有する層間絶縁膜と、層間絶縁膜上に設けられ、開口部を介して酸化物半導体膜と接する配線と、を有し、少なくとも酸化物半導体膜と配線とが接する領域の、下地絶縁膜および酸化物半導体膜の間に、絶縁膜および絶縁膜上に設けられたバッファ層を有する半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】放射線耐性能力をさらに向上することができる半導体装置を提供する。

【解決手段】半導体基板1の上方に形成された第1絶縁膜12と、第1絶縁膜12の上方に形成され、下部電極17と上部電極19に挟まれる強誘電体膜18を有するキャパシタQと、キャパシタの上に形成される第2絶縁膜26と、を有し、第1絶縁膜12と下部電極17の間に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第3絶縁膜16、38と、

を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子上の配線層の設計自由度に優れた半導体装置を提供する。

【解決手段】半導体装置は、基板、層間絶縁層、第1トランジスタ、多層配線層、容量素子、金属配線、及び第1コンタクトを備える。基板1上には、層間絶縁層4、5が設けられている。第1トランジスタ3aは、半導体基板1に設けられており、層間絶縁層内に埋め込されている。第1トランジスタは、少なくともゲート電極32及び拡散層を有する。層間絶縁層上には、多層配線層が設けられている。容量素子19は、多層配線層内に設けられている。金属配線(ゲート裏打ち配線)30は、ゲート電極32の上面と接しており、層間絶縁層4内に埋設されている。第1コンタクト10aは、第1トランジスタ3aの拡散層に接続しており、層間絶縁層4内に埋設される。金属配線(ゲート裏打ち配線)30は、第1コンタクト10aと同じ材料で構成されている。

(もっと読む)

Ru含有酸素拡散バリア

【課題】メモリデバイス中の酸素拡散バリアとしてRuおよび/またはRuO2を選択的に形成する方法と、そのようなRu系拡散バリアを有するメモリデバイスを提供する。

【解決手段】MIMキャパシタ構造を形成する方法は、導電性の下部電極プラグ33を露出させるリセスを備えたベース構造を得る工程と、ベース構造材料に比較した下部電極プラグ上へのRu成長の培養時間の違いに基づいて、下部電極プラグ上にRu50を選択成長させる工程と、選択成長したRu50を酸化する工程と、酸化したRu50の上にRu含有下部電極60を堆積する工程と、Ru含有下部電極60の上に誘電体層70を形成する工程と、誘電体層70の上に導電性の上部電極71を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの上部電極上に形成される充填膜の膜厚均一性を向上させる。

【解決手段】半導体基板1と、半導体基板1上に形成された下部電極14と、下部電極14上に形成された容量絶縁膜15と、容量絶縁膜15上に形成された上部電極16と、上部電極16の表面に形成された表面改質層と、表面改質層上に形成された充填膜18を有する半導体装置100。

(もっと読む)

圧電セラミックスの製造方法、圧電素子の製造方法、液体噴射ヘッドの製造方法、及び、液体噴射装置の製造方法

【課題】少なくともBi、Ba、Fe及びTiを含む圧電体層を有する圧電素子、液体噴射ヘッド及び液体噴射装置の性能を向上させる製造方法を提供する。

【解決手段】少なくともBi、Ba、Fe及びTiを含む前駆体溶液であって、水溶液とした場合にpHが7以上である前駆体溶液31を下電極20上に塗布し、塗布した前駆体溶液31を結晶化させてペロブスカイト型酸化物を含む圧電セラミックスを形成する。圧電素子の製造方法は、圧電セラミックス30に電極を形成する工程を備える。液体噴射ヘッドの製造方法は、圧電素子の製造方法により圧電素子を形成する工程を備える。

(もっと読む)

記憶装置及びその製造方法

【課題】信頼性が高い記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る記憶装置は、下部電極層と、前記下部電極層上に設けられた絶縁性の芯材層と、前記芯材層上に設けられ、前記芯材層の側面上には設けられていない上部電極層と、前記芯材層の側面上に設けられ、前記下部電極層及び前記上部電極層に接し、複数の微小導電体が隙間を介して集合した抵抗変化層と、を備える。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層の溝に埋め込まれた電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設ける。チャネル形成領域は、サイドウォールを側壁に有するゲート電極層と重なる位置に形成される。溝は、深い領域と浅い領域を有し、サイドウォールは、浅い領域と重なり、配線との接続は、深い領域と重なる。

(もっと読む)

半導体装置及びその製造方法

【課題】記憶素子の実効面積の減少を抑制する半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法は、基板上に第1導電プラグを形成する工程と、基板上に第1導電プラグの上面を覆う可変抵抗膜を形成する工程と、基板上に第1導電プラグの上面を覆う第1絶縁膜を形成する工程と、第1絶縁膜のうち第1導電プラグ上の部分を除去して、第1絶縁膜に孔部を形成する工程と、第1絶縁膜の上面から孔部内にわたって第1導電膜を形成して孔部内を埋め込むことで、孔部内で可変抵抗膜に接触し、かつ、可変抵抗膜を介して第1導電プラグに電気的に接続するように第1導電膜を形成する工程と、を含む。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタ、ダイオード等の半導体用途に好適な材料を提供する。

【解決手段】ジルコニウムを含ませた酸化物半導体材料は結晶化しやすい材料とすることができ、成膜直後において、結晶構造を有する酸化物半導体膜を形成することができる。従って、酸化物半導体膜の成膜後の加熱処理を省略することができるため、量産に適したプロセスである。具体的には、少なくともインジウムと亜鉛を含む酸化物半導体材料に、4族元素の一つであるジルコニウムを含ませる。少なくともインジウムと亜鉛を含む酸化物半導体材料にジルコニウムを含ませた酸化物半導体材料膜(InZrZnOX膜)を提供する。

(もっと読む)

可変抵抗素子を備える不揮発性メモリセル及び不揮発性半導体記憶装置

【課題】 検知マージンを大きくして可変抵抗素子の抵抗状態をより正しく検知することができ、且つ、面積低減によりコスト抑制を図ることができる不揮発性メモリセル及び不揮発性半導体記憶装置を提供する。

【解決手段】 第1電極と第2電極の間に第1可変抵抗体R1を挟持してなる第1可変抵抗素子RD1と、第3電極と第4電極の間に第2可変抵抗体R2を挟持してなる第2可変抵抗素子RD2と、ドレイン端子が、第2電極と第4電極に、ゲート端子がワードラインに、ソース端子がコモンラインCLに夫々接続されたトランジスタTと、を備え、第1電極材料の仕事関数が第2電極材料の仕事関数より大きい値に、第3電極材料の仕事関数が第4電極材料の仕事関数より小さい値に設定されるか、または、第1電極材料の仕事関数が第2電極材料の仕事関数より小さい値に、第3電極材料の仕事関数が第4電極材料の仕事関数より大きい値に設定される。

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】酸素不足度の異なる遷移金属酸化物層を積層して抵抗変化層に用いた不揮発性記憶装置において、素子特性のばらつきを従来よりもさらに抑制する。

【解決手段】第1電極層を形成する工程(A)と、第1電極層の上に酸素不足型の遷移金属酸化物で構成される第1抵抗変化層を形成する工程(B)と、第1抵抗変化層の上端面を液体の酸化剤で化学的に酸化処理して中間酸化層を形成する工程(C)と、中間酸化層をさらに酸化し、第1抵抗変化層の上に第1抵抗変化層を構成する遷移金属酸化物よりも酸素不足度が少ない遷移金属酸化物で構成される第2抵抗変化層を形成する工程(D)と、第2抵抗変化層の上に、第2電極層を形成する工程(E)と、を有する、不揮発性記憶装置の製造方法。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を提供する。また、バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を具備する半導体装置を提供する。

【解決手段】インジウム、ランタン、亜鉛及び酸素を有する結晶構造の酸化物半導体膜とする。また、当該結晶構造において、ランタンは酸素が6配位した構造とし、インジウムは酸素が5配位した構造とする。酸化物半導体膜の結晶構造中にランタンを用いることで、インジウム、ガリウム、亜鉛及び酸素を有する結晶構造の酸化物半導体膜よりもバンドギャップが大きく、結合エネルギーを大きくした酸化物半導体膜とすることができる。また、該酸化物半導体膜を用いた半導体装置の特性を向上させることができる。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】 可変抵抗素子への電圧印加極性が異なる2種類の書き込み動作後の各ベリファイ動作を夫々低消費電力且つ高速に実行可能な半導体記憶装置を提供する。

【解決手段】 書き込み回路22が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の電気抵抗を低抵抗化させるセット動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の電気抵抗を高抵抗化させるリセット動作を夫々実行可能に構成され、読み出し回路21が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第1読み出し動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第2読み出し動作を夫々実行可能に構成されている。

(もっと読む)

電子機器

【課題】非接触でデータの送受信が可能な半導体装置は、鉄道乗車カードや電子マネーカ

ードなどの一部では普及しているが、さらなる普及のためには、安価な半導体装置を提供

することが急務の課題であった。上記の実情を鑑み、単純な構造のメモリを含む半導体装

置を提供して、安価な半導体装置及びその作製方法の提供を課題とする。

【解決手段】有機化合物を含む層を有するメモリとし、メモリ素子部に設けるTFTのソ

ース電極またはドレイン電極をエッチングにより加工し、メモリのビット線を構成する導

電層とする。

(もっと読む)

半導体装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

61 - 80 / 3,610

[ Back to top ]