Fターム[5F083JA45]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 酸化物導電体 (2,345) | 複酸化物 (752) | ABO3(ペロブスカイト)型 (433)

Fターム[5F083JA45]に分類される特許

1 - 20 / 433

半導体装置の製造方法

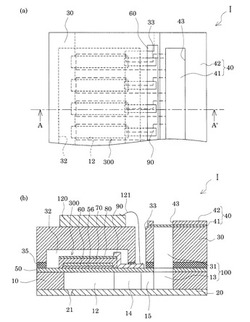

液体噴射ヘッド及び液体噴射装置並びに圧電素子

【課題】環境負荷が小さく、歪量が大きい液体噴射ヘッド、液体噴射装置及び圧電素子を提供する。

【解決手段】圧電体層70と圧電体層70に設けられた電極60,80とを具備する圧電素子300を備え、圧電体層70は、ビスマス、鉄、バリウム及びチタンを含みペロブスカイト構造を有する複合酸化物からなり、圧電体層70に駆動電圧Vaを印加したときの変位量をZmax、その後印加電圧を0Vにしたときの変位量をZ0としたとき、(Zmax−Z0)/Vaが70pm/V以上且つ比誘電率が700以下である。

(もっと読む)

機能性デバイスの製造方法並びに薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより機能性固体材料となる機能性液体材料を準備する第1工程と、基材上に機能性液体材料を塗布することにより、機能性固体材料の前駆体組成物層を形成する第2工程と、前駆体組成物層を80℃〜200℃の範囲内にある第1温度に加熱することにより、前駆体組成物層の流動性を予め低くしておく第3工程と、前駆体組成物層を80℃〜300℃の範囲内にある第2温度に加熱した状態で前駆体組成物層に対して型押し加工を施すことにより、前駆体組成物層に型押し構造を形成する第4工程と、前駆体組成物層を第2温度よりも高い第3温度で熱処理することにより、前駆体組成物層から機能性固体材料層を形成する第5工程とをこの順序で含む機能性デバイスの製造方法。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置のスイッチング耐久性の向上を図る。

【解決手段】実施形態によれば、半導体記憶装置は、複数のセルアレイブロックと、制御回路とを備えている。制御回路は、選択ビット線を0ボルトにし、選択ワード線に0ボルトよりも高い第1の電位を与え、非選択ワード線に0ボルトよりも高く前記第1の電位よりも低い第2の電位を与え、選択セルアレイブロックに第1の方向で隣接し選択ビット線を選択セルアレイブロックと共有する隣接セルアレイブロックにおける、選択ビット線に隣接する非選択ビット線に0ボルト以上で前記第2の電位よりも低い第3の電位を与え、前記第3の電位が与えられた非選択ビット線以外の他の非選択ビット線に前記第2の電位を与えて、選択メモリセルの抵抗変化膜の抵抗状態を変化させる。

(もっと読む)

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

機能性デバイスの製造方法及び機能性デバイスの製造装置

【課題】機能性デバイスの高性能化、又はそのような機能性デバイスの製造プロセスの簡素化と省エネルギー化を提供する。

【解決手段】機能性デバイスの製造方法は、型押し工程と、機能性固体材料層形成工程を含む。型押し工程では、機能性固体材料前駆体溶液を出発材とする機能性固体材料前駆体層に対して型押し構造を形成する型を押圧している間の少なくとも一部の時間においてその機能性固体材料前駆体層に対して熱を供給する熱源の第1温度がその機能性固体材料前駆体層の第2温度よりも高くなるように、その機能性固体材料前駆体層に対して型押し加工を施す。また、機能性固体材料層形成工程では、型押し工程の後、酸素含有雰囲気中において、機能性固体材料前駆体層を前述の第1温度よりも高い第3温度で熱処理することにより、機能性固体材料前駆体層から機能性固体材料層を形成する。

(もっと読む)

Ru含有酸素拡散バリア

【課題】メモリデバイス中の酸素拡散バリアとしてRuおよび/またはRuO2を選択的に形成する方法と、そのようなRu系拡散バリアを有するメモリデバイスを提供する。

【解決手段】MIMキャパシタ構造を形成する方法は、導電性の下部電極プラグ33を露出させるリセスを備えたベース構造を得る工程と、ベース構造材料に比較した下部電極プラグ上へのRu成長の培養時間の違いに基づいて、下部電極プラグ上にRu50を選択成長させる工程と、選択成長したRu50を酸化する工程と、酸化したRu50の上にRu含有下部電極60を堆積する工程と、Ru含有下部電極60の上に誘電体層70を形成する工程と、誘電体層70の上に導電性の上部電極71を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】放射線耐性能力をさらに向上することができる半導体装置を提供する。

【解決手段】半導体基板1の上方に形成された第1絶縁膜12と、第1絶縁膜12の上方に形成され、下部電極17と上部電極19に挟まれる強誘電体膜18を有するキャパシタQと、キャパシタの上に形成される第2絶縁膜26と、を有し、第1絶縁膜12と下部電極17の間に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第3絶縁膜16、38と、

を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を劣化させることなく、半導体材料または絶縁膜の結晶特性を改善することができる低温アニールを用いた半導体装置の製造方法、並びに、このような低温アニールに適した半導体装置を提供する。

【解決手段】本実施形態による半導体装置は、半導体基板の上方に設けられた金属からなる下部電極と、下部電極の上方に設けられた金属からなる上部電極と、下部電極と上部電極との間に設けられた結晶層とを備える。下部電極および上部電極の各膜厚は、結晶層の結晶化に用いられるマイクロ波の周波数に対応する表皮効果における表皮層よりも薄い。

(もっと読む)

可変抵抗絶縁層を用いたメモリ素子及びそれを有するプロセッサシステム

【課題】可変抵抗材料を用いて形成されるランダムアクセスメモリ装置を提供する。

【解決手段】可変抵抗メモリ装置301において、望ましい円錐状に形造された下部電極308は、下部電極308の頂点のところにおける絶縁材料312の厚さが最も薄く、下部電極308の頂点のところにおける電界が最大であることを確保する。電極308、310の配置およびメモリ素子の構造はメモリ装置内に安定で確実に導電路を作り出し、かつ、スイッチングとメモリ特性を再生可能にする。

(もっと読む)

強誘電体素子、インクジェット式記録ヘッド及びインクジェット式画像形成装置

【課題】エッチング残渣が少なく信頼性が良好であり、かつリーク電流を抑制することができる強誘電体素子を提供する。

【解決手段】シリコン基板10の上に順に、振動板11、下部電極20、強誘電体層30、上部電極40を形成し、強誘電体層30の側面の傾斜角はθ2=30°、上部電極40の側面の傾斜角はθ1=30°としている。これにより、エッチングガスやプラズマ粒子の衝突角度が平面に近づき、傾斜面でのエッチング残渣の除去率が向上する。

(もっと読む)

パターン形成用基板、圧電アクチュエータ製造方法、圧電アクチュエータ、液滴吐出ヘッド、および、液滴吐出装置

【課題】流動体を付着させて熱処理を行う工程を繰り返し行うことにより微細パターンの膜を所望の膜厚で精密に作製可能とするパターン形成用基板と、パターン形成用基板を用いた圧電アクチュエータの製造方法を提供する。

【解決手段】所定の流動体を特定領域に付着させて熱処理を行うことによりパターン化された膜を形成するためのパターン形成用基板10で、特定領域を親和性とし、それ以外の領域を非親和性とする表面改質をおこなう。パターン形成用基板10の表面改質処理対象となる金属膜はPt膜53を積層し、基体として、Ti,Ta,Zr,V,Nb,Mo,Wから選ばれる少なくとも1つの金属元素、酸素元素および炭素元素から構成されるMOC膜52を用いる。

(もっと読む)

ニッケル酸ランタン膜形成用組成物の製造方法、ニッケル酸ランタン膜の製造方法、及び圧電素子の製造方法

【課題】特殊な環境が不要で短時間且つ低コストでニッケル酸ランタン膜形成用組成物を製造することができるニッケル酸ランタン膜形成用組成物の製造方法、ニッケル酸ランタン膜の製造方法、及び圧電素子の製造方法を提供する。

【解決手段】少なくとも酢酸ランタン、酢酸ニッケル、酢酸、及び水を混合して混合溶液を得た後、混合溶液を加熱する。

(もっと読む)

半導体記憶装置の製造方法

【課題】クロスポイント型セル構造の配線構造を正確に形成する。

【解決手段】

第1の配線を形成する第1配線層及びメモリセルを形成するメモリセル層を順次積層してなる第1積層構造を第1方向に延びるストライプ状にエッチングする。このとき、第1ストライプ部の側部から第2方向に突出する第1フック部を形成する。そして、第1積層構造の上層に第2積層構造を形成し、この第2積層構造を2方向に延びるストライプ状にエッチングする。このとき、第2ストライプ部の側部から第1方向に突出する第2フック部を形成する。上記を所定数繰り返す。そして、第1又は第2フックの側面に接するコンタクトプラグを形成する。第2フック部が形成されるべき領域では、第1積層構造を除去し、また、第1フック部が形成されるべき領域では、第2積層構造を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】セキュリティを高めるための半導体装置を提供する。

【解決手段】第1トランジスタ4a、および第1トランジスタ4aに接続される第1キャパシタ4bを有する第1メモリセル4を含む第1メモリセルアレイ2と、第1トランジスタ4aよりもオフ電流が高い第2トランジスタ5a、および第2トランジスタ5aに接続される第2キャパシタ5bを有する第2メモリセル5を含む第2メモリセルアレイ3と、を有する。

(もっと読む)

圧電デバイスおよびその製造方法

【課題】圧電体の構成金属の拡散による特性低下を回避するとともに、圧電体の形成時の膜のはがれを回避し、さらに、圧電体の結晶性および平坦性を向上させる圧電デバイスおよびその製造方法を提供する。

【解決手段】圧電デバイス1の基板11上には、電極層23を含む下地層13を介して、圧電体14が形成される。下地層13は、第1の層21と、第2の層22とを含んでいる。第1の層21は、金属酸化物または金属窒化物からなる。第2の層22は、第1の層21の金属酸化物の構成金属と同じ金属、または金属窒化物の構成金属と同じ金属からなる。

(もっと読む)

強誘電体キャパシタの製造方法及び強誘電体キャパシタ

【課題】強誘電体膜の表面に現れた窪みを、強誘電体材料で効率的に埋め込むことが可能な強誘電体キャパシタの製造方法を提供する。

【解決手段】基板10の上に第1導電膜11を形成する。第1導電膜11の上に、表面に複数の凹部15が形成された第1強誘電体膜12を形成する。第1強誘電体膜12の表面の凹部15を埋め込むように、第1強誘電体膜12の上に、原子層堆積法により第2強誘電体膜13を形成する。第2強誘電体膜13の上に、第2導電膜17を形成する。

(もっと読む)

抵抗メモリ素子および関連する制御方法

【課題】電圧制御されたプログラム可能な抵抗層を有する抵抗メモリ素子とプログラミング方法を提供する。

【解決手段】参照面に平行な面に横たわり、参照面上の垂直な投影で上部電極投影を有する上部電極素子12と、参照面に平行な面に横たわり、参照面上の垂直な投影で下部電極投影を有する下部電極素子14と、上部電極素子12と下部電極素子14との間に挿入された可変性の抵抗率を有する活性層16を含む抵抗メモリ素子10において、上部電極投影と下部電極投影との間にオーバーラップ領域L3があり、オーバーラップ領域L3は少なくとも上部電極投影のコーナーおよび/または少なくとも下部電極投影のコーナーを含み、オーバーラップ領域L3の面積は、参照面上の、上部電極素子12と下部電極素子14の全投影面積の10%以下を構成する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】可変抵抗素子のデータ保持特性を向上させることのできる半導体記憶装置及びその製造方法を提供する。

【解決手段】一の実施の形態に係る半導体記憶装置は、基板上に配置された複数の第1配線と、第1配線と交差するように配置され、第1配線と基板との間に位置する複数の第2配線と、第1配線と第2配線との各交差部に配置され、電流整流素子及び可変抵抗素子を直列接続してなる第1のメモリセルを含む第1のメモリセルアレイとを備える。第1のメモリセルの可変抵抗素子は、第1の金属材料の酸化物により形成された第1記録層と、第1の金属材料により形成され、且つ、第1記録層と接するように形成された第2記録層とを有する。第2記録層は第1記録層に比べ第1配線に近い側に設けられる。

(もっと読む)

強誘電体膜の製造方法とそれを用いた強誘電体素子

【課題】分極特性を向上させる強誘電体素子とその製造方法を提供する。

【解決手段】強誘電体素子は、基板1と、この基板1上に形成された拡散防止層2と、拡散防止層2の上に形成された下部電極層3と、下部電極層3の上に形成された強誘電体膜4と、強誘電体膜4の上に形成された上部電極層5とから構成されている。強誘電体膜4の化学溶液法を用いた製造方法は、基板1の主面に下部電極層3を形成する下部電極形成工程と、この下部電極層3上に強誘電体4の前駆体膜を形成する前駆体形成工程と、前駆体膜を加熱して結晶化させることで強誘電体膜4を形成する結晶化工程と、強誘電体膜4を一定の温度まで冷却する冷却工程と、を少なくとも含み、結晶化工程において、前駆体膜に応力を印加した後に結晶化させる。

(もっと読む)

1 - 20 / 433

[ Back to top ]