Fターム[5F083LA25]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | チップレイアウト (365)

Fターム[5F083LA25]の下位に属するFターム

周辺回路がチップ4周辺部に配置 (27)

周辺回路がチップ3周辺部に配置 (15)

周辺回路がチップ2周辺部に配置 (25)

周辺回路が中央部に配置 (38)

周辺回路が十字に配置 (50)

Fターム[5F083LA25]に分類される特許

1 - 20 / 210

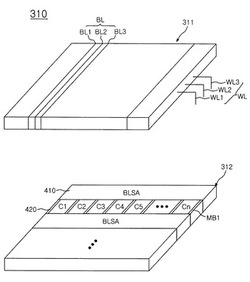

半導体装置

【課題】複数個のメモリチップが積層された構造を有する半導体装置の信頼性を向上させる。

【解決手段】半導体装置は、複数のビットラインと複数のワードラインとの交差点に複数個のメモリセルが配列される複数個のメモリチップが垂直方向に積層され、いずれか一つのメモリチップには複数個のメモリチップの各々に配列された複数のビットラインと連結されアクティブにされるメモリチップのビットラインをイネーブルさせるためのビットラインセンスアンプと、複数個のメモリチップの各々に配列された複数のワードラインと連結されアクティブされるメモリチップのワードラインをイネーブルさせるためのサブワードラインドライバを含み、ビットラインセンスアンプとサブワードラインドライバがいずれか一つのメモリチップに備わる。

(もっと読む)

半導体集積回路及びその設計方法

【課題】チップサイズを増大することなく、キャパシタの容量を増やすことができる半導体集積回路を提供する。

【解決手段】半導体基板10上にメインブロック11と周辺ブロック12とが混載された半導体集積回路において、半導体基板10上のメインブロック11に形成され、第1のトレンチキャパシタを有するメイン回路と、半導体基板10上の周辺ブロック12に形成され、第2のトレンチキャパシタを有するアナログ回路とを備える。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ワード線抵抗を低減し、かつ、周辺回路のトランジスタの特性変化を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、複数のメモリセルと、周辺回路とを備える。メモリセルは、半導体基板の上方に設けられたフローティングゲートと、フローティングゲート上に設けられたゲート間絶縁膜と、ゲート間絶縁膜上に設けられたコントロールゲートとを含む。周辺回路は、互いに電気的に接続されたフローティングゲートおよびコントロールゲートと、少なくともフローティングゲートとコントロールゲートとの間の電気的接触部分に設けられ該フローティングゲートと該コントロールゲートとの間の電気的接続を妨げない絶縁薄膜とを含むトランジスタを含む。複数のメモリセルは、コントロールゲート内に絶縁薄膜を含まない。メモリセルおよび周辺回路において、コントロールゲートの少なくとも上部はシリサイド化されている。

(もっと読む)

半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

(もっと読む)

メモリ装置

【課題】大容量化が容易であり、高収率且つ高信頼性を有する半導体メモリ装置が提供される。

【解決手段】本発明に従うメモリ装置は、記憶素子と前記記憶素子にデータを書き込むか、又は読み出す周辺回路を含む第1半導体チップ、及び外部と前記第1半導体チップとの間で交換されるデータ又は信号の入出力機能を遂行する第2半導体チップを含み、本発明のその他の特徴に従うメモリ装置は、外部とデータ又は信号を交換するための入出力回路チップ、及び各々前記入出力回路チップから提供される信号に応答して前記データを格納するか、或いは内部に格納されたデータを読み出して前記入出力回路チップへ出力する、垂直方向に積層される複数のコアチップを含む。

(もっと読む)

半導体記憶装置

【課題】比較的小振幅な信号が伝送される第1の信号線対で発生するカップリングノイズを低減しつつ、該第1の信号線対と直交する方向に異なる配線層で配置される、第1の信号線対よりも振幅が大きい信号が伝送される第2の信号線毎の信号遅延量の差異を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、メモリアレイ上で配線される第1の振幅信号が伝送される複数の第1の信号線対と、該第1の信号線対と直交する方向に異なる配線層で配置される複数の第2の信号線とを有する。第1の信号線対は、メモリマットの列毎に配置され、メモリマットの列方向において、それぞれ所定の一定間隔で交差される。また、第1の信号線対の交差部位は第2の信号線の配線方向におけるメモリマットの列毎にずらして配置される。

(もっと読む)

半導体記憶装置の製造方法

【課題】製造工程を簡略化出来る半導体記憶装置の製造方法を提供すること。

【解決手段】実施形態の半導体記憶装置の製造方法は、第1配線層42及び前記第1メモリセル層43〜47をパターニングすることにより、第1方向D1に沿ったストライプ形状の第1構造を第1領域20に形成し、第2構造DM1を第2領域21に形成することと、第1構造及び前記第2構造DM1上に順次形成した第2配線層54及び第2メモリセル層55〜59をパターニングすることにより、第1方向D1と異なる第2方向D2に沿ったストライプ形状を有し、且つ第2領域21における第2構造DM1直上の領域で折り返すパターンを有する第3構造を第1領域20に形成することと、第3構造の折り返す部分における第2配線層54及び第2メモリセル層55〜59、並びにその直下に位置する第1メモリセル層43〜47を除去することとを具備する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子埋設用凹部上端部の肩落ちによるキャパシタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】半導体装置は、保護層80は、凹部(孔23)の上端部の周囲に設けられている。この保護層80は、保護層80と同一層に位置しており、論理回路領域に位置している多層配線層を構成する絶縁層よりも誘電率が高い材料で構成されており、機械強度に優れた部材となる。これにより、凹部(孔23)上端部の肩落ちを抑制し、キャパシタ高さのバラツキを抑制する。

(もっと読む)

抵抗変化型メモリデバイスおよびその駆動方法

【課題】リファレンスセルの抵抗状態に応じて、読み出し電流を設定する構成で、誤書き込みによる抵抗の変化が発生することなく、より信頼性の高いリファレンス電流を得ることが可能な抵抗変化型メモリデバイスおよびその駆動方法を提供する。

【解決手段】素子両端に極性の異なる信号を印加することで可逆的に記憶素子の抵抗値が変化するメインメモリセルを含むメモリアレイ部と、素子両端に極性の異なる信号を印加することで可逆的に抵抗値が変化する記憶素子を含み、メインメモリセルのデータを識別するために必要な参照電流を発生させるリファレンスセルを含むリファレンスセル部と、を有し、リファレンスセルの抵抗状態に応じた参照電流の印加電流の向きが設定されている。

(もっと読む)

半導体記憶装置、および、ビット線の充電方法

【課題】低消費電力モードから通常動作モードへの復帰時におけるビット線の充電時間を適切に設定することで、復帰動作で消費される電力を低減する。

【解決手段】半導体記憶装置10は、複数のビット線2a,2b…のそれぞれを充電する充電回路4と、帰還経路5aの配線にダミービット線3が用いられているリングオシレータ5と、リングオシレータ5の発振回数が、複数のビット線2a,2b…の数に基づいて設定された所定の回数に達すると、検出信号を出力するカウンタ6と、低消費電力モードから通常動作モードへの復帰を指示する復帰信号に応じて、充電回路4による複数のビット線2a,2b…の充電を開始させるとともにリングオシレータ5の発振を開始させ、カウンタ6から出力された検出信号に応じて、充電回路4による複数のビット線2a,2b…の充電を終了させる制御回路7と、を有する。

(もっと読む)

半導体装置

【課題】補償容量としてのキャパシタを備えた補償容量領域において、その容量値を上げずにその面積を大きくして、製造工程時のキャパシタの剥がれを防止する。

【解決手段】第1の領域AR1に設けられたキャパシタ23の下部電極の各々には、端子A(M1)からVPERI電圧が供給されている。第2の領域AR2に設けられたキャパシタ23の下部電極の各々には、端子B(M1)からVSS電圧が供給されている。第3の領域AR3に設けられたキャパシタ23の下部電極の各々は、端子C(M1)から1/2VPERI電圧が供給されている。プレート24は、1/2VPERI電圧を第1〜3の領域AR1〜AR3のキャパシタ23の各上部電極に共通に供給している。第3の領域AR3は、各々の下部電極及び上部電極に同一電圧(1/2VPERI)が供給されるため容量に電荷が溜まることがない。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の一部にメタルゲート電極を有するMISEFTにおいて、メタルゲート電極を構成するグレインの配向性のばらつきに起因するMISFETのしきい値電圧のばらつきを小さくする。

【解決手段】メタルゲート電極4a、4bに炭素(C)を導入することにより、メタルゲート電極4a、4b内のグレインの粒径が大きくなることを防ぎ、メタルゲート電極4a、4bの中に多数の小さいグレインを形成することにより、グレインの配向性を均一化し、ゲート電極の仕事関数のばらつきを低減する。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域における上記プラグと、活性領域の外部における上記プラグとの双方を有する、微細化された半導体装置において、枠付け絶縁膜を確実に形成し、かつ導電性などの機能を最適化することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に形成される活性領域と、平面視における活性領域の周辺に形成されるゲート接続領域と、活性領域上に形成される複数の第1のトランジスタTGに挟まれる領域に形成される、第1のトランジスタTGと第1のトランジスタTGよりも上側の層とを電気的に接続するための第1の接続層CTと、ゲート接続領域上に形成される第2のトランジスタTGと、第2のトランジスタTGよりも上側の層とを電気的に接続するための第2の接続層とを備えている。上記第1の接続層CTには第1の導電部PP1aと第2の導電部PP2aとを含み、第2の接続層SNCには第3の導電部PP2bを含む。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

半導体記憶装置の製造方法

【課題】記憶部と論理部とを有する半導体記憶装置において、電気的特性のばらつき及び信頼性の低下を回避できるようにする。

【解決手段】半導体記憶装置の製造方法は、記憶部300及び論理部301を有する基板101の上に、記憶部ゲート絶縁膜102及び第1の導電膜141を形成する工程よりも後に、第1の導電膜141及び記憶部ゲート絶縁膜102における論理部301の上に形成された部分を除去する。論理部ゲート絶縁膜111及び第2の導電膜147を形成する工程よりも後に記憶部300において第1の導電膜141を露出する。

(もっと読む)

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

記憶装置

【課題】記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

【解決手段】基板に設けられた駆動回路と、駆動回路上に設けられ、駆動回路によって駆動される複数のメモリセルアレイと、を有し、複数のメモリセルアレイはそれぞれ複数のメモリセルを有し、複数のメモリセルはそれぞれ、酸化物半導体層と重畳する第1のゲート電極と、を有する第1のトランジスタと、ソース電極又はドレイン電極と、第1のゲート絶縁層と、導電層と、を有する容量素子と、を有し、複数のメモリセルアレイは重ねて配置される。こうして、記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

(もっと読む)

1 - 20 / 210

[ Back to top ]