Fターム[5F083MA16]の内容

Fターム[5F083MA16]に分類される特許

101 - 120 / 1,403

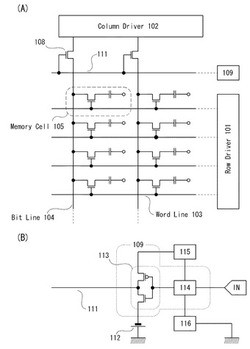

半導体装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線にビット線制御トランジスタを直列に挿入し、そのゲートの最低電位は十分な負の値となるようにする。ビット線制御トランジスタのゲートは電池等に接続するビット線制御回路に接続される。ビット線の最低電位はワード線の最低電位よりも高くなるようにする。外部からの電源が切れた際には、ビット線はビット線制御トランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。あるいは外部電源遮断時にワード線の電位を十分な負の電位とできるような回路を設けてもよい。

(もっと読む)

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼でき、非常に小型の3次元集積回路メモリ用の構造を低い製造コストで提供する。

【解決手段】3次元アレイは第1の端部と第2の端部を含む2つの端部を有し、第1の端部と第2の端部の一方はビット線BLに接続され、第1の端部と第2の端部の他方はソース線CSLに接続される不揮発性メモリセルのNANDストリングのスタック1412、1413、1414と、ビット線BL及びソース線SLの一方をメモリセルのストリング1412、1413、1414に接続させるダイオード1492を有する。

(もっと読む)

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】スループットを低下させずに異なるメモリセルの誘電体膜とキャパシタの誘電体膜を同時に形成するための半導体装置の製造方法を提供する。

【解決手段】第1酸化膜18、窒化膜19、第2酸化膜20を順に形成した第1の誘電体膜を第1の半導体膜16上に形成する工程と、第1領域I内の第1の誘電体膜21をエッチングする工程と、第1領域Iの半導体基板1の表面に第3酸化膜25を形成する工程と、第1領域VI及び第2領域IIIに開口部28a、28bを有し、さらに第3領域II内の第1の誘電体膜21を覆う形状を有するマスク28を半導体基板1の上方に形成する工程と、マスク28の開口部28a、28bを通して、第1領域VI内の前記第3酸化膜25と前記第2領域III内の第1の誘電体膜21の第2酸化膜20を同時にエッチングする工程を含む。

(もっと読む)

半導体メモリ装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線の一端にバックゲートを有するトランジスタ(バックゲートトランジスタ)を直列に挿入し、そのバックゲートの電位は常に十分な負の値となるようにする。また、ビット線の最低電位はワード線の最低電位よりも高くなるようにする。電源が切れた際には、ビット線はバックゲートトランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

半導体装置および半導体装置の制御方法

【課題】信頼性を確保しつつ、高速動作を実現することができる半導体装置を提供する。

【解決手段】抵抗変化素子10を有するメモリセル11と、メモリセル11に印加する電圧を制御する制御部80と、を備え、抵抗変化素子10は、第1の金属材料を含有する下部電極14と、第2の金属材料を含有する上部電極16と、酸素を含有する絶縁膜12と、を有しており、第1の金属材料は、第2の金属材料よりも規格化酸化物生成エネルギーが大きく、制御部80は、絶縁膜12の抵抗値を高抵抗化させる動作時および低抵抗化させる動作時において上部電極16に正電圧を印加し、絶縁膜12の抵抗値を読み出す動作時において下部電極14に正電圧を印加する。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリの製造プロセスにおけるPEP数を削減する。

【解決手段】実施形態に係わる抵抗変化メモリは、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される複数の抵抗変化素子MTJ及び複数のビアV0と、複数の抵抗変化素子MTJの側壁上に配置される複数の側壁絶縁層PLとを備える。複数の抵抗変化素子MTJは、一定ピッチで格子状に配置され、複数の側壁絶縁層PLの側壁に垂直な方向の厚さは、複数の側壁絶縁層PLが互いに部分的に接触し、複数の側壁絶縁層PL間に複数のホールが形成される値に設定される。複数のビアV0は、これら複数のホール内に配置される。

(もっと読む)

半導体装置

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体メモリ装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に、書き込みトランジスタのソースおよび読み出しトランジスタのソースをビット線に、読み出しトランジスタのドレインを読み出しワード線に接続する。ここで、書き込みトランジスタと読み出しトランジスタの導電型を異なるものとする。集積度を高めるために、バイアス線を他行の読み出しワード線で代用したり、記憶セルを直列に接続し、NAND構造とし、読み出しワード線と書き込みワード線を共用してもよい。

(もっと読む)

半導体装置

【課題】電力供給がない状況で記憶保持が可能で、書き込み回数に制限が無い、新たな半導体装置を提供する。

【解決手段】チャネル領域と第1のゲート絶縁層と第1のゲート電極と第1のソース及びドレイン電極とを有する第1のトランジスタと、酸化物半導体層140と第2のソース電極142a及び第2のドレイン電極142bと第2のゲート絶縁層146と第2のゲート電極148aとを有する第2のトランジスタ162と、第2のソース電極142aまたは第2のドレイン電極142bの一方と第2のゲート絶縁層146と第2のゲート絶縁層146上に第2のソース電極142a又は第2のドレイン電極142bの一方と重なるように設けられた第3の電極148bとを有する容量素子164と、を有し、第1のゲート電極と第2のソース電極142a又は第2のドレイン電極142bの一方とは接続され、第3の電極148bは酸化物半導体層140と重なる領域を有する。

(もっと読む)

半導体記憶装置

【課題】3次元型の半導体記憶装置のパフォーマンスを向上させる。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と、半導体基板上に設けられ、積層された複数のメモリセルを含む複数のメモリユニットと、カラム方向に配列された複数のメモリユニット上に複数本形成されたビット線とを備え、複数のビット線のロウ方向の配列ピッチは、メモリユニットのロウ方向の配列ピッチよりも小さく、カラム方向に配列された各メモリユニットの端部は、複数本形成されたビット線のいずれか1つに接続される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

半導体装置の製造方法

【課題】非晶質炭素膜を用いて形成する電極のアスペクト比を増大させる。

【解決手段】半導体装置の製造方法は、半導体基板上に第1非晶質炭素膜を形成し、周辺回路領域の第1非晶質炭素膜を除去してメモリセル領域の第1非晶質炭素膜を第2非晶質炭素膜とし、第2非晶質炭素膜を覆う第1シリコン酸化膜を基板全面に形成し、第2非晶質炭素膜上の第1シリコン酸化膜を除去して周辺回路領域の第1シリコン酸化膜を第2シリコン酸化膜とし、第2非晶質炭素膜と第2シリコン酸化膜を覆う第1絶縁膜を形成し、第1絶縁膜に第1開口を形成し、第1開口を埋め込む第2絶縁膜を形成し、第2絶縁膜に第2開口を形成し、第2開口と第1開口が重なる位置に露出する第2非晶質炭素膜にホールを形成し、ホール内に下部電極を形成し、第2絶縁膜を除去して第1開口内に第2非晶質炭素膜を露出させ、露出した第2非晶質炭素膜を全て除去する。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

半導体装置

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】第1のトランジスタ及び第2のトランジスタを有するメモリセルを有し、第1のトランジスタは第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタは酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される不揮発性メモリによって解決する。

(もっと読む)

半導体装置

【課題】高速動作、低消費電力である半導体装置の提供。

【解決手段】結晶性のシリコンをチャネル形成領域に有する第1のトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子である第2のトランジスタとを有する。第2のトランジスタは第1のトランジスタを覆う絶縁膜上に位置する。第1及び第2のトランジスタは、ソース電極又はドレイン電極を共有している。上記絶縁膜は、加熱により一部の酸素が脱離する第1の酸化絶縁膜と、酸素の拡散を防ぎ、なおかつ当該第1の酸化絶縁膜の周囲に設けられた第2の酸化絶縁膜とを有し、第2のトランジスタが有する酸化物半導体膜は、上記第1の酸化絶縁膜に接し、かつチャネル形成領域である第1の領域と、第1の領域を挟み、第1及び第2の酸化絶縁膜に接する一対の第2の領域とを有する半導体装置。

(もっと読む)

半導体記憶装置

【課題】単位面積あたりのメモリモジュールの記憶容量を増加させる。また、消費電力の小さなメモリモジュールを提供する。

【解決手段】半導体装置は、ビット線と、二以上のワード線と、トランジスタおよびキャパシタからなるサブメモリセルを二以上有するメモリセルと、を有する。トランジスタのソースまたはドレインの一方がビット線と接続し、トランジスタのソースまたはドレインの他方がキャパシタと接続し、トランジスタのゲートがワード線の一と接続し、キャパシタの容量が各サブメモリセルで異なる。

(もっと読む)

半導体集積回路

【課題】記憶装置の消費電力を低減すること、記憶装置の面積を低減すること、記憶装置を構成するトランジスタの数を低減する。

【解決手段】第1の出力信号及び第2の出力信号の電位を比較する比較器と、第1の酸化物半導体トランジスタ及び第1のシリコントランジスタを有する第1のメモリ部と、第2の酸化物半導体トランジスタ及び第2のシリコントランジスタを有する第2のメモリ部と、当該第1の出力信号及び当該第2の出力信号の電位を確定する出力電位確定器とを有し、当該第1の酸化物半導体トランジスタのソース又はドレインの一方は、当該第1のシリコントランジスタのゲートに電気的に接続されており、当該第2の酸化物半導体トランジスタのソース又はドレインの一方は、当該第2のシリコントランジスタのゲートに電気的に接続されている記憶装置に関する。

(もっと読む)

記憶回路、信号処理回路、電子機器

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】酸化物半導体を用いて形成されたトランジスタと、該トランジスタのソース電極またはドレイン電極の一方と接続された容量素子を用いて、不揮発性の記憶回路を構成する。記憶回路に予めハイレベル電位を書き込んでおき、退避させるデータがハイレベル電位の場合は、そのままの状態を維持し、退避させるデータがローレベル電位の場合は、ローレベル電位を記憶回路に書き込むことで、書き込み速度を向上させた信号処理回路を実現できる。

(もっと読む)

101 - 120 / 1,403

[ Back to top ]