Fターム[5F083MA16]の内容

Fターム[5F083MA16]に分類される特許

41 - 60 / 1,403

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

半導体記憶装置

【課題】消費電力を低減出来る半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、選択トランジスタ、メモリセル、ワード線、セレクトゲート線、ドライバ回路12、ロウデコーダ11−0、及び検知回路16を備える。ドライバ回路12は、第1電圧Vss,Vccを出力する。ロウデコーダ11−0内の第1転送トランジスタは、ワード線及びセレクトゲート線の各々に関連付けられ、ドライバ回路12から出力された第1電圧を、ワード線及びセレクトゲート線に転送する。検知回路16は、データの消去時において、ビット線及び/またはソース線に印加される第2電圧を検知して、検知結果に応じてフラグを生成する。ドライバ回路12は、フラグが生成されたことに応答して第1電圧の値を変更して、第1転送トランジスタをカットオフさせる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体装置

【課題】半導体チップに構成されるメモリコアにおける電源系を容易に分離可能な配線構造を実現しスループットの向上が可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体チップC1に複数のメモリコア(DRAMコア)が構成される。各メモリコアは、第1電源によって動作しパラレルデータを双方向に伝送するデータバスを駆動する第1回路領域と、第1電源と分離された第2電源によって動作しデータバスを伝送されるパラレルデータと外部端子を介して入出力されるシリアルデータとを双方向に変換する第2回路領域と含む。第1貫通電極群23は、第1回路領域に第1電源を供給する複数の貫通電極をY方向に並べて配置され、第2貫通電極群21は、第2回路領域に第2電源を供給する複数の貫通電極をY方向と交差するX方向に並べて配置される、それぞれの貫通電極群を経由して第1及び第2電源の配線群が互いに分離した配置で形成される。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

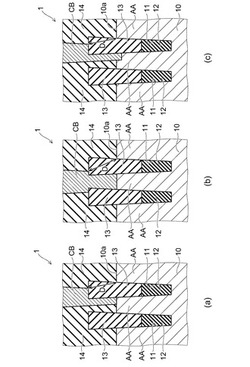

半導体装置およびその製造方法

【課題】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成プロセスを簡略化できるようにする。

【解決手段】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置であり、前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

半導体記憶装置、半導体装置及び半導体記憶装置の製造方法

【課題】DRAMとReRAMとを混載する場合において、容量素子及び抵抗変化素子の性能を維持しながら製造コストを低減する。

【解決手段】半導体記憶装置は、抵抗変化素子1と容量素子101とを具備している。抵抗変化素子1は、第1深さD1のシリンダー型のMIM構造を有し、抵抗変化型メモリ用である。容量素子101は、第1深さD1よりも深い第2深さD2のシリンダー型のMIM構造を有し、DRAM用である。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】制御ゲート電極および浮遊ゲート電極を備えた構成において、制御ゲート電極を構成する多結晶シリコンの空乏化を抑制できるようにした不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された複数の浮遊ゲート電極と、複数の浮遊ゲート電極上に形成された電極間絶縁膜と、電極間絶縁膜上に形成されたワード線と、を備える。ワード線は、不純物がドープされた多結晶シリコンを含む下層および上層を分断し且つ複数の浮遊ゲート電極間に一部が位置する分断層を介在して形成され、ワード線は、その下層の高さが上層の高さよりも低い。

(もっと読む)

半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

(もっと読む)

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

半導体装置

【課題】素子分離すべき領域にダミーの補助ゲートを配置することで、電気的に分離する方法(FS方式)を採用しつつ、補助ゲートに給電するための新たな専用の配線を設けることによるチップの縮小化の弊害を解消する半導体装置を提供する。

【解決手段】半導体基板2に埋め込み形成された素子分離膜によって、複数のセル部活性領域が区画された半導体装置1であって、半導体基板2に設けられたゲート溝内に、ゲート絶縁膜を介して形成された補助セルゲート28aが、半導体基板2と電気的に接続されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化されても、コントロールゲートとフローティングゲートとの間のカップリング容量比を増大させることができる半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。第1の絶縁膜は、半導体基板上に形成されている。フローティングゲートは、第1の絶縁膜上に設けられた第1のフローティングゲート部分、第1のフローティングゲート部分上に設けられた中間絶縁膜、および、中間絶縁膜上に設けられた第2のフローティングゲート部分を含み、電荷を蓄積可能に構成されている。第2の絶縁膜は、フローティングゲートの上面および側面に設けられている。コントロールゲートは、第2の絶縁膜を介してフローティングゲートの上面および側面に対向し、フローティングゲートの電圧を制御する。フローティングゲートの側面において中間絶縁膜が第1および第2のフローティングゲート部分に対して窪んでいる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ガードリング周辺のメモリセル領域から周辺回路領域へのエッチング液の染み込みを防止する。

【解決手段】半導体装置の製造方法は、メモリセル領域及び周辺回路領域が画定された半導体基板上に第1の層間絶縁膜を形成し、第1の層間絶縁膜の一部を除去してメモリセル領域の周囲にガードリング溝を形成し、ガードリング溝を金属導電材で埋めてガードリングとし、ガードリングを覆うように第1の層間絶縁膜上にサポート膜を形成し、メモリセル領域のサポート膜に開口を形成し、開口を通してウエットエッチングを行うことで、周辺回路領域の第1の層間絶縁膜を残したまま、メモリセル領域の第1の層間絶縁膜を除去する。

(もっと読む)

抵抗変化素子

【課題】メサ状構造の抵抗変化素子の外周部の耐圧を増加させることで、低抵抗経路の形成される位置を制御することで電気特性の歩留まりが良く、高集積化可能な抵抗変化素子を提供することを目的とする。

【解決手段】第1の電極と、当該第1の電極の上に形成された抵抗変化層と、当該抵抗変化層の上に形成された第2の電極と、を少なくとも備え、前記抵抗変化層は、遷移金属酸化物を少なくとも含み、前記抵抗変化層の外周部の酸素濃度は、内部の酸素濃度より高いことを特徴とする。

(もっと読む)

メモリ装置

【課題】大容量化が容易であり、高収率且つ高信頼性を有する半導体メモリ装置が提供される。

【解決手段】本発明に従うメモリ装置は、記憶素子と前記記憶素子にデータを書き込むか、又は読み出す周辺回路を含む第1半導体チップ、及び外部と前記第1半導体チップとの間で交換されるデータ又は信号の入出力機能を遂行する第2半導体チップを含み、本発明のその他の特徴に従うメモリ装置は、外部とデータ又は信号を交換するための入出力回路チップ、及び各々前記入出力回路チップから提供される信号に応答して前記データを格納するか、或いは内部に格納されたデータを読み出して前記入出力回路チップへ出力する、垂直方向に積層される複数のコアチップを含む。

(もっと読む)

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体記憶装置の製造方法

【課題】製造工程を簡略化出来る半導体記憶装置の製造方法を提供すること。

【解決手段】実施形態の半導体記憶装置の製造方法は、第1配線層42及び前記第1メモリセル層43〜47をパターニングすることにより、第1方向D1に沿ったストライプ形状の第1構造を第1領域20に形成し、第2構造DM1を第2領域21に形成することと、第1構造及び前記第2構造DM1上に順次形成した第2配線層54及び第2メモリセル層55〜59をパターニングすることにより、第1方向D1と異なる第2方向D2に沿ったストライプ形状を有し、且つ第2領域21における第2構造DM1直上の領域で折り返すパターンを有する第3構造を第1領域20に形成することと、第3構造の折り返す部分における第2配線層54及び第2メモリセル層55〜59、並びにその直下に位置する第1メモリセル層43〜47を除去することとを具備する。

(もっと読む)

41 - 60 / 1,403

[ Back to top ]