Fターム[5F083PR34]の内容

Fターム[5F083PR34]に分類される特許

21 - 40 / 917

強誘電体材料層の製造方法、薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】強誘電体材料層の電気特性をより一層向上させることが可能な強誘電体材料層の製造方法を提供する。

【解決手段】本発明の1つの強誘電体材料層の製造方法は、基材上にゾルゲル溶液を塗布することにより、強誘電体材料の前駆体層を形成する強誘電体材料前駆体層形成工程と、その前駆体層を120℃〜250℃の範囲内にある第1温度で乾燥させる乾燥工程と、その前駆体層を第1温度よりも高く、かつ、150℃〜300℃の範囲内にある第2温度に加熱した状態で前述の前駆体層に対して型押し加工を施す型押し工程と、その前駆体層を第2温度よりも高い第3温度で熱処理することにより、その前駆体層から強誘電体材料層を形成する強誘電体材料層形成工程とを、この順序で含む。

(もっと読む)

圧電体前駆体溶液、圧電セラミックスの製造方法、圧電素子の製造方法、液体噴射ヘッドの製造方法、及び、液体噴射装置の製造方法

【課題】少なくともBi、Ba、Fe及びTiを含む圧電体層を有する圧電素子、液体噴射ヘッド及び液体噴射装置の性能を向上させることにある。

【解決手段】少なくともビスマス、バリウム、鉄及びチタンを含むペロブスカイト型酸化物を形成するための圧電体前駆体溶液は、少なくとも、ビスマス塩、バリウム塩、鉄塩、並びに、チタンの部分アルコキシド(チタンにアルコキシ基及び該アルコキシ基以外の官能基が結合したチタン化合物)を含む。圧電セラミックスの製造方法は、前記圧電体前駆体溶液を塗布する工程と、該塗布した前駆体溶液を結晶化させてペロブスカイト型酸化物を含む圧電セラミックスを形成する工程と、を備える。圧電素子の製造方法は、前記圧電セラミックスに電極を形成する工程を備える。液体噴射ヘッドの製造方法は、前記圧電素子の製造方法により圧電素子を形成する工程を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】放射線耐性能力をさらに向上することができる半導体装置を提供する。

【解決手段】半導体基板1の上方に形成された第1絶縁膜12と、第1絶縁膜12の上方に形成され、下部電極17と上部電極19に挟まれる強誘電体膜18を有するキャパシタQと、キャパシタの上に形成される第2絶縁膜26と、を有し、第1絶縁膜12と下部電極17の間に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第3絶縁膜16、38と、

を有する。

(もっと読む)

誘電体薄膜の成膜方法および成膜システム

【課題】プラズマを用いたスパッタ法によって、Pb、Zr、Tiを含む誘電体薄膜を成膜する場合でも、圧電特性の高い誘電体薄膜を安定して成膜する。

【解決手段】誘電体薄膜のスパッタによる成膜中に、プラズマの発光分析を行って、上記プラズマの発光スペクトルを取得する。そして、上記発光スペクトルに含まれる、Pb(406nm)のスペクトル強度IPb、Zr(468nm)のスペクトル強度IZr、Ti(453nm)のスペクトル強度ITiをそれぞれ求める。IPb/(IZr+ITi)の値をP1としたとき、0.4<P1<0.7を満足するように成膜条件を制御しながら、上記誘電体薄膜を成膜する。

(もっと読む)

圧電セラミックスの製造方法、圧電素子の製造方法、液体噴射ヘッドの製造方法、及び、液体噴射装置の製造方法

【課題】少なくともBi、Ba、Fe及びTiを含む圧電体層を有する圧電素子、液体噴射ヘッド及び液体噴射装置の性能を向上させる製造方法を提供する。

【解決手段】少なくともBi、Ba、Fe及びTiを含む前駆体溶液であって、水溶液とした場合にpHが7以上である前駆体溶液31を下電極20上に塗布し、塗布した前駆体溶液31を結晶化させてペロブスカイト型酸化物を含む圧電セラミックスを形成する。圧電素子の製造方法は、圧電セラミックス30に電極を形成する工程を備える。液体噴射ヘッドの製造方法は、圧電素子の製造方法により圧電素子を形成する工程を備える。

(もっと読む)

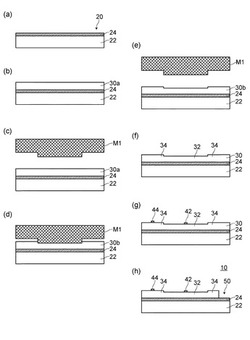

半導体装置およびその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層の溝に埋め込まれた電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設ける。チャネル形成領域は、サイドウォールを側壁に有するゲート電極層と重なる位置に形成される。溝は、深い領域と浅い領域を有し、サイドウォールは、浅い領域と重なり、配線との接続は、深い領域と重なる。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、シリコン層上に、抵抗値が低く、かつ平坦性の良好なニッケルモノシリサイド層を形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】基板に形成されたシリコン層を覆ように白金を含むニッケル層を堆積する工程であって、シリコン層に近い部分では遠い部分と比較して結晶性が低くなるように、白金を含むニッケル層を堆積する工程S05と、基板を加熱することで、シリコン層と白金を含むニッケル層との界面にニッケルモノシリサイド層を形成する工程S07と、を有する。

(もっと読む)

記憶素子および信号処理回路

【課題】消費電力を抑えることができる記憶素子、当該記憶素子を用いた信号処理回路を提供する。

【解決手段】一対のインバータ(クロックドインバータを含む)を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。例えば、容量素子の一方の電極を一対のインバータのいずれかの入力あるいは出力である第1のノードに接続し、他方の電極をスイッチング素子の一方の電極に接続する。スイッチング素子の他方の電極は前記インバータの出力あるいは入力である第2のノードに接続する。ここで、第1のノードの電位と第2のノードの電位は互いに逆の位相である。このような接続により、データ回復時における第1のノードと第2のノードの電位差の絶対値を十分に大きくすることができ、データ回復時のエラーを減らせる。

(もっと読む)

液体噴射ヘッドの製造方法、液体噴射装置の製造方法及び圧電素子の製造方法

【課題】環境負荷が小さく且つ歪み量の大きい圧電素子を有する液体噴射ヘッドの製造方法、液体噴射装置の製造方法及び圧電素子の製造方法を提供する。

【解決手段】基板110、弾性膜50、密着層56、電極60を形成する工程と、電極60の上方に、ビスマス、鉄、バリウム及びチタンを含む前駆体溶液を塗布して塗布膜を形成する工程と、塗布膜を実温165℃以上185℃以下の温度で加熱する乾燥工程と、乾燥工程の後、実温330℃以上440℃以下の温度で加熱する脱脂工程と、脱脂工程の後、脱脂した塗布膜を加熱して結晶化させ圧電膜72を形成する結晶化工程、を具備し、所定厚さの圧電層70を形成する。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。また信頼性の高い半導体装置を提供する。

【解決手段】チャネル形成領域と、ソース領域またはドレイン領域を有する島状半導体膜131と、ゲート絶縁膜と、ゲート電極103とを有する薄膜トランジスタと、層間絶縁膜と、層間絶縁膜中に形成され、ソース領域またはドレイン領域の一方に達する複数のコンタクトホールを含む第1のコンタクトホール142と、ソース領域またはドレイン領域の他方に達する第2のコンタクトホール141とを有し、第2のコンタクトホール141の径は、第1のコンタクトホール142に含まれる複数のコンタクトホール142のそれぞれの径より大きく、第1のコンタクトホールの底面積の合計と、第2のコンタクトホール141の底面積は等しい半導体装置に関する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】注入した導電性不純物により形成される結晶欠陥の密度を低減し、歩留まり率が向上するような半導体装置の製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板を加熱することにより、半導体基板の基板温度を200から500℃の間の所望の温度に維持すると同時に、半導体基板に導電性不純物をイオン注入法もしくはプラズマドーピング法を用いてドーピングし、ドーピングした導電性不純物を活性化させるための活性化処理を行う。

(もっと読む)

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

半導体装置およびその製造方法

【課題】実施形態は、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法を提供する。

【解決手段】実施形態は、基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、前記第1のコンタクトホールの内部に、前記p形半導体領域に接したコンタクトプラグを形成する工程と、を備える。さらに、前記n形半導体領域に連通する第2のコンタクトホールを前記絶縁層に形成する工程と、前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、を備える。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

不揮発性半導体装置およびその製造方法

【課題】絶縁体に電荷を蓄える不揮発性メモリにおいて、データ保持特性を向上させることのできる技術を提供する。

【解決手段】メモリゲート電極MGと半導体基板1との間に介在する電荷蓄積層CSLをメモリゲート電極MGのゲート長または絶縁膜6t,6bの長さよりも短く形成して、電荷蓄積層CSLとソース領域Srmとのオーバーラップ量(Lono)を40nm未満とする。これにより、書込み状態では、書き換えを繰り返すことによって生じるソース領域Srm上の電荷蓄積層CSLに蓄積される正孔が少なくなり、電荷蓄積層CSL中に局在する電子と正孔との横方向の移動が少なくなるので、高温保持した場合のしきい値電圧の変動を小さくすることができる。また、実効チャネル長を30nm以下にすると、しきい値電圧を決定する見かけ上の正孔が少なくなり、電荷蓄積層CSL中での電子と正孔との結合が少なくなるので、室温保持した場合のしきい値電圧の変動を小さくすることができる。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】メモリセルに含まれる整流素子の特性を向上した不揮発性記憶装置の製造方法を提供する。

【解決手段】実施形態に係る不揮発性記憶装置の製造方法は、第1方向にそれぞれ延在する複数の第1導電層と、第1方向と非平行な第2方向にそれぞれ延在し、第1方向と直交する第3方向に第1導電層と離間して設けられた複数の第2導電層と、複数の第1導電層と、複数の第2導電層と、のそれぞれの間に設けられ、多結晶半導体を含む整流素子と、第3方向に整流素子と積層された可変抵抗素子と、を有するメモリセルと、を含む不揮発性記憶装置の製造方法である。この不揮発性記憶装置の製造方法は、非晶質半導体膜を含み、整流素子となる整流素子材料膜を形成する成膜工程と、整流素子材料膜を加熱する加熱工程と、加熱工程によって加熱された整流素子材料膜をパターニングして半導体層を含む整流素子を形成するパターニング工程と、を備える。

(もっと読む)

21 - 40 / 917

[ Back to top ]