Fターム[5F083PR43]の内容

半導体メモリ (164,393) | プロセス (23,970) | メモリセルと周辺回路の同時形成 (5,561) | メモリセル (2,770) | ゲート (954)

Fターム[5F083PR43]に分類される特許

141 - 160 / 954

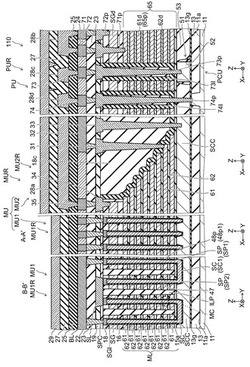

不揮発性半導体記憶装置

【課題】より安定した動作を実現する一括加工型3次元積層型の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、メモリ部MUと、メモリ部に併設された非メモリ部PUと、を備えた不揮発性半導体記憶装置が提供される。メモリ部は、積層された複数の電極膜61と、複数の電極膜どうしの間に設けられた電極間絶縁膜62と、を含む積層構造体MLと、積層構造体と積層された選択ゲート電極SGと、積層構造体及び選択ゲート電極を貫通する半導体ピラーSPと、電極膜と半導体ピラーとの間に設けられた記憶層48と、を含む。非メモリ部は、複数の電極膜の少なくとも1つと同層の部分を含むダミー導電膜65と、選択ゲート電極と同層のダミー選択ゲート電極SGdと、ダミー導電膜に接続されたコンタクト電極と、ダミー選択ゲート電極に接続されたコンタクト電極と、を含む。

(もっと読む)

半導体装置

【課題】正確な抵抗値を有する抵抗素子を備える半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に配置された第1導電体と、第1方向における前記第1導電体の両端の上面に形成されたゲート間絶縁膜と、前記ゲート間絶縁膜が除去された第1接続領域を介して前記第1導電体に接続する第2導電体とを備える第1抵抗素子3−1と、前記半導体基板上に配置された第3導電体と、前記第1方向における前記第3導電体の両端の上面に形成された前記ゲート間絶縁膜と、前記ゲート間絶縁膜が除去された第2接続領域を介して前記第3導電体に接続する第4導電体とを備える第2抵抗素子3−2とを具備し、前記第1方向に沿った前記第2接続領域の長さは、前記第1接続領域の長さよりも長い(LEI2>LEI1)。

(もっと読む)

半導体素子の製造方法、半導体メモリの製造方法、及び半導体素子

【課題】 中電圧トランジスタを形成するための工程数の増加を抑制することが可能な半導体素子の製造方法を提供する。

【解決手段】 半導体基板の上に、下部絶縁膜、下部絶縁膜とは異なる材料からなる中間絶縁膜、及び中間絶縁膜とは異なる材料からなる上部絶縁膜を順番に形成する。半導体基板の表面の第1の領域の上部絶縁膜を除去し、第2の領域には、上部絶縁膜を残す。第1の領域の下部絶縁膜と中間絶縁膜とをゲート絶縁膜として含む第1のトランジスタと、第2の領域の下部絶縁膜、中間絶縁膜、及び上部絶縁膜をゲート絶縁膜として含む第2のトランジスタとを形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化された不揮発性半導体記憶装置で、隣接セル間の寄生容量によるセル間干渉とトランジスタ特性の劣化を従来に比して抑制する。

【解決手段】チャネル半導体上にゲート誘電体膜21、フローティングゲート電極22、トンネル誘電体膜23および制御ゲート電極24が順に積層され、フローティングゲート電極22と制御ゲート電極24は、トンネル誘電体膜23側に曲率を有する尖端部25,26を有する。また、トンネル誘電体膜23のキャパシタンスがゲート誘電体膜21のキャパシタンスと同等以下となるようにトンネル誘電体膜23とゲート誘電体膜21の厚さが調整される。さらに、制御ゲート電極24の尖端部26からフローティングゲート電極22に電子を注入する処理と、フローティングゲート電極22の尖端部26から制御ゲート電極24に電子を抜き取る処理とを、チャネル半導体と制御ゲート電極24との間に印加される電圧によって制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】基板1Cは、半導体基板2と絶縁層3と半導体層4とが積層されたSOI領域1Aと、半導体基板2で構成されたバルク領域1Bとを有しており、SOI領域1Aの半導体層4に形成されたMISFETは、チャネル領域に不純物が導入されておらず、バルク領域1Bの半導体基板2に形成されたMISFETは、チャネル領域に不純物が導入されている。SOI領域1AのMISFETを形成する際には、MISFETのチャネル領域に不純物が導入されないようにし、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とは行なわない。バルク領域1BのMISFETを形成する際には、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とを行う。

(もっと読む)

不揮発性半導体メモリ

【課題】新たなコンセプトに基づく不揮発性半導体メモリを提供する。

【解決手段】本開示の不揮発性半導体メモリは、半導体基板11上の半導体層12と、半導体層12を貫通する複数のコントロールゲートCG11〜CG17と、第1方向の2つの端部における半導体層12内にそれぞれ配置される2つの第1導電型拡散層14と、半導体層12上で第1方向に延びる複数のセレクトゲート線SG1〜SG5と、複数のセレクトゲート線SG1〜SG5上で第2方向に延びる複数のワード線WL1〜WL7とを備える。複数のセレクトゲート線SG1〜SG5の各々は、第1方向に並ぶ複数のコントロールゲートCG11〜CG17と複数のワード線WL1〜WL7との間に接続される複数のセレクトトランジスタに共有されるセレクトゲートとして機能する。半導体層12及び複数のコントロールゲートCG11〜CG17は、メモリセルアレイを構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】メモリセル領域のトランジスタにおけるソース/ドレイン電極上の半導体層同士の接触による短絡を防止しつつ、周辺回路領域のトランジスタにおけるせり上げソース/ドレイン領域を含むソース/ドレイン電極の高濃度不純物層の接合深さの均一性を図り、短チャネル効果を抑制する。

【解決手段】メモリセル領域における隣接するトランジスタ間で半導体層同士が接触しない膜厚にエピタキシャル成長させ、その際、周辺回路領域の素子分離2のみを後退させて露出した基板面からもエピタキシャル成長半導体層10を成長させることで、周辺回路領域の半導体層のファセットFが活性領域外に形成されるようにし、その後、周辺回路領域に高濃度不純物層11用のイオン注入を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、周辺回路領域のうち、メモリセル領域と周辺回路領域の境界付近に位置する領域において、多層的に配線層のレイアウトを行うことで、高集積化を実現することのできる半導体装置及びその製造方法を提供することを課題とする。

【解決手段】素子層16上であって、周辺回路領域12のうち、メモリセル領域11と周辺回路領域12との境界付近に位置する境界領域13に設けられた局所配線21と、素子層16上に設けられた複数の第1及び第2の下部電極95,96及び上部電極98を有するキャパシタ31と、複数の第1の下部電極95を連結すると共に、局所配線19の一部と対向する位置まで延出形成された第1のサポート膜26と、上部電極98とその上方に配置された第1の上部配線42とを連結すると共に、局所配線19の上方に位置し、かつ第1のサポート膜26に到達する第1のコンタクトプラグ37と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート幅が互いに異なる第1,第2のMISトランジスタを備えた半導体装置において、第1,第2のMISトランジスタの閾値電圧を、所望の閾値電圧に制御する。

【解決手段】半導体装置は、第1,第2のMISトランジスタを備えた半導体装置である。第1のMISトランジスタは、第1の高誘電率絶縁膜15aを有する第1のゲート絶縁膜15Aと、第1のゲート電極20Aとを備えている。第2のMISトランジスタは、第2の高誘電率絶縁膜15bを有する第2のゲート絶縁膜15Bと、第2のゲート電極20Bとを備えている。第1,第2のゲート絶縁膜は、調整用金属を含む。第1のMISトランジスタの第1のゲート幅W1は、第2のMISトランジスタの第2のゲート幅W2よりも小さい。第1のゲート絶縁膜中における調整用金属の平均調整用金属濃度は、第2のゲート絶縁膜中における調整用金属の平均調整用金属濃度に比べて低い。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MISFETを含む半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】高耐圧MISFETQ4のゲート絶縁膜GOX4を、酸化シリコン膜と窒化シリコン膜という異なる種類の膜から形成する。具体的に、高耐圧MISFETQ4では、ゲート絶縁膜GOX4を、酸化シリコン膜PREOX1と、この酸化シリコン膜PREOX1上に形成された酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から形成している。

(もっと読む)

半導体構造体及びその製造方法

【課題】 埋め込み型DRAM構造のための半導体構造体及びその製造方法を提供する。

【解決手段】 ノード誘電体及び深いトレンチを充填する導電性トレンチ充填領域がセミコンダクター・オン・インシュレータ(SOI)層の上面とほぼ同一面となる深さにまで窪まされる。浅いトレンチ分離部が深いトレンチの上部の一方の側に形成され、一方深いトレンチの上部の他方の側は、導電性充填領域の半導体材料の露出された表面となる。選択的エピタキシャル成長プロセスが、レイズド・ソース領域及びレイズド・ストラップ領域を付着するために行われる。レイズド・ソース領域は、SOI層内のプレーナ・ソース領域上に直接形成され、そしてレイズド・ストラップ領域は、導電性充填領域上に直接形成される。レイズド・ストラップ領域は、プレーナ・ソース領域及び導電性充填領域の間の導電性通路を与えるためにレイズド・ソース領域に接触する。

(もっと読む)

半導体装置の製造方法

【課題】FEOLにおいても半導体装置のチャージングを効果的に抑制できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に、被保護素子のゲート絶縁膜となる第1の絶縁膜122を形成する工程(a)と、保護素子部302において第1の絶縁膜122の少なくとも一部を除去する工程(b)と、工程(b)よりも後に、被保護素子部301において第1の絶縁膜122の表面を窒化する工程(c)と、工程(c)よりも後に、被保護素子部301及び保護素子部302の上に跨るように導電膜を選択的に形成することにより、互いに接続された被保護素子のゲート電極141及び保護素子の電極142を形成する工程(d)とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】ダミーシリコンピラーを用いてゲート電極を延長する場合の、シリコンピラーにおける反り変形の発生を抑制する。

【解決手段】半導体装置の製造方法は、第1及び第2のシリコンピラー3,4の側周面3a,4aに形成されたゲート絶縁膜9を覆うゲート電極材料を成膜する工程を備え、ゲート電極材料の成膜量は、ゲート絶縁膜9を介して側周面3aを覆う第1の部分と、ゲート絶縁膜9を介して側周面4aを覆う第2の部分とが接触しないよう制御され、第1及び第2の部分を覆うとともに第1の部分と第2の部分の間の領域を埋めるマスク絶縁膜を形成する工程と、マスク絶縁膜をマスクとして用いてゲート電極材料をエッチングすることにより、ゲート絶縁膜9を介してそれぞれ側周面3a,4aを覆うゲート電極101,102と、ゲート電極101,102とを電気的に接続する導体膜11とを形成する工程とをさら備える。

(もっと読む)

半導体装置

【課題】不揮発性メモリと容量素子を有し、性能を向上させる半導体装置を提供する。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MG6nとp型ウエルPW1との間および制御ゲート電極CG4nとメモリゲート電極MG6nとの間には、内部に電荷蓄積層5bを有する絶縁膜5が形成されている。この絶縁膜5は、酸化シリコン膜5aと、その上に形成された窒化シリコン膜5bと、その上に形成された酸化シリコン膜5cと、その上に形成されかつ酸化シリコン膜5cよりも薄い絶縁膜5dとの積層膜からなる。この絶縁膜5dは、ポリシリコンからなるメモリゲート電極MG6nに接している。絶縁膜5dは、Hf,Zr,Al,Ta,Laのうちの少なくとも1種を含む金属化合物により形成されているため、フェルミピニングを生じることができ、誘電率が高い。

(もっと読む)

不揮発性半導体記憶装置

【課題】各メモリセルの書込消去特性を極力一定にできる不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルトランジスタMTは、活性領域Saが素子分離溝2によって互いに分離している。これらのメモリセルトランジスタMTは、それぞれ、活性領域Saの上面上または上方にトンネル絶縁膜3を介して電荷蓄積機能を有する電荷トラップ膜4を備えている。積層絶縁膜Bは、トンネル絶縁膜3および電荷トラップ膜4を少なくとも含んで構成され、トンネル絶縁膜3が素子分離溝2の内面に沿って形成されると共に電荷トラップ膜4がトンネル絶縁膜3の上面に沿って積層されており、素子分離溝2内の全領域に埋込まれている。

(もっと読む)

限られたチャージ拡散を有するチャージトラップメモリ

【課題】隣接メモリセルへの漏洩電流を減らすフラッシュメモリ、特にチャージトラップメモリおよびそれを形成するプロセスフローの提供。

【解決手段】セルチャンネル620を含む半導体線が、STI領域120上に形成される。セルチャンネルは、トンネル酸化物層621、トラッピング誘電体層623、およびブロッキング誘電体層628を含む活性誘電体スタックで覆われる。結果として得られるセルチャンネルを分離するトレンチ625は、伝導層460で少なくとも部分的に充填され得る。活性誘電体層および/または伝導層の部分は、セルチャンネルの下、たとえば、セルチャンネルおよびSTI領域の間の界面695の下に位置し得る。そのような構成は、活性誘電体スタックおよび/または半導体層がセルチャンネルの下に位置しない構成に比べて、あるセルチャンネルから隣接セルチャンネルに拡散する荷電粒子670に対して経路長の増大をもたらす。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】デバイス特性の劣化を抑制した不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】第1ダミーセル領域121に設けられた素子分離絶縁層33と、第2ダミーセル領域122に設けられた素子分離絶縁層43と、第1ダミーセル領域121と第2ダミーセル領域122との間の境界に位置する素子分離絶縁層51とを備える。素子分離絶縁層33の上面は、浮遊電極層32の上面よりも低い高さに位置する。素子分離絶縁層43の上面は、浮遊電極層42の上面と同じ高さに位置する。浮遊電極層32に隣接する素子分離絶縁層51の上面の端部は、浮遊電極層32の上面よりも低い高さに位置する。素子分離絶縁層51の上面は、浮遊電極層32の側面から浮遊電極層42の側面へ向かって上昇する傾斜TLを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】シリコン抵抗とメモリ回路とを混載した半導体装置において、メモリの情報の保持時間を長くして、かつ書込・読出時間を短くする。

【解決手段】容量素子400はメモリセルを構成しており、第1トランジスタ200は、ソース及びドレインとなる第1拡散層226が容量素子400に接続している。シリコン抵抗素子300はシリコン層からなる。第1拡散層226はシリサイド層を有していない。また第1ゲート電極230は、金属層232及びシリコン層234を積層した積層構造を有している。そして第1ゲート電極230は、素子分離膜50上に位置する領域の少なくとも一部にシリサイド層235を有しており、かつ第1拡散層226に挟まれた領域にはシリサイド層を有していない。そしてコンタクト513は、シリサイド層235を介して第1ゲート電極230に接続している。

(もっと読む)

半導体集積回路装置

【課題】ゲート絶縁膜の厚さが異なる複数種類の電界効果トランジスタを有する半導体集積回路装置の信頼性を高める。

【解決手段】第1の電界効果トランジスタQ3及び第2の電界効果トランジスタQ4は埋込絶縁膜25によって分離され、ゲート絶縁膜31,32は各々熱酸化膜27、30と堆積膜27,28,29が積層され、第1の電界効果トランジスタの熱酸化膜は第2の電界効果トランジスタの熱酸化膜より厚く、各トランジスタの堆積膜は、各々各トランジスタの熱酸化膜よりも厚く構成され、第1の電界効果トランジスタのゲート電極は、ゲート幅方向における端部が埋込絶縁膜上に引き出され、かつ端部と埋込絶縁膜との間に第1の電界効果トランジスタの堆積膜が設けられ、第2の電界効果トランジスタのゲート電極は、ゲート幅方向における端部が埋込絶縁膜上に引き出され、かつ前記端部と埋込絶縁膜との間に第2の電界効果トランジスタの堆積膜が設けられる。

(もっと読む)

シリコン・オン・インシュレータ構造において電界効果トランジスタを備える半導体デバイス

【課題】シリコン・オン・インシュレータ構造において複数電界効果トランジスタを備える新規な半導体デバイスを提供する。

【解決手段】基板200と、基板上の酸化物層190と、酸化物層上の半導体層230を備えるSOI構造の電解効果トランジスタと、半導体・オン・インシュレータ構造(SeOI構造)のFETであって、基板内にチャンネル領域200を備え、前記FET構造のBOX構造酸化物層190の少なくとも一部である誘電体をゲート誘電体とし、基板200をチヤネルとする半導体デバイス。

(もっと読む)

141 - 160 / 954

[ Back to top ]