Fターム[5F083PR43]の内容

半導体メモリ (164,393) | プロセス (23,970) | メモリセルと周辺回路の同時形成 (5,561) | メモリセル (2,770) | ゲート (954)

Fターム[5F083PR43]に分類される特許

101 - 120 / 954

半導体装置の製造方法

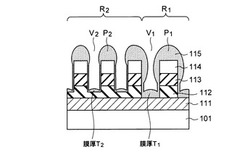

【課題】パターン疎密差の影響を受けないハードマスク形成法を提供する。

【解決手段】基板101上に、第1から第3の膜111,112,113およびレジスト層114を形成した後、疎部R1と密部R2が存在するパターンを前記レジスト層に形成して前記第3の膜をエッチングする。次に、前記第3の膜及び前記レジスト層をマスクとして、密部R2内では前記第2の膜が残存するが、疎部R1内では前記第1の膜が露出するまで、前記第2の膜を除去する。その後CXFYHZガスを使用して、第5の膜115を、疎部R1内に露出した前記第1の膜上に第1の膜厚T1で形成し、密部R2内に残存する前記第2の膜上には膜厚T1よりも薄い第2の膜厚T2で形成する。膜厚T1の前記第5の膜で疎部R1内に露出した前記第1の膜を保護しながら密部R2内に残存する前記第2の膜を除去し、最後に、前記第3から第5の膜を除去して前記第2の膜をハードマスクとする。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】レンチ2内に埋め込まれた埋め込み絶縁膜3の一部を除去することで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1を形成し、空隙AG1は、制御ゲート電極8下に潜るようにしてトレンチ2に沿って連続して形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】周辺回路における回路動作の遅延を低減できる不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板11上に所定間隔を空けて形成され、ゲート絶縁膜1、浮遊ゲート電極2、ゲート間絶縁膜3、及び制御ゲート電極4をそれぞれ有する複数のメモリセルMCと、メモリセルMCの浮遊ゲート電極2の側面、ゲート間絶縁膜3の側面、及び制御ゲート電極4の側面に形成され、空隙を有する側壁絶縁膜18Bと、基板11上に形成され、ゲート絶縁膜1、第1ゲート電極2、ゲート間絶縁膜3、及び制御ゲート電極4を有する周辺トランジスタPTと、周辺トランジスタPTの第1ゲート電極2の側面、ゲート間絶縁膜3の側面、及び制御ゲート電極4の側面に形成され、空隙19Aを有する側壁絶縁膜18Aとを備える。基板11上の最も低い位置にある空隙19Aの上端は、ゲート間絶縁膜3より基板11上の低い位置にある。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】トレンチ2内に埋め込まれた第2の埋め込み絶縁膜4の一部が除去されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、浮遊ゲート電極6間が完全に埋め込まれないようにして制御ゲート電極8間にカバー絶縁膜10が掛け渡されることで、ビット線方向にDBに隣接する浮遊ゲート電極6間に空隙AG2が形成されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】誘電体膜のクラック発生が抑制され、リーク電流特性に優れたキャパシタを有する半導体記憶装置を提供する。

【解決手段】半導体記憶装置の製造方法は、半導体基板上に窒化チタン膜を有する立体構造の下部電極を形成した後、下部電極の表面に誘電体膜を形成する。誘電体膜の表面に、誘電体膜が結晶成長しない温度で第一の上部電極を形成した後、誘電体膜が結晶成長する温度で熱処理し、誘電体膜の少なくとも一部を多結晶状態に変換する。この後、第一の上部電極表面に第二の上部電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】スタック構造のゲート電極を有する不揮発性メモリの低電圧動作化・低消費電力化を実現しうる半導体装置の製造方法を提供する。

【解決手段】素子分離絶縁膜上に第1の導電膜を形成し、素子領域上に第1の絶縁膜を形成し、第1の絶縁膜上及び第1の導電膜が形成された素子分離絶縁膜上に第2の導電膜を形成し、第2の導電膜及び第1の導電膜をパターニングし、第2の導電膜により形成された第1の部分が素子領域上に位置し、第1の導電膜と第2の導電膜の積層膜により形成された第2の部分が素子分離絶縁膜上に位置するフローティングゲートを形成し、フローティングゲート上に第2の絶縁膜を形成し、第2の絶縁膜上にコントロールゲートを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】下部電極、上部電極およびそれらの間の絶縁膜により構成される容量素子の下部電極および上部電極間の耐圧を向上させる。

【解決手段】上部電極TEならびに上部電極TEのそれぞれの側壁の側壁酸化膜9およびサイドウォール10と下部電極BEとの間にONO膜IFを連続的に形成し、また、上部電極TEの側壁に、側壁酸化膜9を介して真性半導体膜からなるサイドウォール10を形成することにより、下部電極BEおよび上部電極TE間にリーク電流が発生することを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】的確かつ効果的にパターンを形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地領域上に、第1のピッチで配置された複数のダミーラインパターン21cを形成する工程と、ダミーラインパターン21cの両長側面に形成された所定マスク部分を有し、ダミーラインパターンを囲む閉ループ形状のマスクパターン25cを形成する工程と、ダミーラインパターン21cを除去する工程と、マスクパターン25cの両端部分を除去して所定マスク部分を残す工程と、所定マスク部分をマスクとして用いて下地領域をエッチングする工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリは、半導体基板1上に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1上に電荷蓄積部を有する絶縁膜5を介して形成されたメモリゲート電極MGとを有しており、メモリゲート電極MGは、制御ゲート電極CGの側面22上に絶縁膜5を介してサイドウォールスペーサ状に形成されている。制御ゲート電極CGは、メモリゲート電極MGに絶縁膜5を介して隣接する側とは反対側の側面21の下部21aが突出し、また、メモリゲート電極MGに絶縁膜5を介して隣接する側の側面22の下部22aが後退している。メモリゲート電極MGは、制御ゲート電極CGに絶縁膜5を介して隣接する側の側面23の下部23aが突出している。

(もっと読む)

半導体装置の製造方法

【課題】 半導体記憶装置に係り、特に、高集積化されたDRAMを、少ない工程数で、且つ微細なセル面積で実現できる半導体記憶装置及びその製造方法を提供する。

【解決手段】 半導体基板10に形成されたメモリセルトランジスタと、メモリセルトランジスタのゲート電極20の上面及び側面を覆う絶縁膜42と、ソース拡散層24上に開口したスルーホール40と、ドレイン拡散層26上に開口したスルーホール38とが形成された層間絶縁膜36と、スルーホール40内壁及び底部に形成され、ソース拡散24層に接続されたキャパシタ蓄積電極46と、キャパシタ蓄積電極46を覆うキャパシタ誘電体膜48と、キャパシタ誘電体膜48を覆うキャパシタ対向電極54とを有するキャパシタと、スルーホール38の内壁及び底部に形成され、ドレイン拡散層と接続されたコンタクト用導電膜44とにより構成する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は半導体装置に関する。

【解決手段】本発明は、半導体基板上のセル領域のセルトランジスタ上の層間膜を貫通してコンタクトプラグが形成され、周辺回路領域のトランジスタ上の層間膜を貫通してコンタクトプラグが形成されてなる半導体装置の製造方法であり、セルトランジスタ上の層間膜にコンタクトホールを形成し、その底部側にシリコン膜の下部導電プラグを形成する工程と、その上に金属膜を積層して積層構造のセルコンタクトプラグを形成する工程と、周辺回路用トランジスタ上の層間膜にコンタクトホールを形成し、その内部に金属膜を形成してコンタクトプラグを形成する工程とを具備し、前記セル領域のコンタクトホール内のシリコン膜上に金属膜を形成する工程と前記周辺回路領域のコンタクトホール内に金属膜を形成する工程を同時に行うことを特徴とする。

(もっと読む)

シリコン酸化膜の形成方法、シリコン窒化膜の形成方法、シリコン酸窒化膜の形成方法

【課題】ポリシリコン上において高品質な絶縁膜を形成できる絶縁膜の形成方法を提供する

【解決手段】シリコン酸化膜の形成方法は、基板上にポリシリコン膜を堆積する工程と、

前記ポリシリコン膜の表面を、酸素を含むガスとKrガスを主体とする不活性ガスとよりなる混合ガスにマイクロ波によりプラズマを励起することで形成される原子状酸素O*に曝すことにより、前記ポリシリコン膜の表面にシリコン酸化膜を形成する工程とよりなる。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

ナンドフラッシュメモリ素子及びその製造方法

【課題】セレクトラインの抵抗を改善すると同時にナンドフラッシュメモリ素子の製造工程を単純化することができるナンドフラッシュメモリ素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された選択トランジスタ及びメモリセル用第1導電膜パターンと、前記第1導電膜パターン上に形成された誘電体膜と、前記メモリセル用第1導電膜パターン上の前記誘電体膜上に形成された第2導電膜パターンと、前記選択トランジスタ用第1導電膜パターンと繋がれて前記第2導電膜パターンより抵抗の低い物質で形成されたセレクトラインと、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】立体構造キャパシタを備えた半導体装置であって、上下部電極に金属若しくは金属化合物を用いるMIM構造で、容量絶縁膜に高誘電体膜を用いるキャパシタにおいて、高誘電率でリーク電流が抑制された信頼性の高いキャパシタを備える半導体装置を提供する。

【解決手段】TiN下部電極102上に酸化ジルコニウム誘電体膜113を形成し、誘電体膜上にTiNを含む上部電極117を形成する際、誘電体膜をALD法で形成し、上部電極を形成する前に誘電体膜形成時のALD法の成膜温度を70℃以上超える温度を付加することなく、第一の保護膜116を成膜する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造工程を増加させることなく絶縁破壊耐性に優れた信頼性に懸念のない、小さな占有面積で所期の容量を確保する容量密度の高いパスコンを備えた半導体装置を実現する。

【解決手段】パスコンについて、第1の容量絶縁膜が、記憶素子のトンネル絶縁膜と共に第1の絶縁膜23で形成され、下部電極である第1の電極26が、記憶素子の浮遊ゲート電極25と共にドープト・アモルファスシリコン膜24(結晶化されたもの)で形成され、第2の容量絶縁膜が、周辺回路の5Vのトランジスタのゲート絶縁膜と共に第2の絶縁膜33で形成され、上部電極である第2の電極37が、記憶素子の制御ゲート電極36及び周辺回路のトランジスタのゲート電極41と共に多結晶シリコン膜34で形成される。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGとp型ウエルPW1との間および制御ゲート電極CGとメモリゲート電極MGとの間には、絶縁膜5が形成されている。この絶縁膜5のうち、メモリゲート電極MGの下面と半導体基板1の上面との間の部分は、酸化シリコン膜9a,9bと酸化シリコン膜9a,9bに挟まれた窒化シリコン膜10aとを有している。絶縁膜5のうち、制御ゲート電極CGの側面とメモリゲート電極MGの側面との間の部分は、酸化シリコン膜6aからなり、窒化シリコン膜10aを有していない。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGとp型ウエルPW1との間および制御ゲート電極CGとメモリゲート電極MGとの間には、絶縁膜5が形成されている。この絶縁膜5のうち、メモリゲート電極MGの下面と半導体基板1の上面との間の部分は、酸化シリコン膜6a,6cと酸化シリコン膜6a,6cに挟まれた窒化シリコン膜6bとを有している。絶縁膜5のうち、制御ゲート電極CGの側面とメモリゲート電極MGの側面との間の部分は、酸化シリコン膜6a,6cと酸化シリコン膜6a,6cに挟まれた空洞CAVとを有し、窒化シリコン膜6bを有していない。

(もっと読む)

半導体集積回路装置の製造方法

【課題】素子特性の安定性を向上できる半導体集積回路装置の製造方法を提供する。

【解決手段】半導体集積回路装置の製造方法は、シリコン基板101の表面に第1の酸化膜103を形成する工程と、周辺回路領域A2内にあるシリコン基板101の所定箇所に不純物を注入し、この所定箇所上の第1の酸化膜103を除去し、この所定箇所上に第2の酸化膜112を形成する工程と、メモリセル領域A1内の第1の酸化膜103にトンネルウィンドウを形成し、このトンネルウィンドウ内で露出したシリコン基板101上にトンネル酸化膜116を形成し、トンネル酸化膜116を覆うメモリセル用ポリシリコン膜118を形成する工程と、第2の酸化膜112を形成する前記工程の後にメモリセル用ポリシリコン膜118上にONO膜119を形成する工程とを有する。

(もっと読む)

101 - 120 / 954

[ Back to top ]