Fターム[5F092BB42]の内容

ホール/MR素子 (37,442) | MR素子の材料 (13,747) | 自由層(感磁層を含む) (2,425) | Fe、Co、Niのみの合金又は単体 (1,217)

Fターム[5F092BB42]に分類される特許

21 - 40 / 1,217

磁気メモリ素子及び磁気メモリ装置

【課題】電流で書き込み動作を行うことができる大容量の磁気メモリ及び磁気メモリ装置を提供する。

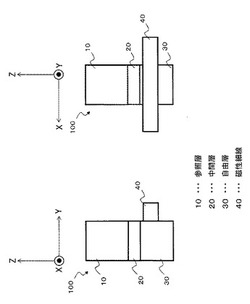

【解決手段】磁化が固定された第1の磁性層10と、磁化が可変の第2の磁性層30と、第1の磁性層10と第2の磁性層30との間に設けられた第1の中間層20と、第1の磁性層10と第2の磁性層30とを結ぶ第1の方向に直交する第2の方向に延在し、第2の磁性層30に隣接し、スピン波を伝搬する第1の磁性細線40と、第1の磁性細線40の一端に設けられた第1のスピン波入力部と、第1の磁性細線40の他端に設けられた第1のスピン波検出部と、を備える。

(もっと読む)

磁気メモリ素子

【課題】実施形態による、磁壁制御が容易な磁気メモリ素子を提供する。

【解決手段】磁気メモリ素子100は、第1方向に延在し、磁壁により隔てられた複数の磁区を有する磁性細線20と、前記磁性細線20に対して前記第1の方向又は前記第1の方向と逆方向に通電可能な一対の第1の電極30と、前記第1の方向に直交する第2の方向において、前記磁性細線20上に設けられた第1の絶縁層40と、前記第2の方向であって前記第1の絶縁層40上に離間して設けられた複数の第2の電極50と、複数の前記第2の電極50と電気的に接続された第3の電極60と、を備える。

(もっと読む)

磁気メモリ

【課題】磁気メモリの動作不良を抑制する。

【解決手段】本実施形態の磁気メモリは、第1領域内の第1の磁気抵抗効果素子1Aと、第2の領域の磁気抵抗効果素子1Xとを含む。第1の磁気抵抗効果素子1Aは、磁化の向きが可変な第1の記憶層10と、磁化の向きが不変な第1の参照層12と、非磁性層11と、第1のシフト調整層13と、を含む。第2の磁気抵抗効果素子1Xは、磁化の向きが可変な第2の記憶層10と、磁化の向きが不変な第2の参照層12と、第2の非磁性層11と、第2のシフト調整層13Xと、を含む。第2のシフト調整層13Xの膜厚t2は、第1のシフト調整層13の膜厚t1以下である。

(もっと読む)

磁気記憶素子及び不揮発性記憶装置

【課題】高密度化が可能な磁気記憶素子及び不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、積層体を備えた磁気記憶素子が提供される。積層体は第1積層部と第2積層部とを含む。第1積層部は、膜面に対して垂直成分を有する第1の方向に磁化が固定された第1強磁性層と、磁化の方向が膜面垂直な方向に可変である第2強磁性層と、第1強磁性層と第2強磁性層との間の第1非磁性層と、を含む。第2積層部は、積層方向に沿って第1積層部と積層される。第2積層部は、磁化の方向が膜面平行な方向に可変である第3強磁性層と、膜面に対して垂直成分を有する第2の方向に磁化が固定された第4強磁性層と、第3強磁性層と第4強磁性層との間の2非磁性層と、を含む。積層方向を法線とする平面で切断したとき、第3強磁性層の断面積は前記第1積層部よりも小さい。

(もっと読む)

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】アナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の抵抗器で分圧して複数の比較用電圧を生成する。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧との比較結果に応じたデジタル信号を出力する。各比較器は、2つの入力の電位差を検出する差動対回路を含む。差動対回路は、第1回路部50と第2回路部60とを有する。第1回路部は、第1入力トランジスタ51と、第1入力トランジスタと直列に接続される抵抗器Rrefとを含む。第2回路部は、第1入力トランジスタと差動対を形成する第2入力トランジスタ61と、第2入力トランジスタと直列に接続される可変抵抗器Rvとを含む。可変抵抗器は、直列に接続されるとともに、制御信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。

(もっと読む)

磁気抵抗効果素子、磁気メモリ及び磁気抵抗効果素子の製造方法

【課題】磁気抵抗効果素子の特性劣化を抑制する。

【解決手段】本実施形態の磁気抵抗効果素子は、膜面に対して垂直方向に磁気異方性と不変な磁化方向とを有する第1の磁性体30と、膜面に対して垂直方向に磁気異方性と可変な磁化方向とを有する第2の磁性体10と、磁性層10,30の間の非磁性体20とを、含む。第1及び第2の磁性体のうち少なくとも一方は、ボロン(B)及び希土類金属及び遷移金属を含む磁性層301を備え、磁性層301において、希土類金属の含有量は、20at.%以上であり、遷移金属の含有量は、30at.%以上であり、ボロンの含有量が、1at.%以上、50at.%以下である。

(もっと読む)

磁気センサ、磁気積層および方法

【課題】この発明のさまざまな実施例は、第1の強磁性自由層138と第2の強磁性自由層140との間に配置されたスペーサ層142とともに構築されてもよい、磁気応答積層132に一般的に向けられる。

【解決手段】少なくとも1つの強磁性自由層は、磁気応答積層の磁気抵抗比(MR)を向上させる結合サブ層186,196を有することができる。

(もっと読む)

磁気抵抗効果素子およびその製造方法

【課題】磁気特性の低下の抑制を図る。

【解決手段】磁気抵抗効果素子は、磁化方向が膜面に対して垂直でかつ不変である第1磁性層33と、前記第1磁性層上に形成されたトンネルバリア層34と、前記トンネルバリア層上に形成され、磁化方向が膜面に対して垂直でかつ可変である第2磁性層35と、を具備する。前記第1磁性層は、上部側に形成され、前記トンネルバリア層の下部に接する界面層32と、下部側に形成され、垂直磁気異方性の起源となる本体層31と、を有する。前記界面層は、内側に設けられた磁化を有する第1領域38と、その外側に前記第1領域を取り囲むように設けられた前記第1領域よりも磁化の小さい第2領域39と、を含む。

(もっと読む)

磁気メモリ

【課題】磁気記録層の強磁性体膜が強い垂直磁気異方性を有する磁気メモリを提供する。

【解決手段】磁気メモリは、強磁性体の下地層51と、下地層51上にの第1非磁性52と、第1非磁性52上の垂直磁気異方性を有する強磁性体のデータ記憶層53と、第2非磁性層20を介してデータ記憶層53に接続された参照層30と、下地層51の下側に接した第1、第2磁化固定層41a、41bとを具備する。データ記憶層53は、反転可能な磁化を有し参照層30とオーバーラップする磁化自由領域13と、磁化自由領域13の端に接続され、第1磁化固定層41aに+z方向に磁化固定された第1磁化固定領域11aと、磁化自由領域13の他の端に接続され、第2磁化固定層41bに−z方向に磁化固定された第2磁化固定領域11bとを備える。磁化自由領域13下の第1非磁性52は、第1、第2磁化固定領域11a、11b下の第1非磁性52よりも厚い。

(もっと読む)

不揮発性記憶装置

【課題】安定した動作が可能な不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、磁気記憶素子と制御部とを備えた不揮発性記憶装置が提供される。磁気記憶素子は積層体を含む。積層体は第1積層部と第2積層部とを含む。第1積層部は、磁化が固定された第1強磁性層と、磁化の方向が可変の第2強磁性層と、第1強磁性層と第2強磁性層との間に設けられた第1非磁性層と、を含む。第2積層部は、積層方向に沿って第1積層部と積層される。第2積層部は、通電される電流によって磁化が回転して発振が生じる第3強磁性層と、磁化が固定された第4強磁性層と、第3強磁性層と第4強磁性層との間に設けられた第2非磁性層と、を含む。制御部は、第2強磁性層の磁化の向きに応じた第3強磁性層の発振の周波数の変化を検出することで、第2強磁性層の磁化の向きを読み出す読み出し部を含む。

(もっと読む)

磁気記憶素子及び不揮発性記憶装置

【課題】安定した動作が可能な磁気記憶素子及び不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、第1、第2積層部を含む磁気記憶素子が提供される。第1積層部は、第1強磁性層/第1非磁性層/第2強磁性層を含む。第1強磁性層の磁化は面直に固定され、第2強磁性層の磁化方向は面直に可変である。第2積層部は、第3強磁性層/第2非磁性層/第4強磁性層を含む。第3強磁性層の磁化方向は面内方向に可変であり、第4強磁性層の磁化は面直に固定されている。第3強磁性層の位置での第1、第2、第4強磁性層からの漏れ磁界Hs、第3強磁性層の磁気異方性Ku、ダンピング定数α、磁化Ms及び反磁界係数Nzは、Ku≦αMs(8πNzMs−Hs)を満たす。電流によりスピン偏極した電子と、第3強磁性層で発生する回転磁界と、を第2強磁性層に作用させ、第2強磁性層の磁化方向を決定できる。

(もっと読む)

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】実施形態のアナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の可変抵抗器で分圧して複数の比較用電圧を生成する。複数の可変抵抗器の各々は、直列に接続されるとともに、外部信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧とを比較し、その比較結果に応じたデジタル信号を出力する。

(もっと読む)

磁気抵抗効果素子およびその製造方法

【課題】書き込み電流の低減およびリテンション特性の向上を図る。

【解決手段】磁気抵抗効果素子は、磁化方向が膜面に対して垂直でかつ可変である第1磁性層31と、前記第1磁性層上に形成されたトンネルバリア層32と、前記トンネルバリア層上に形成され、磁化方向が膜面に対して垂直でかつ不変である第2磁性層40と、を具備する。前記第2磁性層は、垂直磁気異方性の起源となる本体層34と、前記トンネルバリア層と前記本体層との間に形成され、前記本体層よりも高い透磁率を有し、前記本体層よりも大きい平面サイズを有する界面層33と、を備える。前記本体層の側面に、前記本体層よりも高い透磁率を有するシールド層90が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を劣化させることなく、半導体材料または絶縁膜の結晶特性を改善することができる低温アニールを用いた半導体装置の製造方法、並びに、このような低温アニールに適した半導体装置を提供する。

【解決手段】本実施形態による半導体装置は、半導体基板の上方に設けられた金属からなる下部電極と、下部電極の上方に設けられた金属からなる上部電極と、下部電極と上部電極との間に設けられた結晶層とを備える。下部電極および上部電極の各膜厚は、結晶層の結晶化に用いられるマイクロ波の周波数に対応する表皮効果における表皮層よりも薄い。

(もっと読む)

混合器

【課題】

乗算信号の出力低下を回避しつつ、低いローカルパワーで作動可能とする。

【解決手段】

磁化固定層、磁化自由層、および前記磁化固定層と前記磁化自由層との間に配設された非磁性スペーサー層を備え、高周波信号S1およびローカル信号S2を入力したときに磁気抵抗効果によって両信号S1,S2を乗算して電圧信号(乗算信号)S3を生成する磁気抵抗効果素子2の磁化自由層に対し、磁場印加部3より発生する磁場を膜面法線方向、または膜面方向から膜面法線方向に傾けて掛けることで、Q値の高い共振特性を得ることができ、大きな乗算信号を得ることができ、さらに狭帯域周波数選択性の機能を有する周波数変換装置を提供する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】MTJ素子内における層間の短絡を抑制し、かつ、MTJ素子を構成する磁性層の劣化を抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板を備える。磁気トンネル接合素子は、2つの磁性層と該2つの磁性層間に設けられたトンネル絶縁膜とを含み、半導体基板の上方に設けられている。側壁膜は、磁気トンネル接合素子の側面の上部に設けられている。フェンス層は、導電性材料を含み、側壁膜の側面および磁気トンネル接合素子の側面の下部に設けられている。フェンス層の頂点は、側壁膜の頂点よりも低く、かつ、トンネル絶縁膜よりも高い位置にある。

(もっと読む)

磁気センサ

【課題】被実装部材上に回路チップと隣接して搭載される磁気センサにおいて、回路チップとパッドとを電気的に接続するワイヤ同士の接触を抑制することができる磁気センサを提供する。

【解決手段】複数のパッド31〜36を一辺10aと垂直方向において互いに完全にオフセットした状態で配置する。これによれば、被実装部材上に磁気センサの一辺10aを回路チップと隣接して搭載し、パッド31〜36と回路チップとをワイヤで接続した際に、ワイヤ同士が接触してしまうことを抑制することができる。

(もっと読む)

周波数選択性を有する混合器

【課題】

大きな乗算信号を取り出すことが可能で、さらに受信用バンドパスフィルタ機能を有した混合器を提供することを主目的とする。

【解決手段】

磁化固定層、磁化自由層、および前記磁化固定層と前記磁化自由層との間に配設された非磁性スペーサー層を備え、高周波信号S1およびローカル信号S2を入力したときに磁気抵抗効果によって当該両信号S1,S2を乗算して電圧信号(乗算信号)S4を生成する磁気抵抗効果素子2から得た乗算信号は、共振特性の強度に応じて増減し、共振周波数f0と両信号S1,S2のそれぞれ周波数f1、f2が一致するときに最大強度を示し、共振周波数f0から周波数f1、f2の両方またはいずれか一つが離れると減衰する。あたかもバンドパスフィルタを挿入したときと同じ効果があり、磁場印加部3による磁場を制御することで、所望のバンドパスフィルタを有する周波数変換装置を提供できる。

(もっと読む)

半導体磁気記憶装置

【課題】磁気記憶素子を構成する層を、周辺回路部内で有効に活用する。

【解決手段】実施形態によれば、半導体磁気記憶装置は、セルトランジスタを含むセル部と、周辺トランジスタを含む周辺回路部とが形成された半導体基板を備える。さらに、前記装置は、前記セル部内に配置され、下部電極と、前記下部電極上に形成された電極間層と、前記電極間層上に形成された上部電極とを含む磁気記憶素子を備える。さらに、前記装置は、前記周辺回路部内に配置され、前記下部電極を形成している第1の層と、前記電極間層を形成している第2の層と、前記上部電極を形成している第3の層とを含む構造体を備える。さらに、前記装置は、前記第1の層に電気的に接続された第1及び第2のプラグを備える。さらに、前記第1の層は、前記第1のプラグと前記第2のプラグを電気的に接続する配線として機能する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】MTJ素子内における層間の短絡を抑制し、かつ、MTJ素子を構成する磁性層の劣化を抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態による半導体記憶装置は半導体基板を備える。磁気トンネル接合素子は、2つの磁性層と該2つの磁性層間に設けられたトンネル絶縁膜とを含み、半導体基板の上方に設けられている。側壁膜は、磁気トンネル接合素子の側面の上部に設けられている。フェンス層は、導電性材料を含み、側壁膜の側面および磁気トンネル接合素子の側面の下部に設けられている。保護膜は、絶縁体からなりフェンス層の側面に設けられている。フェンス層の上面および保護膜の上面は、側壁膜の上面よりも低く、かつ、トンネル絶縁膜よりも高い位置にある。

(もっと読む)

21 - 40 / 1,217

[ Back to top ]