Fターム[5F101BD30]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | SOI、薄膜トランジスタ、三次元素子 (1,051)

Fターム[5F101BD30]に分類される特許

121 - 140 / 1,051

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のトランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電位を保持させることで行う。メモリセルの読み出しは、ビット線にプリチャージ電位を供給した後ビット線への電位の供給を止め、ビット線の電位がプリチャージ電位に保たれるか、または電位が下がるか、により行う。

(もっと読む)

記憶回路、信号処理回路、電子機器

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】酸化物半導体を用いて形成されたトランジスタと、該トランジスタのソース電極またはドレイン電極の一方と接続された容量素子を用いて、不揮発性の記憶回路を構成する。記憶回路に予めハイレベル電位を書き込んでおき、退避させるデータがハイレベル電位の場合は、そのままの状態を維持し、退避させるデータがローレベル電位の場合は、ローレベル電位を記憶回路に書き込むことで、書き込み速度を向上させた信号処理回路を実現できる。

(もっと読む)

記憶回路

【課題】短時間の電源停止により消費電力を抑えることができ、電源再開時において誤動作を引き起こすことなく初期化することのできる信号処理装置の記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性記憶部に記憶していたデータ信号を、不揮発性記憶部に保持する。不揮発性記憶部では、オフ電流が極めて小さいトランジスタを用いることによって、容量素子に保持されたデータ信号は長期間にわたり保持する。こうして、不揮発性記憶部は電源の供給が停止した間も論理状態を保持する。また電源停止時に容量素子で保持されたデータ信号は、電源再開時にはリセット回路を導通状態とすることで、誤動作を引き起こすことのない電位にする。

(もっと読む)

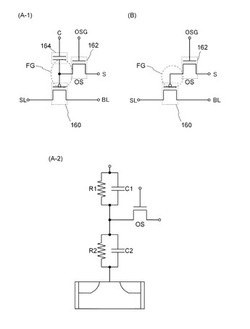

半導体装置

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】第1のトランジスタ及び第2のトランジスタを有するメモリセルを有し、第1のトランジスタは第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタは酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される不揮発性メモリによって解決する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリトランジスタの特性が均一な半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、それぞれ複数枚の絶縁膜及び導電膜を交互に積層することにより、積層体を形成する工程と、前記積層体に、一方向に延び各前記導電膜を分断するトレンチを形成する工程と、前記トレンチ内にジブロックコポリマーを埋め込む工程と、前記ジブロックコポリマーを、前記積層方向に延びる複数の第1のブロック及び絶縁性の第2のブロックに相分離させる工程と、前記第1のブロックを除去することにより、複数本のホールを形成する工程と、前記ホールの内面上に電荷蓄積層を形成する工程と、前記ホール内に半導体材料を埋め込むことにより、前記積層方向に延びる複数本の半導体ピラーを形成する工程と、を備える。

(もっと読む)

記憶装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な記憶装置、及び該記憶装置を有する半導体装置を提供する。

【解決手段】第1の入力端子、及び第1の入力端子の入力信号の反転信号が入力される第2の入力端子、並びに第1の信号が出力される第1の出力端子、及び第1の信号の反転信号が出力される第2の出力端子、を有するレベルシフタと、第1の信号が入力される第3の入力端子、及び第1の信号の反転信号が入力される第4の入力端子、並びに第3の出力端子を有する第1のバッファと、第1の信号の反転信号が入力される第5の入力端子、及び第1の信号が入力される第6の入力端子、並びに第4の出力端子を有する第2のバッファと、を有し、第1のバッファの第3の出力端子から出力される信号が、レベルシフタの第1の入力端子に入力され、第2のバッファの第4の出力端子から出力される信号が、レベルシフタの第2の入力端子に入力される。

(もっと読む)

半導体集積回路

【課題】記憶装置の消費電力を低減すること、記憶装置の面積を低減すること、記憶装置を構成するトランジスタの数を低減する。

【解決手段】第1の出力信号及び第2の出力信号の電位を比較する比較器と、第1の酸化物半導体トランジスタ及び第1のシリコントランジスタを有する第1のメモリ部と、第2の酸化物半導体トランジスタ及び第2のシリコントランジスタを有する第2のメモリ部と、当該第1の出力信号及び当該第2の出力信号の電位を確定する出力電位確定器とを有し、当該第1の酸化物半導体トランジスタのソース又はドレインの一方は、当該第1のシリコントランジスタのゲートに電気的に接続されており、当該第2の酸化物半導体トランジスタのソース又はドレインの一方は、当該第2のシリコントランジスタのゲートに電気的に接続されている記憶装置に関する。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置の集積化を図る。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と半導体基板上に設けられ、積層された複数のメモリセルを含むメモリセルアレイと、複数のメモリセルと電気的に接続されて平行に配列された複数のビット線と、ビット線接続配線を介してビット線と接続された複数のセンスアンプとを備える。ビット線接続配線は、隣接するN(Nは2以上の整数)本ごとに1つのグループとする。センスアンプは、ビット線接続配線が延びる第1方向にはNよりも小さい数で、且つ前記第1方向と交差する第2方向には前記グループ間のピッチよりも小さいピッチで配列されている。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性半導体装置の高集積化を図ることのできる技術を提供する。

【解決手段】スイッチ用nMIS(Qs)のスイッチゲート電極SGと、スイッチ用nMIS(Qs)にワード線に対して交差する方向に沿って隣接するメモリ用nMIS(Qm)のメモリゲート電極MGとの間に、スイッチ用nMIS(Qs)のソース/ドレイン領域SDHとして機能し、同時にメモリ用nMIS(Qm)のドレイン領域Dとして機能する半導体領域を形成し、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)側のソース/ドレイン領域SDHを構成する半導体領域の形状と、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)と反対側(ビット線側)のソース/ドレイン領域SDLを構成する半導体領域の形状とを非対称とする。

(もっと読む)

三次元半導体装置及びその製造方法

【課題】導電層とコンタクトの十分な接続を確保可能な三次元半導体装置及びその製造方法を提供する。

【解決手段】三次元半導体装置は、半導体基板上に導電層と絶縁層とが交互に複数積層され、前記複数の導電層は、それらの端部の位置が上層から下層にかけて徐々にずれた階段部を形成し、前記階段部の各ステップに、積層方向に延びるコンタクトがそれぞれ接続されたものであり、前記階段部が、少なくとも最上層から所定の導電層までは、上層の導電層ほど前記ステップの幅が広くなるように形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】誤書込みを抑制した不揮発性半導体記憶装置を提供する。

【解決手段】制御回路は、書込み動作時、複数のビット線中の書込み禁止ビット線の電圧を第1電圧まで上げた後、書込み禁止ビット線をフローティング状態とする。続いて、制御回路は、書込み禁止ビット線以外の書込みビット線の電圧を第2電圧まで上げ、これに伴うカップリングにより書込み禁止ビット線の電圧を上げる。これにより、制御回路は、書込み禁止ビット線に対応するメモリストリング内のメモリトランジスタに対して書込み動作を禁止する。一方、制御回路は、書込みビット線に対応するメモリストリング内のメモリトランジスタに対して書込み動作を実行する。

(もっと読む)

半導体記憶装置

【課題】積層型の半導体記憶装置のパフォーマンスを向上させる。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と、半導体基板に対して垂直方向に延び複数のメモリセルを直列接続してなる柱状に形成された複数のメモリユニットを、半導体基板に沿って二次元配列してなるメモリセルアレイと、メモリセルアレイの各メモリユニットの端部に接続される複数のビット線とを備える。複数のメモリユニットは、カラム方向に隣接する前記メモリユニット同士がメモリユニットのロウ方向の配列ピッチ内でロウ方向に変位することにより千鳥状に配列される。

(もっと読む)

半導体装置

【課題】瞬断もしくは瞬時電圧低下等の極めて短時間の電源停止又は電源電圧低下の場合でさえ、揮発性メモリ内のデータが消失してしまう場合があった。そこで、高速データ処理のために揮発性メモリを用いた場合であっても、データの保持時間を延ばす。

【解決手段】容量素子及び酸化物半導体を用いたトランジスタを有するメモリに揮発性メモリのデータ内容をバックアップしておくことによって、データの保持時間を長くすることができる。

(もっと読む)

半導体装置

【課題】連想メモリは一つのメモリセル内の素子数が多く、一つのメモリセルの面積が大きくなりやすい。そこで、一つのメモリセルの面積を小さくする。

【解決手段】読み出し用のトランジスタのチャネル容量(ゲート電極とチャネル形成領域との間の容量)を用いて電荷の保持を行う。つまり、読み出し用のトランジスタを電荷保持用のトランジスタとして兼用する。また、読み出し用且つ電荷保持用のトランジスタのゲートに電荷供給用のトランジスタのソース又はドレインの一方を電気的に接続する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、を有し、駆動回路は、

データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置

【課題】特定のトランジスタのゲートの電位に応じて記憶情報の判別が行われる半導体装置において、当該トランジスタのしきい値電圧のばらつきの低減と、長期間に渡る情報の保持とを両立することで情報の保持特性に優れる半導体装置を提供すること。

【解決手段】チャネル領域が酸化物半導体によって形成されるトランジスタのソース又はドレインのみに電気的に接続されるノードにおいて電荷の保持(情報の記憶)を行う。なお、当該ノードにソース又はドレインが電気的に接続されるトランジスタは、複数であってもよい。また、当該酸化物半導体は、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い。このような酸化物半導体によってトランジスタのチャネル領域が形成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。

(もっと読む)

半導体装置

【課題】占有面積が小さく、冗長性があり、かつリーク電流の小さい保護回路を提供する。

【解決手段】保護回路は、複数の非線形素子が重畳するように積層され、かつ該非線形素子が電気的に直列接続されている構成であり、該保護回路に含まれる少なくとも一つの非線形素子は、チャネル形成領域に酸化物半導体を用いたトランジスタをダイオード接続した素子であり、他の非線形素子は、チャネル形成領域にシリコンを用いたトランジスタをダイオード接続した素子、または、接合領域にシリコンを用いたダイオードとする。

(もっと読む)

記憶装置、及び当該記憶装置を用いた半導体装置

【課題】DRAMよりも書き込み、読み出しなどの動作速度が高く、SRAMよりもメモリセルあたりの半導体素子の数を減らすことができる記憶装置。

【解決手段】制御装置と、演算装置と、緩衝記憶装置とを有し、緩衝記憶装置は、主記憶装置から、或いは演算装置から送られてきたデータを、制御装置からの命令に従って記憶し、緩衝記憶装置は複数のメモリセルを有し、メモリセルは、チャネル形成領域に酸化物半導体を含むトランジスタと、トランジスタを介してデータの値に従った量の電荷が供給される記憶素子とを有する。さらに、緩衝記憶装置が有する複数のメモリセルは、バリッドビットに対応するメモリセルが、データフィールドに対応するメモリセルよりも、そのデータの保持時間が短い。

(もっと読む)

半導体装置及びその駆動方法

【課題】信号処理回路に対する電源電圧の供給及び遮断を選択することができるスイッチとして機能する回路(電源供給制御回路)として好ましい回路を提供する。

【解決手段】信号処理回路に対する電源電位の供給を担う第1の配線と、電源電位を供給する第2の配線との電気的な接続を制御するトランジスタ、及び、信号処理回路に対する電源電位の供給を担う第1の配線を接地させるか否かを制御するトランジスタとを設け、当該2つのトランジスタの少なくとも一方として、チャネルが酸化物半導体層に形成されるトランジスタを適用する。これにより、2つのトランジスタの少なくとも一のカットオフ電流に起因する消費電力を低減することが可能となる。

(もっと読む)

121 - 140 / 1,051

[ Back to top ]