Fターム[5F102GJ04]の内容

接合型電界効果トランジスタ (42,929) | 基板 (5,097) | 半導体材料(半絶縁性材料も含む) (3,925) | 3−5族 (1,455)

Fターム[5F102GJ04]の下位に属するFターム

Fターム[5F102GJ04]に分類される特許

81 - 100 / 747

パワーデバイス

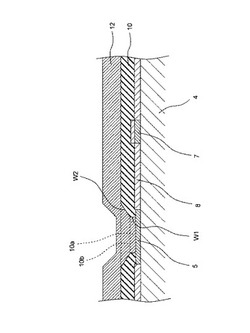

【課題】膜剥がれの要因となる有機材料を用いることなく、エレクトロマイグレーションの耐性と長期信頼性を向上できるパワーデバイスを提供する。

【解決手段】バリア層4(AlGaN)4上に形成された酸化シリコン(SiO2)からなる層間絶縁膜10と、層間絶縁膜10のソース電極5上に形成され、基板平面に対して略垂直な第1の側壁W1を有する第1コンタクトホール部10aと、第1コンタクトホール部10aの第1の側壁W1の上縁から上側に向かって徐々に広がるように層間絶縁膜10に形成され、基板平面に対して傾斜した第2の側壁W2を有する第2コンタクトホール部10bと、第1,第2コンタクトホール部10a,10b内および層間絶縁膜10上に形成された配線層12とを備える。上記配線層12は、第1コンタクトホール部10aにおいて第1の側壁W1の基板厚さ方向の寸法よりも膜厚が厚い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

パワーモジュールおよび電力変換回路

【課題】電力変換回路の性能を高める。

【解決手段】ユニット10は、半導体スイッチ素子1,2と、ダイオード3,4とを備える。ダイオード3は、半導体スイッチ素子2がオン状態である時に逆バイアスされ、半導体スイッチ素子2がオフ状態である時に導通する。ダイオード4は、半導体スイッチ素子1がオン状態である時に逆バイアスされ、半導体スイッチ素子1がオフ状態である時に導通する。ダイオード3,4は、窒化ガリウム(GaN)ダイオードまたはダイヤモンドダイオードである。ユニット10を備えるパワーモジュールは、コンバータ、インバータ等の電力変換回路に適用される。

(もっと読む)

窒化物半導体層のエッチング方法及びこれを用いた窒化物半導体装置の製造方法

【課題】高抵抗なダメージ層を形成しない窒化物半導体層のエッチング方法と、これを用いた低抵抗なオーミック電極を備える窒化物半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の窒化物半導体層のエッチング方法は、(a)窒化物半導体層に不純物イオンを注入し、その表面から所定深さまで不純物領域を形成する工程と、(b)前記不純物領域を熱処理する工程と、(c)前記不純物領域の前記表面側の所定領域をウェットエッチングで除去する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】InAlN電子供給層上にGaN層を形成する場合でも、InAlN電子供給層の品質の悪化を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、基板10上にGaN電子走行層14を形成する工程と、GaN電子走行層14上にInAlN電子供給層18を形成する工程と、InAlN電子供給層18を形成した後、In含有ガスを供給しつつ、基板10を昇温させる工程と、昇温が終了した後、InAlN電子供給層18上にGaN層20を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置

【課題】高周波数動作が可能な半導体装置を提供すること。

【解決手段】本発明は、基板10上に設けられたGaN電子走行層14と、GaN電子走行層14上に設けられたAlNスペーサ層16と、AlNスペーサ層16上に設けられたInAlN電子供給層18と、InAlN電子供給層18上に設けられたゲート電極24とゲート電極24を挟むソース電極26およびドレイン電極28と、を備え、AlNスペーサ層16の膜厚が、0.5nm以上1.25nm以下の半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】InAlN電子供給層上にGaN層を形成する場合でも、InAlN電子供給層の品質の悪化を抑制すること。

【解決手段】本発明は、基板10上にGaN電子走行層14を形成する工程と、GaN電子走行層14上にInAlN電子供給層18を形成する工程と、InAlN電子供給層18上に第1のGaN層20を形成する工程と、第1のGaN層20上に、InAlN電子供給層18および第1のGaN層20を形成した際の温度よりも高い温度で、第2のGaN層22を形成する工程と、InAlN電子供給層18上に、ゲート電極26と、ゲート電極26を挟むソース電極28およびドレイン電極30と、を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

化合物半導体装置

【課題】 電流コラプスを抑制するとともに、高耐圧動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】 SiC基板10上に形成されたi−GaNバッファ層12と、i−GaNバッファ層12上に形成されたn−AlGaN電子供給層16と、n−AlGaN電子供給層16上に形成されたn−GaNキャップ層18と、n−GaNキャップ層18上に形成されたソース電極20及ドレイン電極22と、ソース電極20とドレイン電極22との間のn−GaNキャップ層18上に形成されたゲート電極26と、ソース電極20とドレイン電極22との間のn−GaNキャップ層18上に形成された第1の保護層24と、ゲート電極26とドレイン電極22との間の第1の保護層24に形成されたn−GaNキャップ層18に達する開口部28に埋め込まれ、第1の保護層24とは異なる絶縁層よりなる第2の保護層30とを有する。

(もっと読む)

半導体エピタキシャル基板、およびその製造方法

【課題】

高周波信号遮断後の回復が早く、素子分離特性のよい化合物半導体エピタキシャル基板を提供する。

【解決手段】

半導体エピタキシャル基板は、単結晶基板と、単結晶基板上にエピタキシャル成長されたAlN層と、AlN層の上にエピタキシャル成長された窒化物半導体層とを有し、単結晶基板とAlN層間界面より、AlN層と窒化物半導体層間界面の方が凹凸が大きい、ことを特徴とする。

(もっと読む)

電界効果型トランジスタ

【課題】ゲート電極のドレイン端の電界を緩和し、ゲート絶縁膜の破損を低減する。

【解決手段】窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップエネルギーが大きい窒化物半導体で形成された電子供給層112と、チャネル層108の上方に形成されたソース電極116およびドレイン電極118と、チャネル層108の上方に形成されたゲート電極120と、チャネル層108の上方に形成され、チャネル層108からホールを引き抜くホール引抜部126と、ゲート電極120およびホール引抜部126を、電気的に接続する接続部124と、を備える電界効果型トランジスタ100。

(もっと読む)

GaNHEMT装置用再成長ショットキー構造

【課題】高温で動作可能な高電子移動度トランジスタを提供する。

【解決手段】バッファ層16と、バッファ層16上のIII−V族層18と、III−V族層18上のソース接点20およびドレイン接点22と、III−V族層18上で、ソース接点20およびドレイン接点22間の再成長ショットキー層10と、成長ショットキー層10上のゲート接点24、を備える装置、および装置を用いたシステムを含む。さらに、装置とシステムの製造方法も含む。

(もっと読む)

窒化物半導体装置および窒化物半導体装置の製造方法

【課題】オン抵抗が低く、かつ、Vth(閾値電圧)が高い窒化物半導体装置の提供。

【解決手段】アクセプタになるアクセプタ元素を含み、窒化物半導体で形成されたバックバリア層106と、バックバリア層106上に窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップが大きい窒化物半導体で形成された電子供給層112と、チャネル層108と電気的に接続された第1主電極116、118と、チャネル層108の上方に形成された制御電極120と、を備え、バックバリア層106は、制御電極120の下側の領域の少なくとも一部に、アクセプタの濃度がバックバリア層の他の一部の領域より高い高アクセプタ領域126を有する窒化物半導体装置100。

(もっと読む)

スイッチ装置

【課題】オン抵抗を小さく抑えながらも、スイッチ素子の駆動に必要な電力を小さく抑えることができるスイッチ装置を提供する。

【解決手段】スイッチ装置1は、スイッチ素子10のドレイン電極12とソース電極13との間を流れるドレイン電流Idsを計測する電流モニタ部23を駆動回路20に備えている。制御部22は、スイッチ素子10がオンしている状態において、スイッチ素子10のオン抵抗が規定値以下になるように電流モニタ部23の計測値(ドレイン電流Ids)に応じてゲート電圧Vgsの下限値を設定する。制御部22は、設定した下限値を下回らない範囲で、電圧印加部21から印加可能な最小の大きさにゲート電圧Vgsを調節する。電圧印加部21は、制御部22に制御され、制御部22で決定された大きさのゲート電圧Vgsをスイッチ素子10に印加する。

(もっと読む)

半導体装置

【課題】高電圧を印加しても短絡破壊を生じないトランジスタとして動作する半導体装置を提供する。

【解決手段】半導体装置1は、基板10(シリコン基板10a)の上に形成されたバッファ層21と、バッファ層21の上に形成されたチャネル層22と、チャネル層22の上に形成され、チャネル層22とヘテロ接合を構成する障壁層23とを備える。バッファ層21およびチャネル層22は、窒化物半導体で形成されている。チャネル層22は、膜厚を1μm以上2μm以下とされ、炭素濃度を5×1016cm-3以下とされている。

(もっと読む)

電界効果トランジスタ

【課題】動的な耐圧であるダイナミック耐圧の低下を抑制できるGaN系のHFETを提供する。

【解決手段】このGaN系のHFETでは、2次元電子ガス除去領域260Bが、ドレイン電極211の長手方向の一方の端211Aから短手方向に伸ばした仮想線M71よりも長手方向外方に位置すると共にソース電極212の一端部212Aに対して短手方向に隣接する領域の下のGaN系積層体205に形成されている。また、2次元電子ガス除去領域260Aは、2次元電子ガス除去領域260Bの長手方向外方に隣接すると共にソース電極212の一端部212Aからソース電極接続部214に沿って短手方向に延在している。2次元電子ガス除去領域260A,260Bの存在によって、スイッチング時の動的な電界変動によってソース電極212の端部212Aからドレイン電極211の端部211Aへ向かって電子流が集中することを回避できる。

(もっと読む)

電界効果トランジスタ

【課題】動的な耐圧であるダイナミック耐圧の低下を抑制できるGaN系のHFETを提供する。

【解決手段】このGaN系のHFETでは、ドレイン電極12の長手方向の端12A,12Bから長手方向と直交する短手方向に伸ばした仮想線M1,M2よりも長手方向外方に位置すると共にソース電極11に隣接する領域の下のGaN系積層体5、およびドレイン電極12の長手方向の端12A,12Bに長手方向外側に隣接する領域の下のGaN系積層体5に2次元電子ガスが存在しない2次元電子ガス除去領域31が形成されている。2次元電子ガス除去領域31の存在によって、スイッチング時の動的な電界変動によってソース電極11の端部からドレイン電極12の端部へ向かって電子流が集中することを回避できる。

(もっと読む)

電界効果トランジスタ

【課題】動的な耐圧であるダイナミック耐圧の低下を抑制できるGaN系のHFETを提供する。

【解決手段】このGaN系のHFETでは、各ソース電極12の長手方向の長さL2と各ドレイン電極11の長手方向の長さL1とが同じ長さである。また、ソース電極12の長手方向の端12A,12Bの長手方向の位置は、ドレイン電極11の長手方向の端11A,11Bの長手方向の位置と一致している。ソース電極12の長手方向の両端12A,12Bがドレイン電極11の長手方向の両端11A,11Bよりも長手方向外方へ突出していない構成により、ソース電極12の端12A,12Bからドレイン電極11の端11A,11Bへ向かって電子流が集中することを回避できる。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】電流コラプスを低減し、ドレイン電流を増大しながら、ゲートリーク電流を減少できるようにする。

【解決手段】半導体装置は、基板1と、基板1の上に形成されたIII族窒化物からなる半導体層2、3と、半導体層2、3の上に、それぞれ形成されたソース電極5、ゲート電極7及びドレイン電極6と、半導体層2、3の上に、ゲート電極7の下部及び半導体層2、3と接し、且つ、ソース電極5及びドレイン電極6と離間するように形成されたシリコンを含まない第1保護膜8と、半導体層2、3の上に、半導体層2、3と接し且つゲート電極7の下部と離間するように形成され、第1保護膜8と組成が異なり且つ窒素を含む第2保護膜9とを備えている。

(もっと読む)

トランジスタ

【課題】耐圧特性に優れた高電子移動度トランジスタ(HEMT)を提供する。

【解決手段】基板12上に形成された複数の活性半導体層16、18を含むHEMT10。ソース電極20、ドレイン電極22、およびゲート24は、複数の活性層16、18と電気的に接触して形成される。スペーサ層26は、複数の活性層16、18の表面の少なくとも一部の上に形成され、ゲート24を覆っている。フィールドプレート30が、スペーサ層26上に形成されて、ソース電極22に電気的に接続され、このフィールドプレート30はHEMT10内の最高動作電界を低減する。

(もっと読む)

81 - 100 / 747

[ Back to top ]