Fターム[5F102GJ04]の内容

接合型電界効果トランジスタ (42,929) | 基板 (5,097) | 半導体材料(半絶縁性材料も含む) (3,925) | 3−5族 (1,455)

Fターム[5F102GJ04]の下位に属するFターム

Fターム[5F102GJ04]に分類される特許

101 - 120 / 747

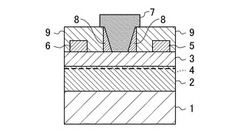

半導体装置

【課題】電流コラプスを低減し、ドレイン電流を増大しながら、ゲートリーク電流を減少できるようにする。

【解決手段】半導体装置は、基板1と、基板1の上に形成されたIII族窒化物からなる半導体層2、3と、半導体層2、3の上に、それぞれ形成されたソース電極5、ゲート電極7及びドレイン電極6と、半導体層2、3の上に、ゲート電極7の下部及び半導体層2、3と接し、且つ、ソース電極5及びドレイン電極6と離間するように形成されたシリコンを含まない第1保護膜8と、半導体層2、3の上に、半導体層2、3と接し且つゲート電極7の下部と離間するように形成され、第1保護膜8と組成が異なり且つ窒素を含む第2保護膜9とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】水素を用いた熱分解において、水素濃度を規定してエッチング速度を制御することで、半導体装置の製造方法の加工精度を向上させる。

【解決手段】半導体装置1の製造方法は、基板10に窒化物半導体で形成された第1層(障壁層25)および第2層(キャップ層26)を順に堆積させる堆積工程と、窒素および水素の混合雰囲気中で加熱して第2層をエッチングする熱エッチング工程とを備える。熱エッチング工程では、水素濃度が1%以上20%以下であることが望ましい。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、耐圧が高いノーマリーオフの半導体装置を提供する。

【解決手段】基板102の上方に形成された、III−V族化合物半導体からなるバックバリア層106と、バックバリア層106上に形成され、バックバリア層よりバンドギャップエネルギーが小さいIII−V族化合物半導体からなるチャネル層と108、チャネル層108にオーミック接続された第1の電極116,118と、チャネル層の上方に形成された第2の電極120と、を備え、バックバリア層106は第2の電極120の下方に設けられ、かつ、第2の電極120の下方から第1の電極の116,118下方まで連続して設けられていない半導体装置を提供する。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、Vthが高い半導体装置を提供する。

【解決手段】基板102の上方に、III−V族化合物半導体で形成されたバックバリア層106と、バックバリア層106上に、バックバリア層106よりバンドギャップエネルギーが小さいIII−V族化合物半導体で形成され、バックバリア層106の上方の少なくとも一部に設けられたリセス部122において、他の部分より膜厚が薄いチャネル層108と、チャネル層108にオーミック接合された第1の電極116,118と、少なくともリセス部においてチャネル層の上方に形成された第2の電極120と、を備える半導体装置を提供する。

(もっと読む)

半導体装置

【課題】電流コラプスが抑制され、耐圧の高い半導体装置を提供する。

【解決手段】基板110と、基板110の上方に形成された窒化物系化合物半導体からなるバッファ層120と、バッファ層120上に形成された窒化物系化合物半導体からなるチャネル層130と、チャネル層130の上方に形成された窒化物系化合物半導体からなる電子供給層132と、電子供給層132の上方に形成された第1の電極136と、電子供給層132の上方に形成された第2の電極138と、を備え、第2の電極138の電位に対して、基板110の電位および第1の電極136の電位が同じ側であり、第2の電極138の下の領域のバッファ層120の厚さおよびチャネル層130の厚さの合計が、第1の電極136の下の領域のバッファ層120の厚さおよびチャネル層130の厚さの合計より、大きい半導体装置。

(もっと読む)

半導体装置

【課題】窒化物半導体を用いた半導体装置のオン抵抗を低減できるようにする。

【解決手段】半導体装置は、アンドープのAlGaN層104と、該AlGaN層104の上に形成され、AlGaN層104とオーミック接触するソース電極107及びドレイン電極108とを有している。AlGaN層104の上部における少なくとも各電極107、108と接触する部分には、不純物拡散層110が形成されている。不純物拡散層110は、AlGaN層104に対しアクセプタ性を示す不純物が拡散し、且つ、AlGaN層104における窒素空孔と不純物とが結合してなる不純物準位が、AlGaN層104の伝導帯端の近傍に形成される。

(もっと読む)

半導体デバイス

【課題】低シート抵抗化、リーク電流の低減、および、オーミック電極の接触抵抗の低減を実現する。

【解決手段】基板と、基板上に設けられ第1の窒化物系化合物半導体からなるチャネル層と、チャネル層上に設けられたバリア層と、バリア層上に設けられた第1電極と、チャネル層の上方に設けられた第2電極とを備え、バリア層は、チャネル層上に設けられ第1の窒化物系化合物半導体よりバンドギャップエネルギーが大きい第2の窒化物系化合物半導体からなる障壁層と、第2の窒化物系化合物半導体よりバンドギャップエネルギーが小さい第3の窒化物系化合物半導体からなり量子準位が形成された量子準位層とを有する半導体デバイスを提供する。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】良好なオン特性を維持したまま、逆方向バイアスに対するリーク電流を低減した半導体デバイスを得る。

【解決手段】窒化物系化合物半導体からなるチャネル形成層と、チャネル形成層上に設けられ、第1の窒化物系化合物半導体からなる第1の半導体層、および、第2の窒化物系化合物半導体からなる第2の半導体層を有する疑似混晶からなる疑似混晶層と、疑似混晶層上に設けられ、窒化物系化合物半導体からなり、チャネル形成層の多数キャリアと反対の導電型を有する導電半導体層と、導電半導体層に接する第1の電極と、チャネル形成層に電気的に接続された第2の電極と、を備える半導体デバイスを提供する。

(もっと読む)

半導体装置

【課題】基板の反りを抑制しつつ、バッファ層及び化合物半導体の厚さを稼ぐことができ、素子耐圧を向上することができる半導体装置を提供する。

【解決手段】半導体装置は、基板2と、バッファ層3と、窒化物系化合物半導体4とを備える。バッファ層3は、AlN層とGaN層とを積層した第1のバッファ領域321,331と、GaN層を有する第2のバッファ領域322,332とを交互に積層して構成される。バッファ層3において窒化物系化合物半導体4側の第1のバッファ領域331とそれに隣接する第2のバッファ領域332との1組の全体のAl組成は基板側の1組のAl組成に対して大きく設定されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 高周波特性を確保し、サイズを小型化し、かつ製造が容易な、正孔の蓄積を解消できる、耐圧性に優れた、半導体装置等を提供する。

【解決手段】 ヘテロ接合電界効果トランジスタ(HFET:Hetero-junction Field Effect Transistor)であって、非導電性基板1上に位置する、チャネルとなる二次元電子ガス(2DEG:2 Dimensional Electron Gas)を形成する再成長層7(5,6)と、再成長層に接して位置する、ソース電極11、ゲート電極13およびドレイン電極15を備え、ソース電極11が、ゲート電極13に比べて、非導電性基板1から遠い位置に位置することを特徴とする。

(もっと読む)

半導体発光素子

【課題】平坦性が向上した半導体基板を基礎として、特性の高性能化された半導体発光素子を提供する。

【解決手段】p型電極32と、n型電極31と、p型電極32に接続され、複数のp型窒化物系III−V族化合物半導体からなるp型積層構造(16〜20)と、n型電極31に接続され、複数のn型窒化物系III−V族化合物半導体であるn型積層構造(11〜14)と、p型積層構造(16〜20)とn型積層構造(11〜14)との間に形成されたInGaNからなる多重井戸構造を備える活性層15とを備え、n型積層構造が、GaN層11と、GaN層11上に形成されたドープ層10と、ドープ層10上に設けられた窒化物系III−V族化合物半導体層12と、窒化物系III−V族化合物半導体層12よりも活性層15側に設けられた超格子層13とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】電子移動度の低下が抑制され、かつ二次元電子ガスの閉じ込めが高められた半導体装置およびその製造方法を提供する。

【解決手段】AlaInbGa1-(a+b)N(0≦a,b≦1、0≦a+b≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが大きい第1の窒化物半導体層2、AlcIndGa1-(c+d)N(0≦c,d≦1、0≦c+d≦1)から成る第2の窒化物半導体層3、IneGa1-eN(0<e≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが小さいバックバリア層4、AlfIngGa1-(f+g)N(0≦f,g≦1、0≦f+g≦1)から成り、第2の窒化物半導体層3とバンドギャップが等しいチャネル層5、AlhIniGa1-(h+i)N(0≦h,i≦1、0≦h+i≦1)から成り、チャネル層5よりもバンドギャップが大きいバリア層6を、この順に基板1に積層する。

(もっと読む)

半導体装置の製造方法

【課題】膜の形成によって生じる半導体基板の反りを緩和できる、半導体装置の製造方法を提供する。

【解決手段】SiC半導体基板10の主面上にイオン注入用マスク材18を形成する。マスク材は半導体基板とは異なる熱膨張係数を有する。レジスト膜20をマスクとしてドライエッチングにより複数の装置形成領域の間の領域上(ダイシングライン)14に切欠き部16aを有するマスク用膜16を形成する。イオン注入などの工程を経て半導体装置を形成後、ダイシングラインに沿って各装置形成領域に分離する。

(もっと読む)

半導体装置

【課題】窒化物半導体により、反転型のHEMTが構成された半導体装置において、半導体装置の形成を容易としつつ2DEGを効果的に形成する。

【解決手段】窒化物半導体からなる下地層15の(0001)面上に、窒化物半導体からなる電子供給層17、窒化物半導体からなる電子走行層19の順に積層され、電子走行層19における電子供給層17と反対の面上に、ゲート電極21、ソース電極23、及びドレイン電極25が設けられている。そして、電子走行層19における電子供給層17側に、二次元電子ガスが形成される。このような反転型のHEMTが構成された半導体装置10において、分極の正方向を[0001]方向とした場合、電子供給層17の自発分極とピエゾ分極の和P2が、電子走行層19の自発分極とピエゾ分極の和P1よりも大きくなっている。

(もっと読む)

アクティブ発振防止付き複合半導体デバイス

【課題】アクティブ発振防止付き複合半導体デバイスを提供する。

【解決手段】本明細書は、アクティブ発振制御付き複合半導体デバイスの種々の実現を開示する。1つの好適な実現では、ノーマリオフ複合半導体デバイスが、ノーマリオンIII-窒化物パワートランジスタ、及びこのノーマリオンIII-窒化物パワートランジスタとカスコード接続された低電圧(LV)デバイスを具えて、ノーマリオフ複合半導体デバイスを形成する。このLVデバイスは、例えば修正したボディ打込み領域により低減した出力抵抗、及び例えば修正した酸化物の厚さにより低減したトランスコンダクタンスの一方または両方を含むように構成されて、複合半導体デバイスのゲインを約10,000以下にすることができる。

(もっと読む)

複合GaN基板およびその製造方法、ならびにIII族窒化物半導体デバイスおよびその製造方法

【課題】高特性かつ手頃な価格の複合GaN基板およびその製造方法ならびにIII族窒化物半導体デバイスおよびその製造方法を提供する。

【解決手段】本複合GaN基板1は、比抵抗が1Ωcm未満の導電性GaN基板10と、導電性GaN基板10上に配置された比抵抗が1×104Ωcm以上で厚さが5μm以上の半絶縁性GaN層20と、を含む。本III族窒化物半導体デバイス2は、上記の複合GaN基板1と、複合GaN基板1の半絶縁性GaN層20上に配置された少なくとも1層のIII族窒化物半導体層30と、を含む。

(もっと読む)

トランジスタデバイスおよび高電子移動度トランジスタ(HEMT)

【課題】デバイス利得、帯域幅、および動作周波数が増加するトランジスタを提供する。

【解決手段】第1のスペーサ層28が、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間の活性領域の表面の少なくとも一部の上にある。ゲート電極24は、ソース電極20とドレイン電極22に向かって延在する一般的にT字型の頂部34を備える。フィールドプレート32は、スペーサ層28の上であって、ゲート頂部34の少なくとも1つの区域のオーバーハングの下にある。第2のスペーサ層30は、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間にある第1のスペーサ層28の少なくとも一部の上と、フィールドプレート32の少なくとも一部の上に形成される。少なくとも1つの導電性経路が、フィールドプレート32をソース電極20またはゲート電極24に電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】オン抵抗が小さく、またオフ容量が低い、デュアルゲートを備えた電界効果トランジスタを提供する。

【解決手段】第1又は第2のゲート電極8は、ソース電極4側又は前記ドレイン電極5側に延びる第1のひさし部61と、第2又は第1のゲート電極8側に延びる第2のひさし部62とを有し、第2のひさし部62の長さが第1のひさし部61の長さより短い。

(もっと読む)

半導体装置

【課題】マルチフィンガーFETセル内のループ発振を抑制させ、かつチップ面積の増大を抑制する。

【解決手段】ユニットフィンガーの並列接続からなるマルチフィンガー単位FETセルと、マルチフィンガー単位FETセルのゲートフィンガーを並列接続する指定ゲートバスラインと、指定ゲートバスラインに接続されたゲート引き出しラインとを備え、ゲート引き出しラインと指定ゲートバスラインの接続点をマルチフィンガー単位FETセル内の中心からずらすことによって、接続点の一方に接続されたゲートフィンガー数が、他方に接続されたゲートフィンガー数よりも多くする。

(もっと読む)

MMIC用パッケージ

【課題】チップサイズの大きい高周波部品(MMIC)とパッケージ端子間を接続するインダクタンス成分を抑制し、高周波特性を改善したMMIC用パッケージを提供する。

【解決手段】導体ベースプレート200と、導体ベースプレート200上に配置され、入力端子24aおよび出力端子24bを有するMMIC基板24と、導体ベースプレート200上に配置され、MMIC基板24を囲むセラミック枠体180と、セラミック枠体180上に配置されたパッケージ入力端子21aおよびパッケージ出力端子21bと、MMIC基板24とセラミック枠体180との間の導体ベースプレート200上に配置された結合用基板25と、結合用基板25上に配置された結合ライン25aとを備え、パッケージ入力端子21aと結合ライン25a間、および結合ライン25aと入力端子24a間とが接続されている。

(もっと読む)

101 - 120 / 747

[ Back to top ]