Fターム[5F102GJ04]の内容

接合型電界効果トランジスタ (42,929) | 基板 (5,097) | 半導体材料(半絶縁性材料も含む) (3,925) | 3−5族 (1,455)

Fターム[5F102GJ04]の下位に属するFターム

Fターム[5F102GJ04]に分類される特許

141 - 160 / 747

窒化物半導体素子の製造方法

【課題】ドレインリーク電流を低減することが可能な窒化物半導体素子の製造方法を提供する。

【解決手段】ヘテロ電界効果トランジスタ1の製造方法は、ドリフト層20aを支持基板10上にエピタキシャル成長させる工程と、水素ガスをキャリアガスとして用いて、p型半導体層である電流ブロック層20bをドリフト層20a上に1000℃以上でエピタキシャル成長させる工程と、窒素ガス、アルゴンガス、ヘリウムガス及びネオンガスからなる群より選ばれる少なくとも一種のガスをキャリアガスとして用いて、コンタクト層20cを電流ブロック層20b上にエピタキシャル成長させる工程と、を備える。

(もっと読む)

半導体装置

【課題】 オン抵抗の増大を抑制しつつ、耐圧の低下を抑制する技術を提供する。

【解決手段】 ノーマリオフ型の半導体装置100は、ヘテロ接合を構成する半導体層16と、第1リセス部8と、第1リセス部8よりも浅い第2リセス部4と、ゲート部5を備えている。半導体層16は、第1半導体層12と、第1半導体層12上に設けられているとともに第1半導体層12よりもバンドギャップが広い第2半導体層14を有している。第2リセス部4は、第2半導体層14を貫通していない。第2リセス部4の下方に位置する第2チャネル部C2は、第1リセス部8の下方に位置する第1チャネル部C1よりも電流経路20の上流側に配置されている上流側第2チャネル部C2uを有する。

(もっと読む)

高電子移動度トランジスタ(HEMT)

【課題】高周波特性を改善する。

【解決手段】III族窒化物系高電子移動度トランジスタ(HEMT)20は、GaNバッファ層26を備えており、Ganバッファ層26上にAlyGa1−yN(y=1又は≒1)層28がある。AlxGa1−xN(0≦x≦0.5)バリア層30が、GaNバッファ層26の反対側でAlyGa1−yN層28上にあり、該層28のAl濃度は、バリア層30よりも高い。GaNバッファ層26とAlyGa1−yN層28との間の界面に2DEG38が形成されている。バリア層30上に、ソース、ドレイン、及びゲート・コンタクト32、34、36が形成されている。また、AlyGa1−yN層28の反対側において、バッファ層26に隣接する基板22も含み、GaNバッファ層26と基板22との間に、核生成層24を含むことができる。

(もっと読む)

半導体素子

【課題】低オン抵抗で、ノーマリーオフ動作を有し、高信頼性の半導体素子を提供する。

【解決手段】半導体素子1Aは、支持基板10上にN面成長されたAlXGa1−XN(0≦X<1)を含む第1半導体層11と、前記第1半導体層上に形成されたノンドープもしくは第1導電形のAlYGa1−YN(0<Y≦1、X<Y)を含む第2半導体層15と、前記第2半導体層上に形成されたAlZGa1−ZN(0≦Z<1、Z<Y)を含む第3半導体層16と、を備える。半導体素子1Aは、第3半導体層16に接続された第1主電極20と、第3半導体層16に接続された第2主電極21と、第1主電極と第2主電極とのあいだの第3半導体層16の上に設けられたゲート電極31と、を備える。第3半導体層16の厚さは、ゲート電極31下において選択的に薄い。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

p型のIII族窒化物半導体層を含む半導体装置とその製造方法

【課題】p型のIII族窒化物半導体層を含む積層構造を利用して複数個の半導体装置を製造し、エッチング等して個々の半導体装置に分割すると、個々の半導体装置の側面に露出するp型のIII族窒化物半導体層の表面に沿ってリ−ク電流が流れてしまう。

【解決手段】p型のIII族窒化物半導体層8を含む積層構造の表面または裏面からp型のIII族窒化物半導体層8に達しない深さまでエッチングまたはダイシングし、残った厚みをへき開して個々の半導体装置に分割する。半導体装置の側面に露出するp型のIII族窒化物半導体層8の表面はへき開面となり、結晶欠陥が少なく、側面に沿ってリ−ク電流が流れることを防止する。

(もっと読む)

パッケージ

【課題】導体ベースプレートと金属外壁との熱膨張係数が異なることに伴う、銀ロウ付けする際の導体ベースプレートの反りを抑制したパッケージを提供する。

【解決手段】導体ベースプレートと、導体ベースプレート上に配置された半導体装置と、半導体装置を内在し、導体ベースプレート上に配置され、導体ベースプレートと接する面に複数の開放部を有する金属壁と、開放部を充填するブロックとを備えるパッケージ。

(もっと読む)

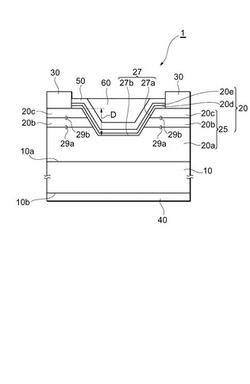

トランジスタ装置

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能

するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース、ドレ

イン、およびゲートを含む。第1のスペーサ層が、活性領域の上方でソースとゲートの間

にあり、第2のスペーサ層が、活性領域の上方でドレインとゲートの間にある。第1のス

ペーサ層上の第1のフィールドプレート、及び第2のスペーサ層上の第2のフィールドプ

レートが、ゲートに接続される。第3のスペーサ層が、第1のスペーサ層、第2のスペー

サ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、

第3のフィールドプレートが、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

【課題】埋込み部を形成する際のエッチングにより埋込みゲートが損傷をきたし、ゲート領域劣化が生じ得る。

【解決手段】ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。

(もっと読む)

半導体デバイスの製造方法およびエピタキシャル成長用の支持基板

【課題】中間層の一部が露出している支持基板であっても、それに適切な処理を加えることにより、半導体デバイスを歩留まりよく製造することができる半導体デバイスの製造方法およびエピタキシャル成長用の支持基板を提供する。

【解決手段】本半導体デバイスの製造方法は、少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させることができる下地基板10と、下地基板10上に全面的に配置された中間層20と、中間層20上に部分的に配置されたGaN層30aとを含み、GaN層30aと中間層20の一部とが露出している支持基板2を形成する工程と、支持基板2の中間層20が露出している部分20p,20q,20rを選択的に除去することにより、下地基板10の一部を露出させる工程と、GaN層30a上に、III族窒化物半導体層をエピタキシャル成長させる工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】電界集中を緩和させることにより、高耐圧、高信頼性を得ることが可能な半導体装置とその製造方法を提供する。

【解決手段】本発明の実施形態は、半導体基板と、半導体基板上に設けられるゲート電極と、ゲート電極を挟んで半導体基板上に設けられるソース電極及びドレイン電極と、ゲート電極の少なくともドレイン電極側のエッジの下部に設けられるリセスと、を備える。

(もっと読む)

半導体装置

【課題】電流コラプスの発生を抑制できるIII族窒化物半導体トランジスタおよびその製造方法を提供する。

【解決手段】FET1では、第1窒化物半導体層103の上に第2窒化物半導体層104が設けられ、少なくとも一部が第2窒化物半導体層104に接するようにソース電極106およびドレイン電極107が設けられている。第2窒化物半導体層104の上面においてソース電極106とドレイン電極107との間に位置するように凹部110aが形成されており、ゲート電極108が凹部110aの開口を覆うように凹部110aの上方に設けられている。

(もっと読む)

半導体装置、試験装置、および製造方法

【課題】電流電圧のパルス特性を向上させて電流電圧のDC特性に近づける。

【解決手段】半導体層と、半導体層上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、ゲート絶縁膜上に設けられ、ゲート絶縁膜上におけるゲート電極の端部の少なくとも一部においてゲート電極と接するゲート境界膜と、を備え、ゲート境界膜およびゲート絶縁膜は、同種の絶縁材料を含む半導体装置を提供する。ゲート電極およびゲート境界膜上に設けられた絶縁性の保護膜を更に備え、保護膜は、ゲート境界膜およびゲート絶縁膜とは別種の絶縁材料を含んでよい。

(もっと読む)

高電子移動度トランジスタ

【課題】ノーマリオフ特性を得つつスイッチング特性が向上した高電子移動度トランジスタ(HEMT)を提供する。

【解決手段】窒化物半導体からなるHEMT100は、n型不純物を含むか又はアンドープの第1層103と、第1層上に設けられ第1層よりもバンドギャップエネルギーが大きい第2層105と、第2層上に設けられp型不純物を含む第3層106と、第3層上に設けられ下側から上側に向かってバンドギャップエネルギーが小さくなっている第4層107と、を有する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を容易に実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1上方に形成されたAlGaN層3と、AlGaN層3上に形成されたAlGaN層4と、AlGaN層4上に形成された電子走行層5と、電子走行層5上方に形成された電子供給層6と、が設けられている。AlGaN層3の組成をAlx1Ga1-x1N、AlGaN層4の組成をAlx2Ga1-x2Nと表すと、「0≦x1<x2≦1」の関係が成り立つ。AlGaN層4の上面には、AlGaN層4の下面に存在する正の電荷よりも多くの負の電荷が存在している。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体層のクラックをより一層低減することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基材1と、基材1の上方に形成された初期層2と、初期層2上に形成され、III−V族化合物半導体を含むコア層3と、が設けられている。初期層3として、コア層3に含まれるIII-V族化合物半導体のIII族原子の層が形成されている。

(もっと読む)

半導体発光素子

【課題】GaN基板上に結晶成長する各半導体層の平坦性向上した半導体基板を実現し、この半導体基板を基礎として、特性の高性能化された半導体発光素子を提供する。

【解決手段】p型電極32と、n型電極31と、p型電極32に接続され、複数のp型窒化物系III−V族化合物半導体からなるp型積層構造(16〜20)と、n型電極31に接続され、複数のn型窒化物系III−V族化合物半導体であるn型積層構造(11〜14)と、p型積層構造(16〜20)とn型積層構造(11〜14)との間に形成された窒化物系III−V族化合物半導体からなる活性層15とを備え、n型積層構造(11〜14)がSiを5x1017cm-3以上2x1019cm-3以下の濃度で含有し、厚さが0.3nm以上200nm以下のドープ層10と、ドープ層10よりも活性層15側に設けられた超格子層13とを含む。

(もっと読む)

III族窒化物半導体装置

【課題】p型III族窒化物半導体62の上面からn型III族窒化物半導体64に到達する溝が形成されている場合、p型III族窒化物半導体の側面62aが露出する。p型III族窒化物半導体の露出面62aはn型化しやすく、露出面に沿ってリーク電流が流れやすい。

【解決手段】p型III族窒化物半導体62中に存在する正孔を露出面62aに誘導する正孔誘導手段を設ける。例えば、露出面62aを被覆する絶縁膜66に負電荷蓄積領域68を設ける。負電荷蓄積領域68が、p型III族窒化物半導体中に存在する正孔を露出面62aに誘導し、露出面がn型化して露出面に沿ってリーク電流が流れることを防止する。

(もっと読む)

高周波回路

【課題】最小ループと2セルループのオッドモード発振を共に抑制する高周波回路を提供する。

【解決手段】半導体基板上に並列に配列された複数のトランジスタと、第1の絶縁基板上に配置され、複数のトランジスタのゲート端子電極にそれぞれ接続された複数の入力整合回路と、第1の絶縁基板上に配置され、入力整合回路に隣接して配置された入力側第4発振抑制抵抗と、入力側第4発振抑制抵抗に直列接続された入力側第1キャパシタと、隣接する入力整合回路間を繋ぐ伝送線路上の点と入力側第1キャパシタ間に接続された入力側第1インダクタとを有する入力側発振抑制回路とを備え、入力側第1インダクタのインダクタンス値をL1、入力側第1キャパシタのキャパシタンス値をC1とすると、1/{2π(L1×C1)1/2}で表される入力側第1インダクタと入力側第1キャパシタの共振周波数が、2セルループの発振周波数fosc2に等しい高周波回路。

(もっと読む)

141 - 160 / 747

[ Back to top ]