Fターム[5F102GL02]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | 単一半導体層 (2,547) | 4族 (280)

Fターム[5F102GL02]の下位に属するFターム

Si (112)

Fターム[5F102GL02]に分類される特許

41 - 60 / 168

異なる半導体材料の半導体相互接続層及び半導体チャネル層を備えたトランジスタ

トランジスタが、第1の半導体材料の半導体ドリフト層と、この半導体ドリフト層上の半導体チャネル層とを含むことができる。半導体チャネル層は、第1の半導体材料とは異なる第2の半導体材料を含むことができる。半導体ドリフト層と半導体チャネル層の間には、第1及び第2の半導体材料とは異なる第3の半導体材料を含むことができる半導体相互接続層を電気的に結合することができる。また、半導体チャネル層上には、制御電極を設けることができる。 (もっと読む)

ダイヤモンド電界効果トランジスタ

【課題】本発明の目的は、大電流動作が可能となり、さらに大電流動作を高温環境下でも安定に維持でき、また、ノーマリーオン特性とノーマリーオフ特性を作り分けることが可能となり、低消費電力で動作させることができるダイヤモンド電界効果トランジスタを提供する。

【解決手段】P型ダイヤモンド上に、少なくともAl、Ga、B、Inの1つを含むP型窒化物層を有し、P型ダイヤモンドとP型窒化物層との間のヘテロ接合に電気的にオーミック接触するソース電極およびドレイン電極と、ソース電極とドレイン電極との間のP型窒化物層上にゲート電極を有することを特徴とする。

(もっと読む)

電気回路中にて静電気放電保護素子として用いるためのゲート制御されたフィン型抵抗素子、および、電気回路内部を静電気放電から保護するための保護装置

【課題】電気回路中にて静電気放電保護を確実化しながら小型化を実現する。

【解決手段】電気回路において静電気放電保護素子として使用するためのゲート制御されたフィン型抵抗素子は、第1端子領域、第2端子領域、および、第1端子領域と第2端子領域との間に形成されたチャネル領域を有するフィン構造体を備えている。さらに、フィン型抵抗素子は、チャネル領域の上面の一部上に少なくとも形成されたゲート領域を備えている。ゲート領域は、ゲート制御部に電気的に結合されており、ゲート制御部は、ゲート領域に印加される電気的な電位を制御することにより、電気回路が第1動作状態である間は、ゲート制御されたフィン型抵抗素子の電気抵抗を高くし、静電気放電現象の開始によって特徴付けられている第2動作状態では、電気抵抗をより低くする。

(もっと読む)

炭化ケイ素半導体構造体、デバイス及びその製造方法

【課題】炭化ケイ素(SiC)を含む半導体構造体(100)及びデバイスと、その製造方法を提供すること。

【解決手段】構造体(100)及びデバイスは、ベース又はシールド層(116)、チャネル(118)及び表面層(120)を備え、望ましくはすべてイオン注入によって形成される。その結果として本明細書に示す構造体及びデバイスは、ハードな「ノーマリオフ」デバイスであり、即ち約3V超の閾値電圧を示す。

(もっと読む)

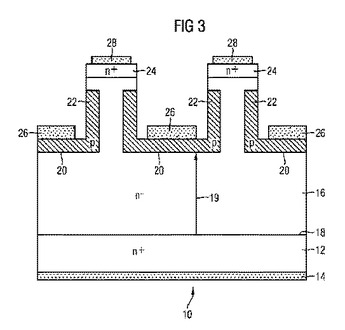

単極半導体部品と半導体装置の製造方法

本発明は、ドリフト層(16)を有する単極半導体部品の製造方法であって、少なくとも1つの広いバンドギャップ材料を含むドリフト層(16)の材料のエピタキシャル析出を手段として、ドリフト層(16)の成長方向(19)に沿って連続的に低下する電荷キャリアドーピング(n)の濃度を有するドリフト層(16)を形成する工程を含む方法に関する。エピタキシャル析出により形成されるドリフト層(16)に炭化ケイ素を使用することにより、下流工程におけるドープ材原子の拡散による電荷キャリアドーピング(n)の連続的に低下する濃度のその後の変化を抑制する。製造方法は特に、単純なおよび/または費用効果的なやり方で、ドリフト層(16)を含む単極半導体部品であって比較的低い順方向損失と比較的高い逆バイアス電圧との有利な比を有する単極半導体部品を実装するために使用されることができる。単極半導体部品は能動半導体部品または受動半導体部品であることができる。本発明はさらに、半導体装置(10)に関する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのSBD10は、半導体からなる基板11と、基板11上に形成されたn型層12と、n型層12上に配置されたアノード電極14と、アノード電極14に接続され、n型層12に突出するp型領域13とを備えている。p型領域13は、n型層12との境界領域において、境界領域に隣接するp型領域13内の領域である高不純物領域13Bよりも導電型がp型であるp型不純物の濃度の低い低不純物領域13Aを含んでいる。

(もっと読む)

傾斜ドープ領域を有する縦型接合電界効果トランジスターおよびダイオードならびに製造方法

半導体装置および装置を製造する方法が記載される。前記装置は、接合障壁ショットキー(JBS)ダイオードまたはPiNダイオードなどの、接合電界効果トランジスター(JFET)またはダイオードであり得る。前記装置は、エピタキシャル成長によって形成された、傾斜したp型半導体層及び/又はp型半導体領域を有する。前記方法は、イオン注入を必要としない。前記装置は、炭化ケイ素(SiC)などの広バンドギャップの半導体材料から製造され得、高温度および高電力の用途で使用され得る。 (もっと読む)

イオン注入せずに縦型接合形電界効果トランジスタおよびバイポーラ接合トランジスタを製造する方法およびそれによって製造されたデバイス

縦型接合形電界効果トランジスタ(VJFET)またはバイポーラ接合トランジスタ(BJT)のような半導体デバイスを製造する方法が記載される。その方法はイオン注入を必要としない。VJFETデバイスは、エピタキシャル成長した埋め込みゲート層のみでなく、エピタキシャル再成長したn型チャネル層及びエピタキシャル再成長したp型ゲート層も有する。その方法で製造されたデバイスも記載される。 (もっと読む)

半導体装置およびその製造方法

【課題】 炭化珪素の半導体装置において、電極材料と、内部配線の材料とが異なるとき、これら異種金属の接触界面における不具合のおそれを無くして、長期間使用後にも高い信頼性を得ることができる、半導体装置等を提供する。

【解決手段】 炭化珪素14,18に接触する接触電極16と、該接触電極と導通する配線19とを備え、接触電極16が、チタン、アルミニウム、および珪素を含有する合金で形成され、配線19は、アルミニウムまたはアルミニウム合金で形成され、該配線は接触電極と接触することで該接触電極と導通をとることを特徴とする。

(もっと読む)

横型接合型電界効果トランジスタ

【課題】漏れ電流の発生を防止すると共に、十分な耐圧を実現することが可能な横型接合型電界効果トランジスタを提供する。

【解決手段】この発明に従った横型JFET10では、バッファ層11は、SiC基板1の主表面上に位置し、p型不純物を含む。チャネル層12は、バッファ層11上に位置し、バッファ層11におけるp型不純物の濃度より高い濃度のn型不純物を含む。n型のソース領域15およびドレイン領域16は、チャネル層12の表面層において互いに間隔を隔てて形成され、p型のゲート領域17は、チャネル層12の表面層においてソース領域15およびドレイン領域16の間に位置する。バリア領域13は、チャネル層12とバッファ層11との境界領域において、ゲート領域17の下に位置する領域に配置され、バッファ層11におけるp型不純物の濃度より高い濃度のp型不純物を含む。

(もっと読む)

ワイドバンドギャップ半導体パワーJFETのための高温ゲートドライバ及びそれを含む集積回路

高い周囲温度環境において作動することが可能なワイドバンドギャップ(例えば、>2eV)半導体接合形電界効果トランジスタ(JFET)のためのゲートドライバについて記載される。ワイドバンドギャップ(WBG)半導体デバイスは、炭化ケイ素(SiC)及び窒化ガリウム(GaN)を含む。ドライバは、入力、出力、第1供給電圧を受け取るための第1基準線、第2供給電圧を受け取るための第2基準線、グランド端子、6つの接合形電界効果トランジスタ(JFET)を有する非反転ゲートドライバであり得、第1JFETおよび第2JFETは、第1反転バッファを形成し、第3JFETおよび第4JFETは、第2反転バッファを形成し、及び第5JFET及び第6JFETは、高温パワーSiC JFETを駆動させるために使用され得るトーテムポールを形成する。反転ゲートドライバも記載される。 (もっと読む)

p型半導体デバイス

半導体デバイスが、第1の閉じ込め層(32)上に活性層(31)を備える。活性層(31)は厚さ20nm未満のα−Sn層を備える。第1の閉じ込め層(32)は、α−Snより広いバンドギャップの材料から形成され、α−Snとこの材料間のバンドギャップオフセットは活性層への電荷キャリアの閉じ込めを可能にし、活性層は量子井戸として作用する。類似の第2の閉じ込め層(34)が活性層(31)上に形成されてもよい。半導体デバイスはp−FETであってもよい。このような半導体デバイスの製造方法もまた説明されている。  (もっと読む)

(もっと読む)

テラヘルツ受信素子

【課題】さまざまな偏光特性を持つ電磁波、光波の存在下においても、テラヘルツ信号を正確に受信するテラヘルツ受信素子を提供する。

【解決手段】本発明のテラヘルツ受信素子は、2つの電界効果型トランジスタFET−A、FET−Bと、アンテナとしての2本のゲートワイヤ12、12’と、差分回路21とを有し、前記2本のゲートワイヤ12、12’のそれぞれは、対応する電界効果型トランジスタに電気的に接続され、2つの電界効果型トランジスタへの2つのゲートワイヤ12、12’の取り付け方向のなす角度は0°以外の一定の角度であり、差分回路21は、2つの電界効果型トランジスタのドレイン部から出力される2つの信号の差分を算出し、受信信号として出力する。

(もっと読む)

量子井戸デバイスにおける平行伝導を改善する装置及び方法

平行伝導を改善する量子井戸デバイスを提供する方法及び装置の実施形態が主に記載される。その他の実施形態についても、記載及び特許請求される。 (もっと読む)

半導体装置

【課題】還流ダイオードの逆回復動作時に生じる振動現象の収束時間を低減することが可能な半導体装置を提供する。

【解決手段】 ユニポーラ動作をする還流ダイオード100と、還流ダイオード100に並列接続され、半導体基板領域を含む半導体スナバ200とを備える。半導体スナバ200は、還流ダイオード100の逆バイアス時に少なくとも前記基板領域の一端側に形成されるキャパシタ210と、基板領域の一部を含む抵抗220と、還流ダイオード100の順バイアスに対して逆阻止状態となるように、基板領域の少なくとも一部に形成された逆阻止型ダイオード222とを含む。

(もっと読む)

半導体装置、電力変換装置及び半導体装置の製造方法

【課題】RCスナバ回路の抵抗Rの値を任意に設計可能な半導体スナバ回路を用いた半導体装置、電力変換装置、半導体装置の製造方法を提供する。

【解決手段】ユニポーラ動作をする還流ダイオード100と、還流ダイオード100に並列接続され、キャパシタ210及び抵抗220をモノリシックに集積化した半導体スナバ回路200とを備える半導体装置において、抵抗220が、半導体スナバ回路200の基材となる半導体基体の一部に形成され、半導体基体の比抵抗よりも高い比抵抗を有する高抵抗層を含む。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に接続されたユニポーラ型の還流ダイオード150と、還流ダイオード100に並列接続され、少なくともキャパシタ210と抵抗220とを有する半導体スナバ200、及び、還流ダイオード150に並列接続され、少なくともキャパシタ260と抵抗270とを有する半導体スナバ250が形成された基板領域11を有する半導体チップ1000とを備えている。

(もっと読む)

半導体装置

【課題】並列接続された還流ダイオードと半導体スナバ回路が隣接して配置されるので、小型化され且つ逆バイアス時に還流ダイオードに発生する振動現象の収束時間を短縮できる半導体装置を提供する。

【解決手段】ユニポーラ動作する還流ダイオード100と、少なくともキャパシタ210及び抵抗220を有し、還流ダイオード100と並列接続されて還流ダイオード100に隣接して配置された半導体スナバ回路200とを備える。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に並列接続され、かつ、キャパシタ210および抵抗220を有する半導体スナバ200とを備えている。半導体スナバ200と還流ダイオード100とが積層されている。

(もっと読む)

半導体装置及び電力変換装置

【課題】還流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮する。

【解決手段】半導体装置は、還流ダイオードDと、還流ダイオードDに対し並列に接続され、且つ、キャパシタと抵抗を有する半導体スナバ回路200と、から構成され、半導体スナバ回路中200のキャパシタが、還流ダイオードDの遮断状態において、還流ダイオードDにより空乏層が形成される前記半導体基体中の領域とは異なる位置に形成されるので、還流ダイオードDの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮することができる。

(もっと読む)

41 - 60 / 168

[ Back to top ]