Fターム[5F102GL02]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | 単一半導体層 (2,547) | 4族 (280)

Fターム[5F102GL02]の下位に属するFターム

Si (112)

Fターム[5F102GL02]に分類される特許

21 - 40 / 168

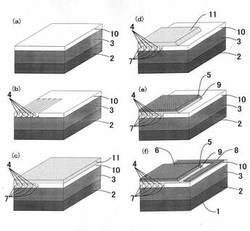

炭化珪素トランジスタ装置の製造方法

【課題】微細化と、オン特性を改善する、炭化珪素トランジスタ装置の製造方法の提供。

【解決手段】高濃度n型炭化珪素基板2上に、低濃度n型ドリフト層3と高濃度p型層10をエピタキシャル成長する工程と、高濃度p型層10の一部を除去離間した複数の高濃度p型ゲート領域4を形成する工程と、互いに隣り合った高濃度p型ゲート領域4の間に位置するチャネル領域7、高濃度p型ゲート領域4及びゲート電極領域10の全面を覆う低濃度n型ドリフト層3よりも低い不純物濃度の低濃度n型領域11をエピタキシャル成長する工程と、低濃度n型領域11の一部を除去する工程と、低濃度n型領域11の表面にイオン注入し高濃度n型ソース領域5を形成する工程と、高濃度n型ソース領域5上にソース電極6を、高濃度n型炭化珪素基板2の裏面にドレイン電極1を、ゲート電極領域10にゲート電極8を形成する工程を含む炭化珪素トランジスタ装置の製造方法。

(もっと読む)

半導体装置

【課題】 立ち上がり電圧低減と高耐圧実現の両立を可能とする構造を提案する。

【解決手段】 SiC縦型ダイオードにおいて、カソード電極21と、n++カソード層10と、n++カソード層上のn−ドリフト層11と、一対のp+領域12と、n−ドリフト層11とp+領域12の間に形成され、且つ一対のp+領域12に挟まれたn+チャネル領域16と、n++アノード領域14と、n++アノード領域14とp+領域12に形成されたアノード電極22を備える。

(もっと読む)

電界効果トランジスタ

【課題】スイッチング速度を向上でき、動作不良品を低減できる、横型の電界効果トランジスタを提供する。

【解決手段】ゲート配線43は、基部44と、基部44から突出する複数の指状部45と、隣接する指状部45の先端部46を接続する接続部47と、を有する。ゲート配線43の指状部45は、ソース配線23の指状部25とドレイン配線33の指状部35と、の間に配置されている。ゲート配線43の基部44は、ソース配線23の基部24とドレイン配線33の指状部35との間に配置され、かつ、ソース配線23の指状部25との間に絶縁膜を介在させて指状部25と交差している。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法、および半導体装置の動作方法

【課題】電界集中を緩和し、高い耐圧を得ることが可能な半導体装置を提供する。

【解決手段】

半導体層上において、第1フィールドプレートFAは、第1絶縁膜上に、第1電極102と第2電極103との間に相互に間隔を置いて配置され、第2フィールドプレートFBは、第2絶縁膜上に、第1電極102上方から第2電極103上方までの間に相互に間隔を置いて配置され、

第1電極および第2電極側末端のFBは、第1電極または第2電極およびそれに隣り合うFAに重なり、

前記第1電極および第2電極側末端FB以外の一方のFAまたはFBは、第1電極から第2電極への方向と垂直方向に隣り合う複数の他方のFAまたはFBに重なり合い、前記第1電極および第2電極側末端FB以外の他方のFAまたはFBは、第1電極から第2電極への方向に隣り合う2つの前記一方のFAまたはFBに重なり合う半導体装置。

(もっと読む)

電子回路装置

【課題】ノーマリオフ型の炭化珪素接合FETはゲートの特性が、使い勝手が悪いという問題がある。これは、ノーマリオフを実現するためにゲート電圧が0Vでオフしていなければならず、かつ、ゲート・ソース間のpn接合に電流が流れないようにオン状態としてはゲート電圧を2.5V程度に抑える必要があるため、実質的にゲート電圧を0Vから2.5Vの間で制御しなければならないためである。従って、閾値電圧からオン状態のゲート電圧までが1Vから2V程度しかなく、ドレイン電流がゲート電圧の変化に非常に敏感であるため、ゲートの制御が難しい。

【解決手段】本願発明は、ノーマリオフ型の炭化珪素接合FETのゲートに、接合FETのゲート容量と同等か少し小さな容量を持つ素子を接続したものである。

(もっと読む)

半導体装置

【課題】 本発明の目的は、半導体装置単体で負電源を必要とせずにスイッチングが可能な素子を提供することである。

【解決手段】 この発明の半導体装置は、ノーマリオンFETと、一方の電極を前記FETのゲートに、他方の電極を入力端子に電気的に接続されたキャパシタと、アノード電極が前記FETのゲートに、カソード電極が前記FETのソースに電気的に接続されたダイオードと、を前記FETと同一チップ上に形成したことを特徴としており、さらに、前記キャパシタが、前記FETのゲート引き出し電極上に誘電体などの絶縁膜を形成し、形成した前記絶縁膜に金属膜を形成することにより形成されたことが好ましい。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】イオン注入したダイヤモンドの高温高圧アニールにより起こるダイヤモンド表面のエッチングを防ぎ、従来の方法では得られない高品質P型、N型ダイヤモンド半導体を得るダイヤモンド半導体の作製方法を提供すること。

【解決手段】ダイヤモンド基板5−11を用意し、そのダイヤモンド基板5−11上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとして基板温度700℃でダイヤモンド薄膜5−12を1μm積層する。上記ダイヤモンド薄膜5−12にイオン注入装置を用い、加速電圧60kV、ドーズ量1×1014cm−2でドーパントを打ち込む。その後、イオン注入ダイヤモンド薄膜5−13上に保護層(白金)5−14を形成する。表面に保護層5−14が形成されたイオン注入ダイヤモンド薄膜5−13を、超高温高圧焼成炉内に配置し、3.5GPa以上、600℃以上の圧力、温度下でアニールする。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】ダイヤモンド薄膜内に存在する結晶欠陥、不純物等を減少させ、高品質なダイヤモンド薄膜を作製可能なダイヤモンド薄膜作製方法を提供すること。

【解決手段】ダイヤモンドが安定な高圧力下でアニールを行う。これにより、結晶中に含まれる格子欠陥等が回復、除去され、ダイヤモンド結晶薄膜を高品質化する事ができる。「(ダイヤモンドが)安定な、安定に」とは、ダイヤモンドがグラファイト化せずにダイヤモンドの状態を保つ状態を指す。ダイヤモンドが安定にアニール出来る領域内でアニールを行う温度(アニール温度、とも呼ぶ)Tおよびアニールを行う圧力(アニール圧力、とも呼ぶ)Pが決定される。この領域は、図21に示される、P>0.71+0.0027TまたはP=0.71+0.0027Tを満たし、なおかつP≧1.5GPaの領域である。このような領域は、図21中の斜線部分である。

(もっと読む)

半導体装置およびその製造方法

【課題】炭化珪素基板を用いた接合型FETにおいて、ゲート・ソース間のpn接合領域において生じるリーク電流を低減する。

【解決手段】炭化珪素基板を用いたトレンチ型接合FETにおいて、トレンチ5の側壁および底面に窒素を導入することにより、トレンチ5の表面にn型層8およびn+型層9を形成する。これによりp+型ゲート領域4とn+型ソース領域3との接合領域であるpn接合領域はダメージの多いトレンチ5の側壁ではなく半導体基板21の主面において露出し、また、その露出する領域は狭まるため、pn接合領域におけるリーク電流を低減することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】n-型チャネル層2の表面に直接p+型ゲート領域4を形成し、p+型ゲート領域4のうちn-型チャネル層2と接する部分と比較して、n-型チャネル層2から離れた部分が幅広となるようにする。そして、p+型ゲート領域4のうち幅広とされた部分がn-型チャネル層2から所定距離離れるようにする。例えば、n-型チャネル層2に凹部2aを形成し、この凹部2a内にp+型ゲート領域4を形成する。

(もっと読む)

コンプリメンタリー接合電界効果トランジスタを備えた炭化珪素半導体装置およびその製造方法

【課題】平坦面に対してデバイス形成できる絶縁分離構造を有し、かつ、高周波でのノイズ伝播や高温時でのリーク電流の発生を抑制できるCJFETを備えたSiC半導体装置を提供する。

【解決手段】絶縁分離層3にてn-型SiC層2やp-型SiC層4を絶縁分離する。これにより、平坦面に対してデバイス形成を行うことができる。このため、製造工程の簡略化を図ることが可能となる。また、PN分離ではなく、半絶縁性のイントリンシック層にて構成された絶縁分離層3によって絶縁分離構造を構成しているため、絶縁分離層3によって高周波ノイズを吸収することによる高周波でのノイズ伝播の抑制を行えると共に、高温時でのリーク電流の発生の抑制を行うことが可能となる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

接合型電界効果トランジスタ

【課題】耐圧性に優れかつチャネル領域の不純物濃度やその厚さ等のばらつきの影響を受けにくいJFETを提供する。

【解決手段】SiC基板9の一方面上にはアルミニウム膜7が形成されている。そのアルミニウム膜7に接するように、そのアルミニウム膜7の両側に、SiC膜からなるチャネル領域4a、4bが設けられている。チャネル領域4a、4b上にはソース領域5a、5bを介してソース電極11a、11bが形成されている。チャネル領域4a、4bのアルミニウム膜7側と反対側にp型SiC膜2a、2bを介してゲート電極13が形成されている。SiC基板9の他方面上には、ドレイン領域6が形成されている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ると共に、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】p+型ゲート領域2をSiC基板1の内部に埋め込んだ構造とする。これにより、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ることが可能となる。また、p+型ゲート領域2がn-型チャネル層3に直接接触させられる構造であるため、p+型ゲート領域2から広がる空乏層によって容易にn-型チャネル層3をピンチオフさせることができ、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制できる。

(もっと読む)

半導体装置およびその製造方法

【課題】DモードとEモードの素子を組み合わせた半導体装置およびその製造方法を提供する。

【解決手段】DモードとEモードのJFETにおけるチャネル領域を設定する場所にそれぞれ凹部2aと凸部2bを備えることで、同一基板上に厚みが異なるn型チャネル層3を形成する。そして、このような厚みが異なるn型チャネル層3によってDモードとEモードで作動するJFETを同一基板上に備えることができるため、SiCでもDモードとEモードのJFETを組み合わせたSiC半導体装置を実現することが可能となる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】エピタキシャル成長を行わなくても素子形成が行え、かつ、バンチングが発生することを防止できるようにする。

【解決手段】エピタキシャル成長を行わず、素子を構成する各領域をイオン注入のみによって形成すると共に、SiC基板1としてオフ角を有しないオン基板を用いる。これにより、イオン注入領域を活性化するための熱処理によってバンチングが発生しないようにできる。したがって、エピタキシャル成長を行わなくても素子形成が行え、かつ、バンチングが発生することを防止できるSiC半導体装置とすることができる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部の周辺を含めてn+型SiC基板1の外縁部においてn+型ソース領域4が除去されると共に、トレンチ6の先端部においてn-型チャネル層7および第2ゲート領域8が除去された凹形状とする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】高耐圧および高電流のスイッチング動作が可能で、かつ製造が容易なFETを提供する。

【解決手段】半導体薄体の一の主表面に設けられた、第1導電型のソース領域(1)と、第1導電型のチャネル領域(10)と、チャネル領域を限定する第2導電型の限定領域(5)と、他の主表面に設けられた第1導電型のドレイン領域(3)と、厚さ方向に連続する第1導電型のドリフト領域(4)とを備え、ドリフト領域(4)およびチャネル領域(10)の不純物濃度は、ソース領域(1)、ドレイン領域(3)および限定領域(5)の不純物濃度よりも低く、チャネル領域(10)の不純物濃度はドリフト領域(4)の不純物濃度よりも低い。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層の厚みのバラツキを抑制できるJFET、MOSFETもしくはMESFETを備えた半導体装置およびその製造方法を提供する。

【解決手段】n+型層3に対して異方性エッチングを行うことによって凹部4を形成したのち、この凹部4内にエピタキシャル成長させることによってn型チャネル層5を形成する。これにより、n型チャネル層5を一定の膜厚かつ一定の濃度で形成することが可能となる。このため、従来の構造と異なり、n型チャネル層5の膜厚が一定なバラツキのない構造とすることが可能となる。したがって、JFETの特性も一定とすることが可能となる。

(もっと読む)

21 - 40 / 168

[ Back to top ]