Fターム[5F102GL02]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | 単一半導体層 (2,547) | 4族 (280)

Fターム[5F102GL02]の下位に属するFターム

Si (112)

Fターム[5F102GL02]に分類される特許

141 - 160 / 168

半導体装置およびその製造方法、容量素子およびその製造方法、並びにMIS型半導体装置およびその製造方法。

【課題】 高耐圧で信頼性の高い半導体装置およびその製造方法、容量素子およびその製造方法、並びにMIS型半導体装置およびその製造方法を提供すること。

【解決手段】 プラズマCVD装置を用い、モノシランガス、水素ガスおよび窒素ガスからなる混合ガスを用い、前記水素ガスの全流量に対する流量比が0.2%から5%の条件で形成された窒化珪素膜をキャパシタ膜、パッシベーション膜、ゲート絶縁膜またはマスク膜に用いた半導体装置およびその製造方法、容量素子およびその製造方法、並びにMIS型半導体装置およびその製造方法。

(もっと読む)

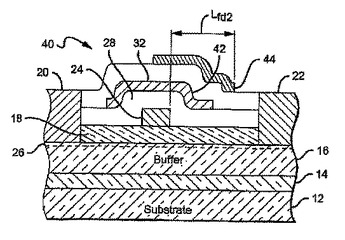

改善されたフィールドプレートを備える半導体デバイス

電界効果トランジスタデバイス及び電界効果トランジスタを形成するための方法であって、当該デバイスは、半導体とオーム接触しているソース電極及びドレイン電極とを備える、電界効果トランジスタデバイス及び電界効果トランジスタを形成するための方法。ゲート電極−フィールドプレート構造は、ソース電極とドレイン電極との間に配置される。ゲート電極−フィールドプレート構造は、誘電体と、半導体とショットキー接触している第1の金属と、第2の金属とを有する。第2の金属は、第1の金属の一部の上に配置されると共に電気的に接続される第1の部分と、誘電体の一部によって第1の金属の第2の部分から分離され、且つ第1の金属のエッジを越えて、第2の金属のエッジまで延在する第2の部分とを有する。電界効果トランジスタデバイスのためのフィールドプレートを設けるために、第1の金属のエッジは、第2の金属のエッジよりもドレイン電極から離れている。 (もっと読む)

半導体装置およびその製造方法並びにその半導体装置製造用基板およびその製造方法。

【課題】 高ドレイン電圧を印加したときに生じるコラプス現象を抑制し、高出力動作可能な半導体装置およびその製造方法並びにその半導体装置製造用基板およびその製造方法を提供する。

【解決手段】 基板(11)上に形成されたGaN系半導体層(13)と、GaN系半導体層(13)の表面に形成された、珪素またはアルミニウムが化学量論的な組成比より多い窒化珪素、酸化珪素、酸化窒化珪素、窒化アルミニウムまたは酸化アルミニウムからなる絶縁膜(25)と、GaN系半導体層(13)上に形成されたゲート電極(18)と、ゲート電極(18)を挟んで形成されたソース電極(14)およびドレイン電極(16)と、を具備する半導体装置およびその製造方法並びにその半導体装置製造用基板およびその製造方法である。

(もっと読む)

接合型半導体装置の製造方法

【課題】 自動車のモータ制御用などで求められるノーマリオフ特性を有する高性能の接合型デバイスを容易な製造工程で実現できるデバイス構造の接合型半導体装置および接合型半導体装置の製造方法を提供する。

【解決手段】 第1の高抵抗層形成工程と、チャネルドープ層形成工程と、第2の高抵抗層形成工程と、ソース領域12となる第1導電型の低抵抗層を形成する低抵抗層形成工程と、低抵抗層と第2の高抵抗層の途中の深さまで部分的にエッチングするエッチング工程と、エッチング工程でエッチングした部分の下部にゲート領域13を形成するゲート領域形成工程と、表面保護膜17を形成する表面保護膜形成工程と、ソース電極19とゲート電極20とドレイン電極18を形成する電極形成工程と、ソース電極19とゲート電極20側に上層電極21を形成する上層電極形成工程と、を有する。

(もっと読む)

ゲート−ソースフィールドプレートを含むワイドバンドギャップトランジスタ

本発明に係るトランジスタは、チャネル層を有する活性領域を含み、この活性領域と接触してソースおよびドレイン電極が形成され、このソース電極とドレイン電極との間にあって活性領域と接触したゲートが形成される。ゲートとドレイン電極との間およびゲートとソース電極との間の複数の活性領域の表面の少なくとも一部分上にスペーサ層がある。このスペーサ層上にはフィールドプレートがあり、活性領域の上のスペーサ上をドレイン電極に向かって延びる。このフィールドプレートはさらに、活性領域の上のスペーサ層上をソース電極に向かって延びる。少なくとも1つの導電性経路が、フィールドプレートをソース電極またはゲートに電気的に接続する。  (もっと読む)

(もっと読む)

炭化珪素トランジスタ装置及びその製造方法

【課題】 炭化珪素トランジスタ装置の、微細化によるデバイス特性改善を阻む要因を除去する。

【解決手段】 高濃度n型炭化珪素基板(2)表面上にエピタキシャル成長により低濃度n型ドリフト層(3)、更に、互いに離間した複数の高濃度p型ゲート領域(4)を形成し、該構造上に低濃度n型チャネル領域(7)と低濃度n型領域1(9)をエピタキシャル成長させ、イオン注入により高濃度n型ソース領域(5)を形成し、前記高濃度n型ソース領域(5)上へソース電極(6)、ドライエッチングによりデバイスセル外に露出した高濃度p型層(10)上へゲート電極(8)、高濃度n型炭化珪素基板(2)の裏面にドレイン電極(1)を形成する。

(もっと読む)

高性能FETデバイス及び方法

【課題】半導体FETデバイスの機能及び高周波性能を改善するために用いることができる、ゲート電圧バイアス供給回路素子を備えたエピタキシャル積層構造を提供する。

【解決手段】半導体電界効果トランジスタ(FET)デバイスの性能を改善するためのゲート電圧バイアス供給回路素子を備えたエピタキシャル積層構造は、基板と、該基板上にエピタキシャルに成長したn型またはp型の第1の層の半導体膜であって、基板と第1の層膜との間にバッファ層が存在する可能性がある第1の層の半導体膜と、第1の半導体層上にエピタキシャルに成長した活性半導体層であって、活性層の導電型が第1の半導体層の導電型と反対であり、またFETを形成するのに十分なゲート、ドレイン、ソースへの電気コンタクトを備えたゲート領域及びドレイン領域及びソース領域を有する活性半導体層と、基板または第1の半導体層上の電気コンタクトと、デバイス性能を向上させるのに十分な電圧極性及び大きさで、ゲートコンタクト及び基板または第1の半導体層に電気的に接続されたゲート電圧バイアス供給回路素子と、からなる構造を利用する。  (もっと読む)

(もっと読む)

シリコンカーバイド静電誘導トランジスタ

【課題】 ドリフト層(電圧保持層)10を共通化して逆並列ダイオードを内蔵したシリコンカーバイド静電誘導トランジスタ(SiC−SIT)を実現する。

【解決手段】 ソース領域11の第1側面の溝19の底面から側面に沿ってゲート領域12を形成し、第1側面(片側)からの空乏層の伸縮のみでチャネル17の幅を制御し、トランジスタ電流Itをオン/オフ制御するスイッチング素子を構成する。一方、第2側面の溝20の底面から側面に沿いソース領域11の表面に亘ってソース電極18を形成し、このソース電極18とドリフト層10との間にショットキー接合21を形成し、このショットキー接合21からドレイン領域15へ、ドリフト層10を共通化して電流Idを流すダイオードを形成する。

(もっと読む)

高い熱放散を伴う複合構造

【課題】良好な熱放散を伴う複合構造を提供する。

【解決手段】光学、光電子工学、または電子工学での用途のための複合構造40であって、支持ウェハ20と、単結晶材料の中から選択される材料からなる層と、誘電体材料からなる層13とを備え、複合構造40の熱インピーダンスが、周囲温度と600°Kとの間で、複合構造と同じ寸法を有する単結晶バルクSiCウェハの熱インピーダンスの約1.3倍以下になるように、支持ウェハ20、単結晶材料からなる層11、および誘電層13が作成される材料が選択され、各層の厚さが調整されることを特徴とする複合構造40。また、この複合構造40を製造するための方法。

(もっと読む)

双方向型電界効果トランジスタおよびマトリクスコンバータ

【課題】単一のデバイスで双方向に流れる電流を制御できる双方向型電界効果トランジスタおよびこれを用いたマトリクスコンバータを提供する。

【解決手段】双方向型電界効果トランジスタは、半導体基板1と、半導体基板1上に設けられ、該基板1の主面に平行なチャネルと該チャネルのコンダクタンスを制御するためのゲート電極13aとを含むゲート領域と、チャネルの第1端側に設けられた第1領域と、チャネルの第2端側に設けられた第2領域とを備え、第1領域の第1電極11aからチャネルを介して第2領域の第2電極12aへ流れる順方向電流および第2電極12aからチャネルを介して第1電極11aへ流れる逆方向電流が、ゲート電極13aに印加されるゲート電圧によって制御される。

(もっと読む)

半導体装置及びその製造方法

【課題】低オン抵抗のスイッチ素子を低コストで実現する。

【解決手段】第一導電型の半導体基体であるN+型SiC基板2及びN−型ドレイン領域1と、N+型SiC基板2の第一主面側に、電流のオン、オフを切り替えるスイッチ機構とを有する半導体装置において、N−型ドレイン領域1中に、該N−型ドレイン領域1とはバンドギャップの異なるP+型ポリシリコンで形成され、第一主面と、該第一主面と対向する第二主面との間で伸びる柱状のヘテロ半導体領域4が、間隔を置いて並んで複数形成されている。

(もっと読む)

半導体装置

【課題】基板強度を保持しつつオン抵抗を低減し得る半導体装置を提供する。

【解決手段】網目状の凸部により形成された複数の凹部を裏面に有し、第1の不純物濃度を有する半導体からなる支持体21と、前記支持体の前記裏面に対向する表面に形成され、前記第1の不純物濃度よりも低い第2の不純物濃度を有する半導体層3と、前記半導体層3に形成された半導体素子とを具備することを特徴とする。

(もっと読む)

ダイヤモンド半導体素子及びその製造方法

【課題】 トランジスタ特性が優れ、また高効率で紫外線発光が可能なダイヤモンド半導体素子及びその製造方法を提供する。

【解決手段】 ダイヤモンド基板1上に、高濃度にBがドープされ夫々ソース及びドレインとなる高ドープダイヤモンド層2及び3を局所的に形成する。また、高ドープダイヤモンド層2と高ドープダイヤモンド層3との間には、極低濃度にBがドープされチャネル層となる低ドープダイヤモンド層4、Bがドープされゲートとなるドープダイヤモンド層6、及び極低濃度にBがドープされチャネル層となる低ドープダイヤモンド層5をこの順に形成する。更に、高ドープダイヤモンド層2上にソース電極となる金属電極7、高ドープダイヤモンド層3上にドレン電極となる金属電極8、ドープダイヤモンド層6上に、ゲート電極となる金属電極9を形成し、ダイヤモンドトランジスタ10にする。

(もっと読む)

炭化珪素半導体装置

【課題】 炭化珪素を用いた静電誘導トランジスタにおいて、シート抵抗が小さいゲート領域を形成し、ゲート遅延を短縮し、高速スイッチング動作を実現する。

【解決手段】 トレンチ溝110〜114に沿ってゲート領域12を形成したSITの溝底のゲート引出し層13からCVD法により形成されるタングステンプラグ膜を利用して、溝上部までタングステンプラグ膜(ゲート立上げ金属膜)31で持ち上げ、トレンチ溝短冊の長辺を、ゲート遅延が問題にならない程度に短くし、溝上部でタングステンプラグ膜同士を接続した。

(もっと読む)

BiCMOSと互換性を有するJFET装置及びその製造方法

エミッタ・アウト拡散、又は縦型バイポーラ装置を形成するために用いられるのと同じ工程で形成されるソース領域及びドレイン領域(17、18)を備えたBiCMOSと互換性があるJFET装置であって、バイポーラ装置内にエミッタ・キャップを形成する半導体層がJFET装置のチャネル(16)を形成し、バイポーラ装置の真性ベース領域を形成する材料層(すなわちベース・エピ・スタック)がJFET装置の真性ゲート領域(14)を形成するJFET装置。その結果、如何なる更なるマスキング又は他の処理ステップの必要なしに、JFET装置の標準的なBiCMOSプロセスへの組み込みが達成される。  (もっと読む)

(もっと読む)

半導体素子及びその製造方法

【課題】 チャネル領域内のキャリア制御性が優れると共にリーク電流が少ない半導体素子及びその製造方法を提供する。

【解決手段】 基板1上に、エピタキシャル成長により、基板1の表面に対して垂直な方向を含む断面が下底よりも上底が短い台形形状である低濃度ドープダイヤモンド層4を形成する。次に、低濃度ドープダイヤモンド層4の両側に、エピタキシャル成長により低濃度ドープダイヤモンド層4よりも不純物濃度が高い高濃度ドープダイヤモンド層7a及び7bを形成する。そして、高濃度ドープダイヤモンド層7a及び7b上に、金属電極8a及び8bを形成した後、酸化シリコン絶縁層9a及び9bを形成し、更に、低濃度ドープダイヤモンド層4の上に酸化アルミニウム絶縁層10を介してゲート電極11を形成して、高濃度ドープダイヤモンド層7a及び7b間の距離が基板1から遠ざかるに従い短くなる半導体素子とする。

(もっと読む)

半導体装置

【課題】 低オン抵抗化を実現し、高速スイッチングが可能なJFETやSITなどの炭化珪素半導体装置を提供する。

【解決手段】 トレンチ溝110〜113に沿って形成したゲート領域13間のチャネルに拡がる空乏層により電流をオンオフするJFETやSITにおいて、半導体基体表面あるいはトレンチ溝113の底部に、外部より電圧が供給可能なゲートコンタクト層102とゲート電極103を設け、これとは独立し、トレンチ溝110〜112の底部で、ゲート領域13のp++コンタクト層14にオーミック接触するメタル導電部(仮想ゲート電極)101を設ける構造とした。この仮想ゲート電極101は、ゲート電極103や外部配線とは絶縁された形となる。

【効果】 ゲート抵抗を小さくし、高速スイッチング動作が可能な大電流容量の炭化珪素半導体装置を得ることができる。

(もっと読む)

半導体装置

【課題】 高温で動作可能な測温ダイオードを内蔵し、高温環境下で用いることができる炭化珪素半導体装置を提供すること。

【解決手段】 静電誘導トランジスタとして、溝部110,111を制御領域12,14に利用する構造を採る場合、制御層間距離によってノーマリオフ型とすることができる。このノーマリオフを素子間分離として用い、炭化珪素と多結晶シリコンとのヘテロ接合ダイオード114(又はpn接合ダイオード)を構成する。

また、深いp型の第3層30を接地することによっても、素子間分離を達成し、この内側のn型第4層と基体他面との間に測温ダイオードを造り込むことができる。

(もっと読む)

半導体装置、およびその半導体装置を用いた電力変換器、駆動用インバータ、汎用インバータ、大電力高周波通信機器

イオン注入で形成されたP型、N型の不純物半導体領域を有する炭化珪素半導体基板を用いた半導体装置において炭化珪素半導体基板表面の凹凸を小さくすることにより、最終的に半導体装置の電気特性を向上できるようにする。この発明の半導体装置は、(000−1)面あるいは(000−1)面からある角度傾いた面を最表層面として有する炭化珪素半導体領域1,2に、P型半導体領域3およびN型半導体領域の少なくとも一方がイオン注入により選択的に形成され、その最表層面に金属電極が形成され、その金属電極に電圧を印加することにより最表層面に垂直な方向に流れる電流の方向を制御するショットキー・バリア・ダイオード、若しくはPN型ダイオードである。  (もっと読む)

(もっと読む)

ソース領域の下にp型埋込み層を備えたトランジスタ及びその作製方法。

本発明は、金属半導体電界効果トランジスタ(MESFET)を提供する。このMESFETは、ソース(13)とドレイン(17)とゲート(24)とを備えている。このゲート(24)を、ソース(13)とドレイン(17)の間及びn導電型チャネル層(18)上に設ける。ドレイン(17)に向かって延びている端部を備えるp導電型領域(14)をソースの下に設ける。このp導電型領域(14)をn導電型チャネル領域(18)から隔ててソース(13)に電気的に結合させる。  (もっと読む)

(もっと読む)

141 - 160 / 168

[ Back to top ]