Fターム[5F102GL02]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | 単一半導体層 (2,547) | 4族 (280)

Fターム[5F102GL02]の下位に属するFターム

Si (112)

Fターム[5F102GL02]に分類される特許

121 - 140 / 168

半導体装置及びその製造方法

【課題】 従来の半導体製造工程を大きく変更することなく、電界効果型トランジスタの実効的なチャネル面積の増大が可能な半導体装置及び半導体装置の製造方法を提供することを課題とする。

【解決手段】 電界効果型トランジスタの素子分離領域、ソース及びドレイン領域、チャネル領域が、半導体基板表面上に設けた複数の溝に沿って構成されていることを特徴とする半導体装置及び平坦な半導体基板の表面に一定間隔一定幅の線状パターン形成する工程、線状パターンをマスクとして半導体基板をエッチングし複数の溝を形成する工程、及び複数の溝に沿ってチャネル領域が構成された電界効果型トランジスタを形成する工程を含む半導体装置の製造方法によって解決される。

(もっと読む)

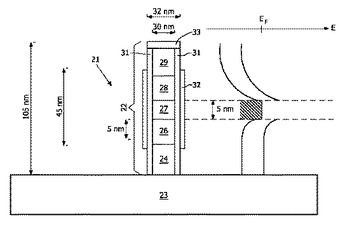

バリアを有するトンネルトランジスタ

本発明は、ソース(24)およびドレイン(29)、並びにこれらのソースとドレインの間に配置されたバリア領域(27)を備えたトランジスタ(21)を提案する。バリア領域は、半導体材料の真性または低濃度ドーピング領域(26,28)によってソースおよびドレインから分離されている。バリア領域と真性または低濃度ドーピング領域との界面にポテンシャルバリアが形成される。ゲート電極(32)はポテンシャルバリアの付近に設けられ、ゲート電極に適切な電圧を印加することによって、ポテンシャルバリアの実効的な高さおよび/または幅を調整することができる。  (もっと読む)

(もっと読む)

電界効果トランジスタを形成するための層状構造

【課題】高性能Geチヤネル構造により、移動度および相互コンダクタンスに優れたHEMT、CMOSデバイスを提供する。

【解決手段】 半導体基板上に複数の半導体層と、より高いバリアまたはより深い閉じ込め量子井戸を有し、相補型MODFETおよびMOSFETのための非常に高い正孔移動度を有する圧縮ひずみエピタキシャルGe層のチャネル構造を取り込み、層状ヘテロ構造をもつ高移動度Geチャネル電界効果トランジスタを形成する。 本発明は、室温より上(425K)から極低温(0.4K)までの広範な温度動作範囲を有し、低温であっても高いデバイス性能が達成可能であることに加えて、ディープ・サブミクロンの現況技術のSi pMOSFETに勝る、移動度および相互コンダクタンスの向上が可能である。

(もっと読む)

低電力接合型電界効果トランジスタの製造方法及び作動方法

小さい線幅を有する一対の相補型接合型電界効果トランジスタ(CJFET)を含むインバータを使用する方法が提供される。この方法は、CJFETインバータの入力キャパシタンスを、同等の線幅のCMOSインバータの対応する入力キャパシタンスより小さくさせることを含んでいる。CJFETは、順バイアスされたダイオードの電圧降下より低い値を有する電源電圧で動作し、CMOSインバータと比較して低減されたスイッチング電力を有する。CJFETインバータの伝搬遅延は、CMOSインバータの対応する遅延に対して少なくとも同等である。  (もっと読む)

(もっと読む)

炭化珪素系半導体素子および発光素子

【課題】バンドギャップを小さくすると共に電子散乱が抑制され、炭化珪素を用いたチャネル領域でのキャリア移動度を向上させた半導体素子、並びにレーザを発振する発光素子を提供する。

【解決手段】SiC基板11上に、AlドープされたSi0.9M0.1C混晶(Mは、Ge,Sn,Pbの少なくとも一種)よりなる薄膜または細線のAlドープSiMC層14が設けられている。また、SiC基板11の内部に、AlドープされたSi0.9M0.1C混晶(Mは、Ge,Sn,Pbの少なくとも一種)よりなる薄膜または細線のAlドープSiMC層14が設け発光させる。

(もっと読む)

半導体装置およびその製造方法

【課題】素子間を分離する絶縁層を容易に形成することができ、また配線の段切れを防止することができ、さらには配線部における寄生容量も低減できる、半導体装置およびその製造方法を提供する。

【解決手段】SiC基板(またはSiC薄膜)に素子間を分離する溝17が形成され、その溝17内が酸化膜(SiO2)18などの絶縁膜で埋め込まれた構造とする。絶縁膜は堆積によって形成すればよいので、1um以上の厚みが容易に得られ、簡便な方法でありながら、良好に素子分離することが可能となる。溝17内を埋め込んだ絶縁膜上に配線することで、断線を防止し、寄生容量を低減することが可能である。

(もっと読む)

半導体装置

【課題】多結晶Si埋め込みゲートSiC接合FETで、高耐圧と低オン抵抗の両立を図る。

【解決手段】n+−SiCをドレイン層とし、n+ドレイン層に接するn-−SiCをドリフト層とする。n-ドリフト層上に形成されたn+−SiCをソース層とし、n+ソース層からn-ドリフト層の所定深さまでトレンチ溝を形成することでn-ドリフト層の一部をチャネル領域とする。こうして、前記トレンチ溝を充填するp型多結晶Siをゲート領域とする接合FETにおいて、少なくとも前記チャネル領域の側壁部分がp型多結晶Siゲート領域と酸化膜を介さずに接する。

(もっと読む)

シリコン及びシリコン合金内の相補型接合型電界効果トランジスタ及びMOSトランジスタを用いた集積回路

シリコン内の接合型電界効果トランジスタを用いて相補型論理回路を構築する方法が開示される。本発明は、理想的に、好ましくは65nm未満のディープサブミクロンの寸法に適したものである。本発明の基礎となるものは、エンハンスメントモードで動作する相補型接合型電界効果トランジスタである。このJFETの速度−パワー性能はサブ70nm寸法のCMOSデバイスに匹敵するものになる。しかしながら、JFETの最大電源電圧は依然として内蔵電位(ダイオードの電圧降下)より小さく制限される。より高い電圧レベルまで駆動される外部回路へのインターフェースを必要とする一定の用途を満足させるため、本発明は、JFETと同一基板上にCMOSデバイスを構築する構造及び方法を含む。 (もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】 高いキャリア移動度を得ると共に大電流化を可能とする。

【解決手段】 チャネル領域において、不純物が実質的にドープされていないSi0.9Ge0.1Cスイッチング層14と、Si0.9Ge0.1Cスイッチング層14の一部に設けられた溝の、スイッチング層表面と略直交する溝内壁に形成されたSiC電子供給層10とが隣接して設けられている。

(もっと読む)

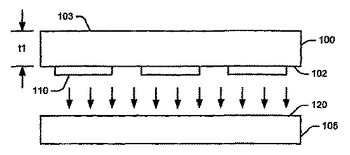

炭化ケイ素パワーデバイスを有する半導体ウェハを処理する方法

炭化ケイ素半導体デバイスを形成するいくつかの方法が開示される。これらの方法は、第1の厚さを有する炭化ケイ素基板の第1の表面に半導体デバイスを形成するステップと、炭化ケイ素基板の第1の表面にキャリア基板を取り付けるステップとを含む。キャリア基板は、炭化ケイ素基板に機械的支持を提供する。これらの方法はさらに、炭化ケイ素基板を、第1の厚さ未満の厚さまで薄くするステップ、炭化ケイ素基板の第1の表面とは反対側の薄くされた炭化ケイ素基板の表面に金属層を形成するステップ、および炭化ケイ素基板の第1の表面とは反対側の薄くされた炭化ケイ素基板の表面にオーミックコンタクトを形成するために、金属層を局所的にアニールするステップを含む。炭化ケイ素基板は、個片化された半導体デバイスを提供するために、個片化される。  (もっと読む)

(もっと読む)

T字型ゲート構造ナイトライド系電界効果トランジスタおよびその製造方法

【課題】優れた高周波特性と高い歩留まりとを有するT字型ゲート構造ナイトライド系電界効果トランジスタおよびその製造方法を提供すること。

【解決手段】基板であるGaN系半導体基板1上に、ナイトライド系半導体層であるAlGaN層2が形成され、AlGaN層2上に表面保護膜であるアニール保護膜4が形成され、アニール保護膜4の一部にAlGaN層2に達する開口部が形成され、該開口部を通してAlGaN層2に接するT字型ゲート電極であるゲート電極6が自己整合的に形成されていることを特徴とするT字型ゲート構造ナイトライド系電界効果トランジスタを構成する。

(もっと読む)

埋込みゲートを有する垂直チャネル接合型電界効果トランジスタおよび製造方法

半導体装置およびその装置の製造方法を説明する。装置は、SiCにおいて実施され、エピタキシャルに成長したn型ドリフト、p型溝ゲート領域、およびp−溝ゲート領域の上にあるn型のエピタキシャルに再成長したチャネル領域を含んでよい。ソース領域は、チャネル領域の上でエピタキシャルに再成長したり、選択的にチャネル領域に注入してよい。その後、ソース、ゲートおよびドレイン領域とのオーム接点が形成されてよい。装置は、ガードリング、接合型ターミネーション・エクステンション(JTE)、またはその他の適当なp−n遮断構造などのエッジターミネーション構造を含んでよい。装置は異なる閾値電圧で加工してよく、同じチャネルドーピングに対して、減少および増加モードの両方の操作を行ってよい。装置は、デジタル、アナログ、およびモノリシックのマイクロ波集積回路で個別電力トランジスタとして使用してよい。  (もっと読む)

(もっと読む)

シリコンカーバイドから製造されるモノリシックな縦型接合型電界効果トランジスタおよびショットキーバリアダイオード、および、その製造方法

自己整合縦型接合型電界効果トランジスタを、エッチング注入ゲートおよび集積逆並列ショットキーバリアダイオードと組み合わせたスイッチング素子が、記載されている。ダイオードのアノードは、漂遊インダクタンスによる損失を低減するために、デバイスレベルでトランジスタのソースに接続される。SBDアノード領域におけるSiC表面は、SBDのターンオン電圧と関連するパワー損失が低減されるよう低いショットキーバリア高さを達成するために、乾式エッチングによって調整される。  (もっと読む)

(もっと読む)

トランジスタ用の非対称レイアウト構造及びその製作方法

高電力トランジスタが提供される。この高電力トランジスタは、ソース領域20とドレイン領域22とゲート接点24を含んでいる。ゲート接点は、ソース領域とドレイン領域の間に配置されている。第1及び第2のオーミック接点がそれぞれ、ソース及びドレイン領域上に設けられている。第1及び第2のオーミック接点はそれぞれ、ソース接点及びドレイン接点を構成する。ソース接点及びドレイン接点は、それぞれに対応する第1及び第2の幅を有する。第1及び第2の幅は異なる。高電力トランジスタの製作方法も提供される。  (もっと読む)

(もっと読む)

静電誘導型トランジスタ、およびその製造方法

【課題】比較的高速な動作が可能で、駆動電圧を比較的低くできる静電誘導型トランジスタを提供することである。

【解決手段】アノード電極9と、半導体層7、71と、この半導体層に埋め込まれたゲート電極5と、カソード電極2とを備えたゲート電極埋め込み静電誘導型トランジスタである。ゲート電極5は、金属膜に貫通孔が形成されてなり、金属膜のアノード側及びカソード側に絶縁層4、101または高抵抗半導体層が配されてチャネルを形成している。ゲート電極5は、ゲート電極となる金属膜を形成する工程、AlとSiを同時にスパッタすることによりAl柱を自己組織的に形成する工程、Al柱およびAl柱直下の金属膜をエッチングする工程を含む工程によって形成され得る。

(もっと読む)

半導体装置、演算増幅器および半導体装置の製造方法

【課題】 ソース/ドレイン接合における接合リーク電流を抑制しつつ、バックゲートバイアスをトランジスタごとに個別に制御する。

【解決手段】 不純物のイオン注入を半導体基板11に局所的に行い、ウェル12a、12bを半導体基板11に形成してから、半導体基板11の表面に絶縁層13を形成し、単結晶半導体層23を介して半導体基板11上の絶縁層13上に半導体基板21を貼り合わせた後、多孔質層22をエッチング除去することにより、多孔質層22を境界として半導体基板21を単結晶半導体層23から剥離する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】 イオン注入に好適なマスク(注入阻止層)の形成工程を含むイオン注入領域形成工程を備えた炭化珪素半導体装置の製造方法を提供する。

【解決手段】 炭化珪素半導体装置の製造方法は、注入阻止層形成工程と、イオン注入工程と、注入阻止層除去工程とを備えている。注入阻止層形成工程では、炭化珪素基板において、イオンが注入される領域を露出させるパターンを有する注入阻止層を形成する。イオン注入工程では、注入阻止層が形成された炭化珪素基板に注入阻止層をマスクとしてイオンを注入する。注入阻止層除去工程では、イオン注入工程においてイオンが注入された炭化珪素基板から注入阻止層を除去する。さらに、注入阻止層形成工程では、珪素原子よりも原子量が大きい元素を構成元素として含み、かつイオンが注入されるときの炭化珪素基板の温度よりも融点が高い材料からなる注入阻止層を形成する。

(もっと読む)

炭化シリコントレンチ装置の端部構造

【課題】ブロッキング特性が効率的で、かつ複雑でないプロセスによって製造することができる炭化シリコントレンチ装置の端部構造を提供する。

【解決手段】炭化シリコン半導体装置に、1つまたは複数のトレンチからなる端部領域を設け、かつこの端部領域に、端部領域と半導体装置の活性領域とを連絡するメサ部を形成する。

(もっと読む)

ダイヤモンドトランジスタ及びその製造方法

トランジスタ、典型的にはMESFETを製造する方法は、ダイヤモンド材料のさらなる層を堆積させることができる成長面を有する単結晶ダイヤモンド材料を含む基板を形成することを含む。基板は、好ましくは、CVDプロセスにより形成され、高純度である。成長面は、3nm以下の二乗平均平方根粗さを有するか、又は3nmを超える段差若しくは突起部を有しない。さらなるダイヤモンド層が、成長面上に堆積され、トランジスタの活性領域を定める。任意選択のn+遮蔽層を基板内又は基板上に形成し、続いて、高純度ダイヤモンドの追加層を堆積する。この方法の一実施形態では、真性ダイヤモンドの層は、高純度層の上面に直接形成され、その後に、ホウ素ドープ(「デルタドープ」)層が続く。デルタドープ層内にトレンチが形成され、これによりゲート領域を定める。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 耐圧が高く、オン抵抗が低い半導体装置およびその製造方法を提供する。

【解決手段】 基板(10)と、該基板上に形成され、SiCドリフト層(14)と、GaN系半導体層(18)と、GaN系半導体層上に形成されたソース電極(60)若しくはエミッタ電極並びにゲート電極(62)と、前記SiCドリフト層の前記GaN系半導体層と相対する面に接続されたドレイン電極(64)またはコレクタ電極と、を具備する半導体装置およびその製造方法である。SiCドリフト層を有することによりドリフト層の厚膜化が可能となりドレイン耐圧が高くできる。さらに、チャネル移動度の高いGaN系半導体層をチャネル層として用いることによりオン抵抗が低い半導体装置およびその製造方法を提供することができる。

(もっと読む)

121 - 140 / 168

[ Back to top ]