Fターム[5F102GL02]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | 単一半導体層 (2,547) | 4族 (280)

Fターム[5F102GL02]の下位に属するFターム

Si (112)

Fターム[5F102GL02]に分類される特許

61 - 80 / 168

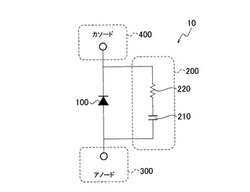

半導体装置及び電力変換装置

【課題】静電容量と抵抗の値が異なる複数のスナバ回路を用意する必要がなく、且つ逆バイアス時に還流ダイオードに発生する振動現象の収束時間を短縮できる半導体装置及び電力変換装置を提供する。

【解決手段】アノード端子300とカソード端子400からなる一対の接続端子と、一対の接続端子間に接続されたユニポーラ動作する還流ダイオード100と、一対の接続端子間に還流ダイオード100と並列接続され、少なくともキャパシタ210と抵抗220を含む半導体スナバ回路200と備え、半導体スナバ回路200のキャパシタ210と抵抗220の値が可変である。

(もっと読む)

半導体装置

【課題】、環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に並列接続され、かつ、キャパシタ210および抵抗220を有する半導体スナバ200とを備えている。半導体スナバ200は、キャパシタ210または抵抗220と接続される第1電極13と、第1電極13と絶縁されつつ、第1電極13と同一主面上に形成されて、キャパシタ210または抵抗220と接続される第2電極14とを有する。

(もっと読む)

半導体装置

【課題】還流ダイオードの逆回復動作時に生じる振動現象の収束時間を低減することが可能な半導体装置を提供する。

【解決手段】 ユニポーラ動作をする還流ダイオード100と、還流ダイオード100に並列接続され、半導体基板領域を含む半導体スナバ200とを備える。半導体スナバ200は、還流ダイオード100の逆バイアス時に少なくとも前記基板領域の一端側に形成されるキャパシタ210と、基板領域の一部を含む抵抗220と、還流ダイオード100の順バイアスに対して逆阻止状態となるように、基板領域の少なくとも一部に形成された逆阻止型ダイオード222とを含む。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に対し並列接続され、基板領域21とキャパシタ210と抵抗220とを含む半導体スナバ200とを備えている。抵抗220の少なくとも一部が、半導体スナバ200の基板領域21の一主面上に直接的にもしくは間接的に形成された、導電性材料からなる膜状の導電層17を含み、かつ、抵抗220に電流が流れる際に、導電層17に流れる電流の経路の少なくとも一部が、膜厚方向以外の方向へ流れる。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮する。

【解決手段】半導体装置1は、還流ダイオードDと、還流ダイオードDに対し並列に接続され、且つ、キャパシタCと抵抗Rを有する半導体スナバ2を備え、環流ダイオードDの遮断状態における静電容量に対するキャパシタCの静電容量の比が0.1以上になっている。このような構成によれば、振動現象の収束効果が高くなるように半導体スナバ2を構成するキャパシタCの静電容量が設定されているので、環流ダイオードDの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】SiCを素材として採用することで本来得られる特性をより確実に得ることが可能な半導体装置およびその製造方法を提供する。

【解決手段】JFET1は、少なくとも上部表面14Aが炭化珪素からなるウェハ10と、上部表面14A上に形成されたゲートコンタクト電極21とを備える。ウェハ10は、上部表面14Aを含むように形成されたイオン注入領域である第1のp型領域16を含む。第1のp型領域16は、上部表面14Aを含むように配置されるベース領域16Aと、突出領域16Bとを含む。ベース領域16Aは、上部表面14Aに沿った方向における幅w1が、突出領域16Bの幅w2よりも広い。ゲートコンタクト電極21は、平面的に見てその全体が第1のp型領域16に重なるように、第1のp型領域16に接触して配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ノーマリオフ型の接合FETにおいて、耐圧の向上とオン抵抗の低減とを両立することができる技術を提供する。

【解決手段】炭化シリコンを基板材料として使用した接合FETにおいて、ゲート領域GRとチャネル形成領域との間のpn接合近傍に、ゲート領域GRに導入されている不純物とは逆導電型であり、チャネル形成領域に導入されている不純物と同じ導電型の不純物を導入する。これにより、pn接合の不純物プロファイルを急峻にするとともに、チャネル形成領域のうち、ゲート領域GRとpn接合を形成する接合領域の不純物濃度が、チャネル形成領域の中央領域の不純物濃度およびエピタキシャル層EPIの不純物濃度よりも高くする。

(もっと読む)

電界効果型トランジスタ

【課題】ドレイン電極からのホールリークが防止された横型のFETを提供することを課題とする。

【解決手段】基板の表面上に形成された第1導電型のチャネル層と、前記チャネル層上に形成されたソース電極、ドレイン電極及びゲート電極とを備え、前記ソース電極及びドレイン電極を前記チャネル層とオーミックコンタクトさせて電界効果型トランジスタを構成し、前記ドレイン電極の下部の前記チャネル層に第1導電型の拡散領域を備え、前記拡散領域が、式(1)Ns≧ε×Vmax/(q×t)(式中、εは前記チャネル層の誘電率[F/m]、Vmaxは前記電界効果型トランジスタの仕様最大電圧[V]、qは電荷量(1.609×10-19)[C]、tは前記基板の表面から前記拡散領域の底面までの距離[m]である)で表されるシート不純物濃度Ns[cm-2]を有していることを特徴とする電界効果型トランジスタにより上記課題を解決する。

(もっと読む)

スロープの側壁を有する垂直接合型電界効果トランジスタ、及びその製造方法

半導体デバイス及びデバイスを製造する方法が記載される。デバイスは、接合型電界効果トランジスタ(JFETs)である。デバイスは、スロープの側壁を有する隆起領域を備え、該側壁は内側にテーパー形状である。側壁は、垂直線から5°以上の角度を形成し、側壁の上部部分は、垂直線から<5°の角度を形成する。デバイスは、垂直(すなわち、0°)又はほぼ垂直の入射イオン注入を用いて、生成される。デバイスは、相対的に均一の側壁ドーピングを有し、角度を有する注入を用いずに、生成される。 (もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ショットキー接触を発生させることなく、炭素の析出を抑制することにより配線の密着性を向上したオーミック電極を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】

SiC半導体装置においてオーミック電極を形成する際に、SiC層11の一方の主表面上には、1種の第1の金属元素からなる、第1の金属層12を形成する。また、第1の金属層の、SiC層11と対向する表面とは反対側の表面上(図1における上側)に、SiからなるSi層13を形成する。このようにして形成した積層構造10Aに対して熱処理を行なう。以上により、電極の表面層への炭素原子の析出や、SiとSiCとによるショットキー接触の形成が抑制された、配線との良好な密着性を示すオーミック電極を有する炭化珪素半導体装置を得ることができる。

(もっと読む)

非シリコンチャネルMOSデバイス中のフェルミレベルピンニングの低減方法

【課題】金属酸化物半導体(MOS)デバイス中の、GeやIII−V化合物(例えばGaAsまたはInGaAs)のような高移動度半導体化合物チャネル中の、フェルミレベルピンニング(FLP)を低減(回避)する方法の提供。

【解決手段】半導体化合物11上のゲート誘電体19上にゲート電極20を形成し、水素アニール21を実施する。水素はゲート電極のPtやPdのような貴金属による触媒作用により原子状水素を形成しアニールを行い半導体化合物11とゲート誘電体19との界面を界面をパッシベートし、更には欠陥を回復する。

(もっと読む)

炭化ケイ素半導体装置および炭化ケイ素半導体装置の製造方法

【課題】チャネルの低い抵抗を維持するとともに、ドリフト層の高い耐圧を維持するSiC半導体装置およびSiC半導体装置の製造方法を提供する。

【解決手段】SiC半導体装置は、SiC基板101、第1半導体層、ベース領域105、第2半導体層、ゲート領域109およびソース領域113を備えている。SiC基板101は、{0001}面に対して30°以上60°以下傾斜した主面101aを有する。第1半導体層は、主面101a上に形成される。ベース領域105は、表面103aの一部に形成される。第2半導体層は、表面103a上に形成される。ゲート領域109は、表面107aの一部に形成され、第2半導体層を挟んでベース領域105と対向する位置に形成される。ソース領域113は、表面107aの一部に形成され、ゲート領域109と隣り合い、かつベース領域105と対向する位置に形成される。

(もっと読む)

接合型電界効果トランジスタの駆動装置および駆動方法

【課題】簡単な構成によって、一時的な過電流による接合型電界効果トランジスタの発熱を抑制するとともに、接合型電界効果トランジスタの過熱状態を検知することができる接合型電界効果トランジスタの駆動装置および駆動方法を提供する。

【解決手段】電流検知部90でモニタする電流が閾値電流を超えた場合、接合型電界効果トランジスタ(JFET)32をターンオンするときのゲート電圧をPN接合のビルトイン電圧より大きくする。これにより、JFET32のオン抵抗を低減させてJFET32の発熱を抑制する。さらに、オン状態のJFET32に流れるゲート電流IGの温度依存性を利用することによって、JFET32の温度の値を簡単に求めることができる。

(もっと読む)

炭化珪素半導体装置

【課題】オーミック電極の接触抵抗を低減するとともに高い耐圧特性を実現することが可能な炭化珪素半導体装置を提供する。

【解決手段】半導体装置1は、基板2と不純物層としてのp+領域25とを備える。基板2は炭化珪素からなり、転位密度が5×103cm−2以下であって、導電型は第1導電型(n型)である。p+領域25は、基板上に形成され、前記第1導電型とは異なる第2導電型の導電性不純物濃度が1×1020cm−3以上5×1021cm−3以下である。

(もっと読む)

ガードリング構造およびその製造方法

半導体素子用のガードリング構造。ガードリング構造は、第1層および第1層の上面に第2層を有する半導体積層体と、第1層内に形成されたゲート構造と、第1層内に形成されたガードリングとを有する。第2層は、第1層のドーパント濃度よりも高いドーパント濃度を有する。ゲートおよびガードリングは、単一のマスクを用いて同時に形成される。  (もっと読む)

(もっと読む)

エッジ終端性能改善のための電場停止層を備えた半導体構造

例示のエッジ終端構造は、半導体素子の周囲に電場停止層を形成することによって、ウエハから切断され実装された後に半導体素子の降伏電圧を維持する。電場停止層は、ドリフト層またはチャネル層のようなエッジ終端構造が提供された層のものより高いドーパント濃度を有する。電場停止層は、素子の周囲に高濃度でドープされた材料を保護し維持するため、素子の製造工程、すなわちメサエッチング中に素子の周囲を選択的にマスキングすることによって形成される。  (もっと読む)

(もっと読む)

半導体装置

【課題】ノーマリオフ特性が実現され、飽和電流値低下が生じず、ゲート電圧に対するドレイン・ソース間電流特性が良好なHEMTを実現する半導体装置を提供する。

【解決手段】第1半導体層131と、第1半導体層131の主面135上に積層され、第1半導体層131の主面135側に2DEG層137を生じさせる第2半導体層133と、第1半導体層131及び第2半導体層133と比して電子親和力χが大きい半導体材料からなり、2DEG層137と電気的に接続された第3半導体層139と、第2半導体層133及び第3半導体層139上に設けられた絶縁膜157と、第3半導体層139にオーミック接続される第1電極151と、第2半導体層133及び第3半導体層139上に絶縁膜157を介して設けられた第2電極153と、第1電極151との間に第2電極153を介在させ、2DEG層137と電気的に接続された第3電極155とを備える。

(もっと読む)

ダイヤモンド電界効果トランジスタ及びその作製方法

【課題】最高動作温度が高くドレイン電流密度が大きい、かつ、長時間の大電力動作にも耐える信頼性のある、実用的なダイヤモンドFETを提供すること。

【解決手段】ダイヤモンド結晶1を用意し、マイクロ波CVD装置のリアクター内で水素プラズマ(Hで表す)を照射し、水素を含む表面層2を形成する(図1(a))。第1の表面層2上の一部の領域に、空間的に分離して、厚さ600nmの金薄膜31、32を蒸着する。これは、各ソース電極31、ドレイン電極32になる。ソース電極31とドレイン電極32との間に、空間的に分離して、Al薄膜4を蒸着する(図1(c))。このAl薄膜4はゲート電極4になる。試料にNO2を供給し、第1の表面層2上に第2の表面層5を形成する(図1(d))。露出した第2の表面層5全体を覆うように保護層6を第2の表面層5上に堆積させる(図1(e))。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】p型コンタクト抵抗を低減でき、素子のスイッチングスピードを下げないようにすることができる炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】半導体基板6のうち第1〜第3コンタクトホール12〜14から露出した部位に、炭化珪素とAlとNiとが反応してそれぞれ形成された合金層15が設けられている。この合金層15におけるAlとNiとの元素組成比は1:4.6〜1:10.6であり、合金層15の厚さは20nm以上100nm以下になっている。これにより、合金層15と半導体基板6とがオーミック接触となり、低いコンタクト抵抗率を得ることが可能となる。

(もっと読む)

ヘテロ接合電界効果トランジスタ

【課題】ゲート電極破壊が起こらず、高電圧で安定して動作し、かつリーク電流を低減することができるヘテロ接合電界効果トランジスタを提供すること。

【解決手段】基板1の表面上にチャネル層2および障壁層3がこの順で積層された半導体層Sと、半導体層S上のトランジスタ領域11に形成されたトランジスタ部11Aおよびホール抜き領域12に形成されたホール抜き部12Aと、トランジスタ領域11とホール抜き領域12との間の半導体層Sの一部を選択除去して設けられた絶縁部10とを備え、ホール抜き部12Aにおけるホール抜き電極8と第2ドレイン電極9の間でアバランシェ降伏が生じるように、ホール抜き電極8と第2ドレイン電極9の間の耐圧が、トランジスタ部11Aのゲート電極と第1ドレイン電極との間の耐圧よりも小さく設定されたことを特徴とするヘテロ接合電界効果トランジスタ。

(もっと読む)

61 - 80 / 168

[ Back to top ]