Fターム[5F102GL08]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | 多層構造(起格子を含む) (113)

Fターム[5F102GL08]に分類される特許

1 - 20 / 113

化合物半導体装置及びその製造方法

半導体装置

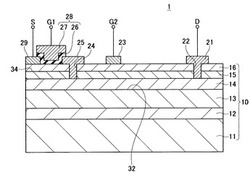

【課題】ノーマリオフで動作するとともに、高い耐圧と低いオン抵抗を具備した半導体装置を提供すること。

【解決手段】 半導体装置1では、ドレイン電極21が第1ヘテロ接合面32に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ソース電極29が第1ヘテロ接合面32に形成される2次元電子ガス層から電気的に絶縁可能に構成されているとともに第2ヘテロ接合面34に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ゲート部28が第2ヘテロ接合面34に対向しており、導通電極25が第1ヘテロ接合面32及び第2ヘテロ接合面34に形成される2次元電子ガス層の双方に対して電気的に接続可能に構成されている。第1ヘテロ接合面32に形成される2次元電子ガス層の電子濃度は、第2ヘテロ接合面34に形成される2次元電子ガス層の電子濃度よりも濃い。

(もっと読む)

半導体装置

【課題】電子が第1励起準位に存在する割合が増えても、量子井戸層の中の電子の有効質量が軽くなる井戸層にできるだけ多くの電子が存在するようにして、より一層の高速化を実現する。

【解決手段】半導体装置を、基板10の上方に設けられた第1半導体層11と、第1半導体層11の上側に接する電子走行層24と、電子走行層24の上側に接する第2半導体層17(25)とを備えるものとし、電子走行層を24、第1井戸層13、中間障壁層14、第2井戸層15を順に積層させた構造を含む2重量子井戸層とし、中間障壁層14の伝導帯のエネルギーが、第1半導体層11及び第2半導体層17(25)の伝導帯のエネルギーよりも低くなり、第1井戸層13及び第2井戸層15の中に基底準位が形成され、2重量子井戸層の中に第1励起準位が形成されるようにする。

(もっと読む)

支持されたゲート電極を備えるトランジスタの作製方法およびそれに関連するデバイス

【課題】貫通する開口を備える保護層を基板上に形成し、さらにこの開口の中にゲート電極を形成することによって、トランジスタを作製する。

【解決手段】ゲート電極の第1の部分は、開口の外側に存在する保護層の表面部分で横方向に延在し、ゲート電極の第2の部分は、保護層から間隔を空けて配置され、第1の部分を越えて横方向に延在する。関連したデバイスおよび作製方法も述べられる。

(もっと読む)

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

窒化物系半導体素子

【課題】本実施形態は、窒化物半導体層のクラックがほとんどなく、表面の粗度が極めて優秀であるので、全体的な安定性の向上された窒化物系半導体素子を提供する。

【解決手段】本実施形態の窒化物系半導体素子は、基板と、前記基板上に形成されるアルミニウムシリコンカーバイド(AlSixC1−x)前処理層と、前記前処理層上に形成されるAlがドーピングされたGaN層と、前記AlがドーピングされたGaN層上に形成されるAlGaN層とを含む。

(もっと読む)

窒化物半導体基板及びその製造方法

【課題】より高いしきい値電圧と電流コラプス改善を両立できる、ノーマリーオフ型の高耐圧デバイスに好適な窒化物半導体基板及びその製造方法を提供する。

【解決手段】基板1と、前記基板1の一主面上に形成されるバッファー層2と、前記バッファー層2上に形成される中間層3と、前記中間層3上に形成される電子走行層4と、前記電子走行層4上に形成される電子供給層5とを含む窒化物半導体基板10において、前記中間層3を厚さ200nm以上1500nm以下、炭素濃度5×1016atoms/cm3以上1×1018atoms/cm3以下のAlxGa1-xN(0.05≦x≦0.24)とし、前記電子走行層4が厚さ5nm以上200nm以下のAlyGa1-yN(0≦y≦0.04)とする。

(もっと読む)

半導体装置

【課題】 本発明の目的は、半導体装置単体で負電源を必要とせずにスイッチングが可能な素子を提供することである。

【解決手段】 この発明の半導体装置は、ノーマリオンFETと、一方の電極を前記FETのゲートに、他方の電極を入力端子に電気的に接続されたキャパシタと、アノード電極が前記FETのゲートに、カソード電極が前記FETのソースに電気的に接続されたダイオードと、を前記FETと同一チップ上に形成したことを特徴としており、さらに、前記キャパシタが、前記FETのゲート引き出し電極上に誘電体などの絶縁膜を形成し、形成した前記絶縁膜に金属膜を形成することにより形成されたことが好ましい。

(もっと読む)

電界効果型トランジスタ

【課題】実用上十分なプロセスマージンを備える状態で、リーク電流の増大およびキャリア濃度の低下を招くことなく、ゲート電極とチャネル層との距離が短縮できるようにする。

【解決手段】InPからなる基板101の上に形成された電子供給層102と、電子供給層102の上に形成されたスペーサ層103と、スペーサ層103の上に形成されたチャネル層104と、チャネル層104の上に形成された障壁層105とを備え、障壁層105は、GaおよびAlの少なくとも1つと、Inと、Pとを含んだアンドープの化合物半導体から構成し、InPよりショットキー障壁高さが高いものとされている。

(もっと読む)

GaNHEMT装置用再成長ショットキー構造

【課題】高温で動作可能な高電子移動度トランジスタを提供する。

【解決手段】バッファ層16と、バッファ層16上のIII−V族層18と、III−V族層18上のソース接点20およびドレイン接点22と、III−V族層18上で、ソース接点20およびドレイン接点22間の再成長ショットキー層10と、成長ショットキー層10上のゲート接点24、を備える装置、および装置を用いたシステムを含む。さらに、装置とシステムの製造方法も含む。

(もっと読む)

化合物半導体装置及び化合物半導体装置の製造方法

【課題】トレンチを用いて素子分離され、且つ、隣接素子の動作による影響が抑制された化合物半導体装置及び化合物半導体装置の製造方法を提供する。

【解決手段】半導体基板10と、キャリア走行層21とキャリア供給層22を有し、半導体基板上に配置された窒化物半導体層20と、上端部がキャリア走行層とキャリア供給層との界面よりも上方に位置する空洞40を内部に有する、窒化物半導体層の周囲を囲んで配置された素子分離絶縁膜30とを備える。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

窒化物半導体装置

【課題】窒化物半導体装置において、高温且つ高電圧下のスイッチング時においても電流コラプスによるオン抵抗の増大が生じないようにする。

【解決手段】基板1上には、バッファ層2、GaNからなるチャネル層3及びアンドープAlGaNからなるバリア層4が順次形成されている。チャネル層3は、該チャネル層3の下部にp型不純物層3aを有し、その上にアンドープ層3bを有している。バリア層4及びチャネル層3の端部が除去されており、露出したバリア層4及びチャネル層3の側面と接するように、それぞれソース電極5及びドレイン電極6が設けられている。バリア層4上におけるソース電極5とドレイン電極6との間の領域にはゲート電極7が設けられている。

(もっと読む)

半導体積層体とこれを含むHFETおよびそれらの製造方法

【課題】半導体積層体に含まれるチャネル層下の化合物半導体層を不純物ドーピングでp型化することなく、その半導体積層体を含むHFETのリーク電流の低減や耐電圧の向上などを可能とする。

【解決手段】半導体積層体は、基板(11)上において順次堆積された第1、第2および第3の化合物半導体層(13、14、15)を少なくとも含み、その第1化合物半導体層(13)の少なくとも部分的層(16)は非晶質に改質されており、第2化合物半導体層(14)は第1化合物半導体層(13)に比べて小さなバンドギャップを有して光吸収層として作用し得る。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−SiO2の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−Si3N4の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

半導体装置

【課題】ピンチオフ特性の改善が可能な半導体装置を提供すること。

【解決手段】本発明は、SiC基板10上に設けられた第1のGaN層18と、第1のGaN層18上に設けられた第2のGaN層20(電子走行層)と、第2のGaN層20上に設けられ、GaNよりもバンドギャップが大きいAlGaN電子供給層16と、を有し、第1のGaN層18のアクセプタ濃度は第2のGaN層20のアクセプタ濃度よりも高い半導体装置である。

(もっと読む)

半導体装置

【課題】遷移金属のエネルギー準位を安定にすることが可能な半導体装置を提供することを目的とする。

【解決手段】本発明は、SiC基板10上に設けられ、遷移金属であるFeとFeよりも深い準位を有する不純物であるCとをそれぞれ一定の濃度で含有する第1のGaN層20と、第1のGaN層20上に設けられ、Feの濃度の変化に従いCの濃度が変化する第2のGaN層22と、第2のGaN層22上に設けられ、GaNよりもバンドギャップが大きい電子供給層18と、を有する半導体装置である。

(もっと読む)

半導体トランジスタおよびその製造方法

【課題】FETの閾値電圧のばらつきのない半導体トランジスタおよびその製造方法を提供する。

【解決手段】半導体トランジスタ100は、基板1と、基板1の上方に形成された第1化合物半導体層103と、第1化合物半導体層103上に形成され、第1化合物半導体層103よりもバンドギャップの大きい第2化合物半導体層104と、第2化合物半導体層104内の少なくとも一部に、酸素がドープされた酸素ドープ領域105と、第2化合物半導体層104上に形成された第3化合物半導体層106と、第1化合物半導体層103に電気的に接続されたソース電極107およびドレイン電極109と、酸素ドープ領域105の上方に、酸素ドープ領域105に接するように形成されたゲート電極108とを有する。

(もっと読む)

半導体基板の製造方法および半導体装置の製造方法

【課題】ノーマリーオフ半導体素子のための高品質の酸化物からなる絶縁膜を提供する。

【解決手段】半導体積層構造を有する基板3の上に、酸化物を含む絶縁膜を形成する工程において、酸化物を構成する元素単体ないしは元素の化合物を半導体積層構造を有する基板3の上に付着させる際に、水素ガス中に高純度水を加熱ないしは冷却することにより水蒸気圧を精密制御して混入させることにより、元素単体ないしは元素の化合物を酸化させる酸素分圧を精密に制御して、酸化物の組成を精密制御し、もって半導体積層構造を有する基板3と物理化学的に整合する絶縁膜を形成する。

(もっと読む)

1 - 20 / 113

[ Back to top ]