Fターム[5F102HC21]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | 熱処理(アニール) (453)

Fターム[5F102HC21]の下位に属するFターム

局部的アニール(レーザ、電子線照射) (10)

レジスト、ガラスの軟化 (1)

合金化、シリサイド化 (42)

Fターム[5F102HC21]に分類される特許

141 - 160 / 400

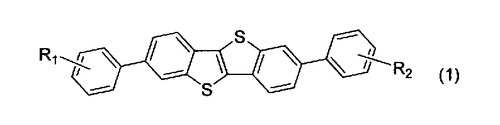

縦型有機半導体デバイス

【課題】雰囲気安定性、高ON/OFF比、高電流密度等の優れた特性を有する実用的な縦型有機半導体デバイスを提供する。

【解決手段】一般式(1)で表される化合物を半導体材料として含む、縦型有機半導体デバイス。

(R1及びR2はそれぞれ独立に置換基を有してもよい芳香族基を表す)

(もっと読む)

半導体装置

【課題】破損を抑制できる半導体装置を提供する。

【解決手段】半導体装置1は、シリコンを含む材料からなる基板2と、基板2上に形成された緩衝層3と、緩衝層3上に形成された窒化物系半導体を含むデバイス形成層4とを有する。緩衝層3は、アルミニウムを含む第1の窒化物系半導体層11と、第1の窒化物系半導体層11の上に形成され、アルミニウムの含有率が徐々に減少する第1の組成傾斜層12と、第1の組成傾斜層12の上に形成され、アルミニウムを含まないまたは第1の窒化物系半導体層11よりもアルミニウムの含有率が少ない第2の窒化物系半導体層13と、第2の窒化物系半導体層13の上に形成され、アルミニウムの含有率が徐々に増加する第2の組成傾斜層14とを順番に複数回積層したものである。第1の組成傾斜層12は、第2の組成傾斜層14よりも厚い。

(もっと読む)

半導体装置の製造方法

【課題】窒化物半導体層を有する半導体装置を低コストで製造する。

【解決手段】基板上に第1の窒化物半導体の犠牲層を形成する犠牲層形成工程と、前記犠牲層上に第2の窒化物半導体層を形成し、前記第2の窒化物半導体層上に窒化物半導体層を積層した積層窒化物半導体層を形成する積層半導体形成工程と、前記犠牲層の表面が露出するまで、前記第2の窒化物半導体層及び前記積層窒化物半導体層をエッチングすることによりトレンチを形成し、前記トレンチ及び前記積層窒化物半導体層表面に接続電極を形成する接続電極形成工程と、前記接続電極の形成された前記基板を電解液に浸漬させ、前記電解液に対し前記接続電極に電位を印加し、前記犠牲層を除去し前記基板を剥離する犠牲層除去工程とを有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体素子

【課題】バッファ層を介した電極間のリーク電流を抑制した半導体素子を提供する。

【解決手段】本半導体素子は、基板10に形成された第1のAlXGa1−XN層14a及び第1のAlXGa1−XN層14aよりAl組成Xの大きい第2のAlXGa1−XN層14bが交互に積層して形成された超格子バッファ層14を有する。そして、第1のAlXGa1−XN層14a及び第2のAlXGa1−XN層14bのAl組成Xは共に0.3より大きく、かつ第1のAlXGa1−XN層14a及び第2のAlXGa1−XN層14bのAl組成Xの差は0より大きく0.6より小さい。この構成によれば、バッファ層を介したリーク電流を低減することができる。

(もっと読む)

接合型電界効果トランジスタ

【課題】J−FETでは、ゲート領域およびバックゲート領域からのp型不純物拡散により、ゲート領域直下のチャネル領域のn型不純物濃度が低下し、IDSSばらつきや、順伝達アドミタンスgm、電圧利得Gvの劣化やノイズ電圧Vnoが増加する問題があった。

【解決手段】バックゲート領域となるp型半導体基板表面にソース領域5、ドレイン領域6を設け、これらの間のp型半導体基板表面にチャネル領域4を設ける。チャネル領域4下方のp型半導体基板に、ゲート領域7を設け、ゲート領域7の上面は、チャネル領域4下面と接触する。これにより、チャネル領域4の不純物拡散ばらつきを防止し、チャネル深さばらつきを抑制できる。従って電流経路の抵抗値を略均一にでき、DSSを安定化させ、順伝達アドミタンスgm、電圧利得Gvを向上させ、ノイズ電圧Vnoを低減できる。更に同一ウエハ内でのIDSSばらつきも抑制できる。

(もっと読む)

半導体装置及びその製造方法

【課題】接合型電界効果トランジスタ等の半導体装置において、オン抵抗を低減できるようにする。

【解決手段】半導体装置の製造方法は、まず、基板101の上に第1の窒化物半導体層103、第2の窒化物半導体層104及びp型の第3の半導体層105を順次エピタキシャル成長する。これよりも後に、第3の半導体層105を選択的に除去する。これよりも後に、第2の窒化物半導体層104の上に、第4の窒化物半導体層106をエピタキシャル成長する。これよりも後に、第3の半導体層105の上にゲート電極を形成する。

(もっと読む)

電界効果トランジスタ

【課題】耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】p型の導電型を有する基板と、前記基板上に形成された高抵抗層と、前記高抵抗層上に形成され、p型の導電型を有するp型半導体層を前記基板側に配置したリサーフ構造を有する半導体動作層と、前記半導体動作層上に形成されたソース電極、ドレイン電極、およびゲート電極と、を備える。好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたn型の導電型を有するリサーフ層を備える。また、好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたアンドープのキャリア走行層と、前記キャリア走行層上に形成され該キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層とを備える。

(もっと読む)

III族窒化物半導体からなるHFETの製造方法

【課題】ノーマリオン型HFETの閾値電圧の簡易な調整方法を提供すること。

【解決手段】i−AlGaN層12のゲート電極15を形成する領域のみを開口させたパターンのマスク17を形成する。開口されたi−AlGaN層12の領域に、CF4 ガスプラズマを照射し、ダメージ層16を形成する(図2(c))。CF4 ガスプラズマの照射時間によってダメージ層16の厚さを調整することで、実質的なi−AlGaN層12の厚さを調整することができ、これにより閾値電圧を調整することができる。

(もっと読む)

電界効果型トランジスタ

【課題】ドレイン電極からのリーク電流を防止できる電界効果型トランジスタを提供する。

【解決手段】この電界効果型トランジスタによれば、WN/Alドレイン電極109がドレイン電極109の下のn+型領域(拡散領域)112を介してGaNチャネル層104にショットキー接合されている。これにより、従来の熱処理によりドレイン電極にオーミックコンタクトを形成する場合と異なり、ドレイン電極109下へメタルが侵入することを回避できる。よって、このメタル侵入が発生するために生じるリーク電流を低減することが可能であり、電界効果型トランジスタにおける破壊電圧を向上できる。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗なオーミック性を有し、酸・アルカリによる腐食に対し高い耐性を持つ電極を備えた半導体装置及びその製造方法を提供することを目的とする。

【解決手段】窒化物半導体層1と、窒化物半導体層1上に設けられた電極と、を備え、電極は、窒化物半導体層1上に設けられた第一金属層2と、第一金属層2上に設けられた第二金属層3と、前記第二金属層3上に設けられた第三金属層4と、を備え、第一金属層2は第二金属層3よりも窒化物半導体層1との高い密着性を有する金属を含み、第二金属層3は第一金属層2よりも低抵抗で窒化物半導体層1に対してオーミック性を有する金属を含み、第三金属層4は水素よりもイオン化傾向の小さい金属を含むことを特徴とする、半導体装置。

(もっと読む)

窒化物半導体装置

【課題】窒化物半導体装置の表面安定化を実現し、これにより、電流コラプスを抑制した窒化物半導体装置を提供する。

【解決手段】第1の窒化物半導体からなるキャリア走行層103と、キャリア走行層103の上方に設けられた第2の窒化物半導体からなるキャリア供給層104と、キャリア走行層103とオーミック接触するソース電極106及びドレイン電極107と、キャリア供給層104の上方に設けられたゲート電極110とを備え、ゲート電極110とドレイン電極107との間において、キャリア供給層104の表面の少なくとも一部が、構成元素として窒素元素を含む窒化物絶縁膜で覆われ、窒化物絶縁膜において、窒素元素の含有量が他の構成元素の含有量の合計よりも多い。

(もっと読む)

トランジスタ実装体及びその製造方法

【課題】チャネル抵抗を大幅に低減した電界効果トランジスタ実装体を実現できるようにする。

【解決手段】トランジスタ実装体の製造方法は、トランジスタ100を形成する工程(a)と、形成基板101を研磨する工程(b)と、形成基板101を研磨したトランジスタ100を保持基板200に固定する工程(c)とを備えている。工程(a)は、形成基板101の主面上に第1の半導体層及び該第1の半導体層よりもバンドギャップが大きい第2の半導体層を順次形成する。工程(b)は、形成基板101における主面と反対側の面を研磨する。工程(c)は、形成基板101の反りが小さくなる方向の応力を形成基板101に印加した状態でトランジスタ100を保持基板200の上に固定する。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】 パワーデバイスに必要な特性を確保しながら、コストを低減することができる窒化物半導体素子およびその製造方法を提供すること。

【解決手段】 CAVET1において、シリコン基板2上に、AlN構造8を有するバッファ層4、電子走行層6、および電子供給層7を積層した構造を有し、電子走行層6および電子供給層7に跨る壁面16を有する積層構造部3を形成する。バッファ層4と電子走行層6との間には、開口部13を有するマスク層12を形成する。ソース電極18は、電子供給層7上に形成し、ゲート電極20は、電子供給層7上におけるソース電極18よりも壁面16寄りの位置に設ける。ドレイン電極30は、シリコン基板2の裏面22側からシリコン基板2およびバッファ層4を貫通するように設ける。そして、壁面16に沿って埋込電極17を設け、開口部13を介してドレイン電極30に電気的に接続する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された電子走行層2と、電子走行層2上方に形成された電子供給層3と、電子供給層3上方に形成されたソース電極7s、ドレイン電極7d及びゲート電極7gと、が設けられている。ソース電極7sと電子供給層3との間の抵抗は、ゲート電極7gから離間するほど低くなっており、ドレイン電極7dと電子供給層3との間の抵抗は、ゲート電極7gから離間するほど低くなっている。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタ製造方法

【課題】ゲート電極材料の耐熱上の問題を克服し、ソース抵抗の低減が可能な電界効果トランジスタを提供する。

【解決手段】ゲート電極9を挟んでソース電極8、ドレイン電極10をそれぞれ形成するソース領域3、ドレイン領域6のいずれか一方または双方の領域にイオンを注入し活性化した第1の高濃度キャリア領域6と、ゲート電極9の直下に形成したチャネル領域4と第1の高濃度キャリア領域6との間の領域に、熱処理によりキャリアを拡散させた熱拡散領域7の第2の高濃度キャリア領域とを形成し、第1の高濃度キャリア領域6は、チャネル領域4と互いに隣接して形成される第2の高濃度キャリア領域7と隣接および/または一部重複し、かつ、チャネル領域4以上に深く形成した第2の高濃度キャリア領域7よりも深く形成する。第1の高濃度キャリア領域6のキャリア濃度を、チャネル領域4よりも高濃度の第2の高濃度キャリア領域7よりさらに高くする。

(もっと読む)

半導体装置

【課題】窒化物半導体から成るヘテロ接合電界効果型トランジスタに於いて、バリア層上に2次元電子ガス濃度を減少させずに略50nm以上のキャップ層を形成するには、シリコンを1×1019cm-2程度の高濃度でドーピングする必要があるが、この様な高い濃度のシリコンを均一性良くドーピングするのは困難である。窒化物半導体では酸素及び窒素空孔の様なエピタキシャル成長中等に意図せずに混入するドナーがあるため、シリコンだけでドーピング濃度を制御することが難しい。

【解決手段】キャップ層50内でヘテロ接合の形成により発生する分極の影響を受けるバリア層40側の領域に、キャップ層50を構成する窒化物半導体のバンドギャップ内の分極の効果によって決まるフェルミ・レベルよりも高いエネルギー位置に準位を形成する複数のドナーが、合計して2次元電子ガス濃度と同程度の濃度でドーピングされている。

(もっと読む)

接合型FET、半導体装置およびその製造方法

【課題】JFETの電気的特性を改善すること。

【解決手段】N型基板201上のPウェル202内部にN型チャネル領域203がある。N型チャネル領域203上にP型ゲート領域103がある。ゲート領域103の中にN型ソース領域107及びドレイン領域106が互いに平行に配置され、それらはN型チャネル203に接続されている。ゲート領域103を配線に接続するためにP型ゲートコンタクト領域104がソース領域107及びドレイン領域106から離れた位置に設けられている。N型チャネル203とPウェル202との境界の上に平坦な分離用のシリコン熱酸化膜204があり、その上に分離用の多結晶シリコン101がある。多結晶シリコン101より外側のPウェル202の上に配線を接続するためにPウェルコンタクト領域102がある。

(もっと読む)

半導体装置、半導体装置の製造方法および半導体装置のリーク電流低減方法

【課題】耐圧特性を向上させ且つリーク電流を低減することが可能な半導体装置、半導体装置の製造方法および半導体装置のリーク電流低減方法を提供する。

【解決手段】HFET100は、支持基板であるサファイア基板101と、サファイア基板101上のバッファ層102と、バッファ層102上のキャリア走行層103と、キャリア走行層103上のキャリア供給層104と、キャリア供給層104上に離間して設けられたソース106sおよびドレイン106dと、キャリア供給層104上におけるソース106sとドレイン106dとの間に設けられたゲート107と、キャリア供給層104上を覆う絶縁膜105と、を備える。キャリア供給層104は、カーボン濃度が2×1017cm−3以上である。

(もっと読む)

III族窒化物基板、それを備える半導体デバイス、及び、表面処理されたIII族窒化物基板を製造する方法

【課題】 安定した表面を有するIII族窒化物基板を提供する。

【解決手段】 一実施形態に係るIII族窒化物基板は、表面層を有している。当該表面層は、3at.%の〜25at.%の炭素を含み、且つ、5×1010原子/cm2〜200×1010原子/cm2のp型金属元素を含んでいる。このIII族窒化物基板は、安定した表面を有するものとなる。

(もっと読む)

半導体装置およびその製造方法

【課題】SiCを素材として採用することで本来得られる特性をより確実に得ることが可能な半導体装置およびその製造方法を提供する。

【解決手段】JFET1は、少なくとも上部表面14Aが炭化珪素からなるウェハ10と、上部表面14A上に形成されたゲートコンタクト電極21とを備える。ウェハ10は、上部表面14Aを含むように形成されたイオン注入領域である第1のp型領域16を含む。第1のp型領域16は、上部表面14Aを含むように配置されるベース領域16Aと、突出領域16Bとを含む。ベース領域16Aは、上部表面14Aに沿った方向における幅w1が、突出領域16Bの幅w2よりも広い。ゲートコンタクト電極21は、平面的に見てその全体が第1のp型領域16に重なるように、第1のp型領域16に接触して配置されている。

(もっと読む)

141 - 160 / 400

[ Back to top ]