Fターム[5F102HC21]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | 熱処理(アニール) (453)

Fターム[5F102HC21]の下位に属するFターム

局部的アニール(レーザ、電子線照射) (10)

レジスト、ガラスの軟化 (1)

合金化、シリサイド化 (42)

Fターム[5F102HC21]に分類される特許

121 - 140 / 400

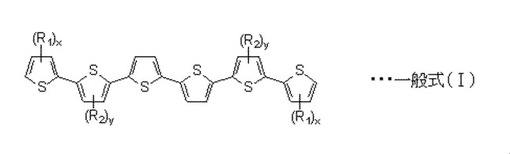

有機半導体材料およびこれを用いた有機薄膜トランジスタ

【課題】汎用溶媒に対する溶解性が非常に高く、湿式成膜が可能な低コストプロセスに適応可能であり、さらに、容易に均質性の高い薄膜を得ることが可能な有機エレクトロニクス用材料として有用なオリゴチオフェン類からなる有機半導体材料およびこれを用いた有機薄膜トランジスタを提供する。

【解決手段】下記一般式(I)で表わされることを特徴とする有機半導体材料。

(式中、R1およびR2は、互いに異なるアルキル基を表わし、xおよびyは、それぞれ独立に1または2の整数を表わす。)

(もっと読む)

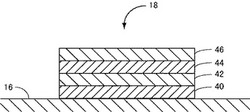

電子デバイス及びオーミック電極形成方法

【課題】低温短時間のアニールによっても、低いコンタクト抵抗を得ることのできるオーミック電極を備える電子デバイスを提供する。

【解決手段】電子デバイスは、ワイドバンドギャップ化合物半導体層16と、ワイドバンドギャップ化合物半導体層16上に形成されるオーミック電極であるソース電極18及びドレイン電極とを含む電子デバイスであって、オーミック電極は、密着層40、オーミック層42、及び、酸化防止層46が、ワイドバンドギャップ化合物半導体層16側からこの順に積層されて形成された電極であり、密着層40は、バナジウム(V)からなり、かつ、厚みが300Å以下であるようにする。

(もっと読む)

電界効果トランジスタ、及び電界効果トランジスタの製造方法

【課題】電界効果トランジスタの局所的な温度を測定することが可能な電界効果トランジスタを提供することである。

【解決手段】本発明にかかる電界効果トランジスタは、半導体層5と、半導体層5とオーミック接合したソース電極1と、半導体層5とオーミック接合したドレイン電極2と、半導体層5とショットキ接合したゲート電極3と、ソース電極1の一部に形成された空隙に設けられた、半導体層5とショットキ接合したショットキ電極4と、を有する。また、本発明にかかる他の態様の電界効果トランジスタは、半導体層5と、半導体層5とオーミック接合したソース電極1と、半導体層5とオーミック接合したドレイン電極2と、半導体層5とショットキ接合したゲート電極1と、ドレイン電極2の一部に形成された空隙に設けられた、半導体層5とショットキ接合したショットキ電極4と、を有する。

(もっと読む)

半導体装置

【課題】インパクトイオン化現象によって発生した電子・正孔を効率よく吸収することが可能で正常な動作特性と高い信頼性を実現する半導体装置を提供する。

【解決手段】半導体装置20は、基板21に対して順次積層されたバッファ層22、下地化合物半導体層23f(下地化合物半導体層23)、インパクトイオン制御層24、下地化合物半導体層23s(下地化合物半導体層23)、チャネル画定化合物半導体層26f(チャネル画定化合物半導体層26)、チャネル画定化合物半導体層26s(チャネル画定化合物半導体層26)、AlGaN(窒化アルミニウムガリウム)層28、GaN(窒化ガリウム)層29を備えている。インパクトイオン制御層24は、下地化合物半導体層23の積層範囲(積層範囲の厚さTst)内に積層されてインパクトイオン化現象の発生位置を制御する。

(もっと読む)

ヘテロ接合電界効果トランジスタ、その製造方法

【課題】ゲート電極下の電子の走行方向が基板表面に略平行であるようにデバイス構造を改良しながらも各種弊害を解消したヘテロ接合電界効果トランジスタを提供する。

【解決手段】n型導電層は選択的にイオン注入されているシリコン(Si)などのn型不純物をアニール処理で活性化することにより形成されており、n型導電層は、イオンが200keV以上の加速エネルギーで注入されており、p型窒化物半導体層より深く、かつドレイン電極114と導通する半導体層にまで注入イオンが達する選択的イオン注入によって形成されており、n型導電層とn型不純物が注入されていないチャネル領域との接続部115に注入されているn型不純物濃度が1×1018cm−3以下である。

(もっと読む)

半導体装置

【課題】ドレイン電極部分での破壊を抑制して、耐圧を向上できる半導体装置を提供する。

【解決手段】ドレイン電極105は、バリア層102に、ショットキー接触するショットキー電極である。このように、ドレイン電極105を、高温アニールで合金化してバリア層102にオーミック接触することなく、形成できる。したがって、ドレイン電極105部分において破壊電界が低くならないので、ドレイン電極105部分での破壊を抑制して、耐圧を向上できる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好な高周波特性及び電流コラプスの低減を両立することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成された表面保護膜10と、化合物半導体積層構造2上方に形成されたソース電極4、ドレイン電極5及びゲート電極6と、が設けられている。ゲート電極6には、その下面が化合物半導体積層構造2に接する接合部6aと、接合部6aよりもドレイン電極5側において、その下面が表面保護膜10の上面に接する乗り上がり部6bと、乗り上がり部6bよりもドレイン電極5側に位置し、その下面と表面保護膜10の上面との間に表面保護膜10よりも誘電率が低い領域が介在する離間部6cと、が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ低抵抗の半導体装置およびその製造方法を提供すること。

【解決手段】基板と、前記基板上に形成された半導体層と、前記半導体層上に形成され、該半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極と、を備える。また、基板上に半導体層を形成する半導体層形成工程と、前記半導体層上に、前記半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極を形成する電極形成工程と、を含む。

(もっと読む)

3−5族化合物半導体

【課題】窒化物系化合物半導体において埋め込み電極として利用可能な特定のパターン形状の導電性材料を埋め込んだ構造を実現し、SIT等のデバイスを作製可能にする。

【解決手段】(1)一般式InxGayAlzN(ただし、x+y+z=1、0≦x≦1、0≦y≦1、0≦z≦1)で表される第1の3−5族化合物半導体と、(2)これに接して該第1の3−5族化合物半導体表面の一部を特定のパターン形状で被覆するSiO2と、(3)該SiO2に接して積層された導電性材料と、(4)該SiO2と該導電性材料との積層体で被覆されてない該第1の3−5族化合物半導体表面の露出部と該導電性材料とを共に被覆する一般式InuGavAlwN(ただし、u+v+w=1、0≦u≦1、0≦v≦1、0≦w≦1)で表される第2の3−5族化合物半導体と、からなり、該導電性材料の層厚が5nm以上100nm以下であることを特徴とする3−5族化合物半導体。

(もっと読む)

窒化物半導体装置および窒化物半導体装置製造方法

【課題】窒素不足に起因する移動度の低下を抑制し、窒素不足に起因するリーク電流を低減することができる窒化物半導体装置、その製造方法を提供する。

【解決手段】窒化物半導体装置1は、基板10と、バッファ層11と、窒化物半導体層(第1窒化物半導体層12、第2窒化物半導体層13、第3窒化物半導体層14)と、第1電極22と、第2電極23と、制御電極25とを備える。第1電極22と第2電極23との間で第3窒化物半導体層14の表面から第2窒化物半導体層13に渡って凹状に形成されたリセス部16を備え、リセス部16は、絶縁性窒化物で形成された窒化物絶縁膜17を備え、制御電極25は、導電性窒化物で形成され窒化物絶縁膜17(ゲート絶縁膜)に重ねて配置されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】オン抵抗を低減することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板上方に、表面が(0001)面の第1の化合物半導体層13b、及び表面が(000−1)面の第2の化合物半導体層13aを互いに接するように形成し、第1の化合物半導体層13b上に第1の化合物半導体層13bよりも格子定数が小さい第3の化合物半導体層14bを形成し、第2の化合物半導体層13a上に第2の化合物半導体層13aよりも格子定数が小さい第4の化合物半導体層14aを形成する。また、前記第1の化合物半導体層に電位を付与する第1の電極、及び前記第2の化合物半導体層に電位を付与する第2の電極を形成する。

(もっと読む)

3−5族化合物半導体

【課題】窒化物系化合物半導体において埋め込み電極として利用可能な特定のパターン形状の導電性材料を埋め込んだ構造を実現し、SIT等のデバイスを作製可能にする。

【解決手段】(1)GaN層上にGaAlNを積層した構造である第1の3−5族化合物半導体と、(2)これに接して該第1の3−5族化合物半導体表面の一部を特定のパターン形状で被覆する導電性材料と、(3)該導電性材料で被覆されてない該第1の3−5族化合物半導体表面の露出部と該導電性材料とを共に被覆する一般式InuGavAlwN(ただし、u+v+w=1、0≦u≦1、0≦v≦1、0≦w≦1)で表される第2の3−5族化合物半導体と、からなり、該導電性材料の層厚が5nm以上100nm以下である3−5族化合物半導体。

(もっと読む)

横型接合型電界効果トランジスタ

【課題】漏れ電流の発生を防止すると共に、十分な耐圧を実現することが可能な横型接合型電界効果トランジスタを提供する。

【解決手段】この発明に従った横型JFET10では、バッファ層11は、SiC基板1の主表面上に位置し、p型不純物を含む。チャネル層12は、バッファ層11上に位置し、バッファ層11におけるp型不純物の濃度より高い濃度のn型不純物を含む。n型のソース領域15およびドレイン領域16は、チャネル層12の表面層において互いに間隔を隔てて形成され、p型のゲート領域17は、チャネル層12の表面層においてソース領域15およびドレイン領域16の間に位置する。バリア領域13は、チャネル層12とバッファ層11との境界領域において、ゲート領域17の下に位置する領域に配置され、バッファ層11におけるp型不純物の濃度より高い濃度のp型不純物を含む。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】単一半導体基板上にHBTおよびFETのような複数異なる種類のデバイスを形成するに適した半導体基板を製造する方法を提供する。

【解決手段】半導体を結晶成長させる反応容器内に第1不純物原子を構成要素として有する単体または化合物を含む第1不純物ガスを導入する段階を含む複数の段階を繰り返して、複数の半導体基板を製造する方法であって、第1不純物ガスを導入する段階の後に、製造された半導体基板を取り出す段階と、反応容器内に第1半導体を設置する段階と、反応容器内に、第1半導体内で第1不純物原子と反対の伝導型を示す第2不純物原子を構成要素として有する単体または化合物を含む第2不純物ガスを導入する段階と、第1半導体を第2不純物ガスの雰囲気中で加熱する段階と、加熱した前記第1半導体上に第2半導体を結晶成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】電流コラプスを減少し耐圧を維持しつつ、オン抵抗を改善した、高電圧、高周波で動作する半導体装置を提供する。

【解決手段】この発明にかかる半導体装置は、ヘテロ接合型の窒化物半導体装置であって、基板1上に形成されたチャネル層2と、チャネル層2上に形成された電子供給層3と、電子供給層3上に選択的に形成されたゲート電極5と、ゲート電極5を挟み離間して形成されたソース、ドレイン電極4a,4bと、ゲート電極5のドレイン電極側端部近傍を除く第1領域に形成され、当該第1領域に対応する二次元電子ガス濃度に作用する第1薄膜である薄膜8と、ゲート電極5のドレイン電極側端部近傍の第2領域に形成され、当該第2領域に対応する二次元電子ガス濃度に作用し、当該濃度を第1領域に対応するそれよりも低くする第2薄膜である薄膜6とを備える。

(もっと読む)

窒化物半導体装置

【課題】p型の窒化物半導体層からのマグネシウムの拡散を防止するとともに良好なノーマリオフ特性を確保することができる窒化物半導体装置を提供する。

【解決手段】窒化物半導体装置100は、nチャネル型の縦型のHEMTである。窒化物半導体装置100は、n型の第3窒化物半導体層4の表面の一部にマグネシウムが含有されているp型の第1窒化物半導体層6a、6bを備えている。第1窒化物半導体層6a、6bの表面に臨む範囲には、イオン注入されたアルミニウムが含有されているAl含有領域8a、8bが形成されている。Al含有領域8a、8bはマグネシウムの拡散を防止する。また、Al含有領域8a、8bの表裏両面に二次元電子ガス層が発生することが抑制され、リーク電流が流れることが抑制される。

(もっと読む)

半導体装置

【課題】リセスゲート構造のヘテロ接合FETにおいて、デルタドーピングによらずドレイン電流の低減を抑止することを目的とする。

【解決手段】本発明の半導体装置は、ゲート電極10と、ゲート電極10の両側に離間して夫々設けられたドレイン電極9及びソース電極8と、少なくともゲート電極10のドレイン電極9側の側面に接するように設けられた不純物ドーピング濃度が異なる二層以上のキャップ層と、を備え、キャップ層の最下層(第一キャップ層5)の厚さdが式(1)で表されることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容易にノーマリオフ特性を向上させることができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、一方の主面5aの一部に凹部16が形成された窒化物系半導体層3〜5と、一方の主面5aに設けられたソース電極7と、凹部16を挟みソース電極7とは反対側であって、一方の主面5aに設けられたドレイン電極8と、一方の主面5aの凹部16を挟み両側に形成され、凹部16側の壁面17が傾斜した絶縁層6と、凹部16の底面16a上及び側面16b上並びに絶縁層6の凹部16側の壁面17上に設けられたゲート電極10とを備えている。絶縁層6の壁面17の傾斜角βは、凹部16の側面16bの傾斜角αよりも大きい。

(もっと読む)

半導体装置

【課題】破損を抑制できる半導体装置を提供する。

【解決手段】半導体装置1は、シリコンを含む材料からなる基板2と、基板2上に形成された緩衝層3と、緩衝層3上に形成された窒化物系半導体を含むデバイス形成層4とを有する。緩衝層3は、アルミニウムを含む第1の窒化物系半導体層11と、第1の窒化物系半導体層11の上に形成され、アルミニウムの含有率が徐々に減少する第1の組成傾斜層12と、第1の組成傾斜層12の上に形成され、アルミニウムを含まないまたは第1の窒化物系半導体層11よりもアルミニウムの含有率が少ない第2の窒化物系半導体層13と、第2の窒化物系半導体層13の上に形成され、アルミニウムの含有率が徐々に増加する第2の組成傾斜層14とを順番に複数回積層したものである。第1の組成傾斜層12は、第2の組成傾斜層14よりも厚い。

(もっと読む)

半導体装置の製造方法

【課題】窒化物半導体層を有する半導体装置を低コストで製造する。

【解決手段】基板上に第1の窒化物半導体の犠牲層を形成する犠牲層形成工程と、前記犠牲層上に第2の窒化物半導体層を形成し、前記第2の窒化物半導体層上に窒化物半導体層を積層した積層窒化物半導体層を形成する積層半導体形成工程と、前記犠牲層の表面が露出するまで、前記第2の窒化物半導体層及び前記積層窒化物半導体層をエッチングすることによりトレンチを形成し、前記トレンチ及び前記積層窒化物半導体層表面に接続電極を形成する接続電極形成工程と、前記接続電極の形成された前記基板を電解液に浸漬させ、前記電解液に対し前記接続電極に電位を印加し、前記犠牲層を除去し前記基板を剥離する犠牲層除去工程とを有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

121 - 140 / 400

[ Back to top ]