Fターム[5F102HC21]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | 熱処理(アニール) (453)

Fターム[5F102HC21]の下位に属するFターム

局部的アニール(レーザ、電子線照射) (10)

レジスト、ガラスの軟化 (1)

合金化、シリサイド化 (42)

Fターム[5F102HC21]に分類される特許

101 - 120 / 400

窒化物半導体装置

【課題】パワートランジスタに適用可能なノーマリオフ型の窒化物半導体装置に生じる電流コラプスを抑制できるようにする。

【解決手段】窒化物半導体装置は、サファイアからなる基板11と、該基板11の上に形成されたGaNからなるチャネル層13と、該チャネル層13の上に形成され、該チャネル層13よりもバンドギャップエネルギーが大きいAlGaNからなるバリア層14と、該バリア層14の上に形成され、p型AlGaN層15及びp型GaN層16を含むp型窒化物半導体層と、該p型窒化物半導体層の上に形成されたゲート電極19と、該ゲート電極19の両側方の領域にそれぞれ形成されたソース電極17及びドレイン電極18とを有している。p型窒化物半導体層は、ゲート電極19の下側部分の厚さが該ゲート電極19の側方部分の厚さよりも大きい。

(もっと読む)

縦型パワートランジスタ装置、半導体チップ、および縦型パワートランジスタ装置の製造方法

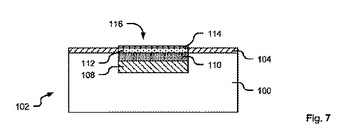

縦型トランジスタ装置は、III−V族半導体材料から形成される基板(100)と、少なくとも部分的に基板内に収容される多層スタック(116)とを備える。多層スタックは、基板(100)に隣接して配置される半絶縁層(108)と、第1のIII−V族半導体材料から形成されており、半絶縁層に隣接して配置される第1の層(110)とを備える。多層スタック(116)はまた、第2のIII−V族半導体材料から形成されて、第1の層(110)に隣接する第2の層(112)と、第1の層と第2の層との界面に形成されるヘテロ接合部とを備える。  (もっと読む)

(もっと読む)

集積半導体基板構造の製造方法

【課題】GaN素子およびCMOS素子の両方を備えた集積回路を製造するための改善した方法を提供する。

【解決手段】集積半導体基板構造100は、基板11と、GaNヘテロ構造20と、半導体基板層30とを備える。GaNヘテロ構造20は、第1素子エリアに存在し、少なくとも部分的に保護層8で覆われている。半導体基板層30は、CMOS素子の区画のための第2素子エリアに存在する。GaNヘテロ構造20および半導体基板層30の少なくとも1つが、基板11の少なくとも1つの溝内をエピタキシャル成長して形成され、GaNヘテロ構造20および半導体基板層30は横方向に並置される。

(もっと読む)

半導体素子およびその製造方法

【課題】より高いブレークダウン電圧に適した半導体素子構造およびその製造方法を提供する。

【解決手段】半導体基板構造(100)は、半導体基板(1)と、半導体基板(1)の上部にGaNタイプの層スタック(20)とを備える。GaNタイプ層スタック(20)は、少なくとも1つのバッファ層(21,22)と、第1活性層(2)と、第2活性層(3)とを備え、第1活性層と第2活性層の界面において、能動素子領域が規定可能である。半導体基板(1)は、絶縁層(12)の上に存在しており、所定のパターンに従って溝(14)を規定するようにパターン化され、そのパターンは、こうした能動素子領域の下地となる少なくとも1つの溝(14)を含み、前記溝(14)は、絶縁層(12)から、GaNタイプ層スタック(20)の少なくとも1つのバッファ層(21,22)の中まで延びて、前記少なくとも1つのバッファ層(22)の範囲で過成長しており、第1および第2活性層(2,3)は、少なくとも能動素子領域の範囲で連続している。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗を低く、移動度を高く、かつピンチオフ特性を良好にした上で、ドレイン電圧を増大させてもキンク現象が生じない、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】開口部28が設けられたGaN系積層体15と、チャネルを含む再成長層27と、ゲート電極Gと、ソース電極Sと、ドレイン電極Dとを備え、再成長層27は電子走行層22および電子供給層26を含み、GaN系積層体には再成長層に開口部でその端面が被覆されるp型GaN層6が含まれ、そのp型GaN層にオーミック接触するp部電極11を備えることを特徴とする。

(もっと読む)

高電子移動度トランジスタ、エピタキシャル基板、及び高電子移動度トランジスタを作製する方法

【課題】ノーマリオフ特性を実現する高電子移動度トランジスタを提供する。

【解決手段】チャネル層25が第1のバリア層27上に設けられると共に第1のバリア層27と第1のヘテロ接合33を成す。また、チャネル層25は圧縮歪みを内包して、チャネル層25のピエゾ電界PZC2は支持基体13から第1のバリア層27への方向に向く。第1のヘテロ接合33がIII族窒化物領域23のc軸方向に対して40度以上85度以下及び140度以上180度未満の角度範囲の傾斜角αで傾斜した基準軸ベクトルに垂直な平面に沿って延在するとき、ゲート電極19直下におけるチャネル層25におけるピエゾ電界PZC2の大きさをc面上のトランジスタにおけるピエゾ電界の大きさに比べて小さくできて、有限な大きさのピエゾ電界を残しながらノーマリオフ特性が実現される。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】 窒化物半導体に対するコンタクト抵抗が低い電極を有する半導体装置の製造方法を提供する。

【解決手段】 窒化物半導体層上に炭素を含有する炭素含有層を形成する炭素含有層形成工程S4と、炭素含有層上にチタンを含有するチタン含有層を形成するチタン含有層形成工程S6を有する半導体装置の製造方法。チタン含有層と窒化物半導体層との間にTiNとTiCの全率固溶体Ti(C,N)の層が形成される。これにより、チタン含有層が、その境界部全体で窒化物半導体層に対してオーミック接続される。

(もっと読む)

電力電子素子及びその製造方法並びに電力電子素子を含む集積回路モジュール

【課題】2DEG(2−Dimensional Electron Gas)チャネルを持つ電力電子素子及びその製造方法を提供する。

【解決手段】本発明にかかる電力電子素子は、2DEGチャネルを形成する、順次に形成された下部及び上部物質層と、上部物質層の上面上に接触したゲートを含み、2DEGチャネルのゲート下領域はオフ領域であり、前記オフ領域で2DEGの密度は最小または0である。上部物質層の全体は、連続的で均一な厚さを持つことができる。ゲート下部の上部物質層は、下部及び上部物質層の間の格子定数差を最小化するか、またはなくす不純物を含むことができる。

(もっと読む)

電界効果トランジスタの製造方法

【課題】ゲート長が短い電界効果トランジスタを低コストで製造できる電界効果トランジスタの製造方法を提供すること。

【解決手段】基板上に、窒化物系化合物半導体からなるチャネル層および該チャネル層上に積層した上部層を含む半導体層を形成する工程と、半導体層の一部領域を少なくとも上部層からチャネル層に到る深さまでエッチングして、該チャネル層の表面の一部を底面部とし、エッチングによって露出した半導体層の側面を側壁部とする段差部を形成する工程と、段差部を含む半導体層の表面を覆うようにマスク層を形成し、該マスク層をエッチバックして該段差部のマスク層を残留させたマスク部を形成する工程と、イオン注入法によって、底面部のマスク部を除く領域にコンタクト領域を形成する工程と、マスク部を除去した後に、少なくとも段差部の底面部と側壁部とを覆うようにゲート絶縁膜およびゲート電極を順次形成する工程と、を含む。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】本発明は、耐圧特性を維持したままアクセス抵抗を低減して高速動作が可能な窒化物半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明による窒化物半導体装置は、窒化物半導体を用いたヘテロ接合電界効果型の半導体装置であって、基板1上に順次積層して形成されたチャネル層3およびバリア層4と、バリア層4上に離間して形成されたソース電極5およびドレイン電極6とを備え、ソース電極5およびドレイン電極6のそれぞれの下方であり、かつ、バリア層4の表面からチャネル層3の少なくとも一部までの領域に対して、不純物拡散を行うことによって不純物拡散領域22を設け、バンドギャップを変化させることを特徴とする。

(もっと読む)

半導体素子用エピタキシャル基板、半導体素子、および、半導体素子用エピタキシャル基板の作製方法

【課題】オーミックコンタクト特性が優れており、かつ、良好なデバイス特性を有する半導体素子を実現することができるエピタキシャル基板を提供する。

【解決手段】下地基板の上に、少なくともAlとGaを含む、Inx1Aly1Gaz1N(x1+y1+z1=1)なる組成の第1のIII族窒化物からなるチャネル層を形成し、チャネル層の上に、少なくともInとAlを含む、Inx2Aly2Gaz2N(x2+y2+z2=1)なる組成の第2のIII族窒化物からなる障壁層を、表面近傍部におけるIn組成比が表面近傍部以外の部分におけるIn組成比よりも大きくなるように形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極からチャネル層までの距離のばらつきが低減されたHEMT半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、リセスエッチング工程後に酸化膜形成工程を行う。リセスエッチングを行った後に、HEMT構造基板の加熱や過酸化水素への浸漬によって、強制的に酸化膜6’’及び7’’を形成する。このような酸化膜6’’及び7’’は、面内均一性に優れ、かつ、ある厚さで安定するため、大気中に暴露してもそれ以上酸化は進まない。酸化膜6’’及び7’’は、例えば、濃度3%の過酸化水素水にHEMT構造基板を3分間浸漬させることや、120℃のホットプレート上で2分間HEMT構造基板を加熱させることにより形成することができる。

(もっと読む)

III族窒化物半導体積層ウェハ及びIII族窒化物半導体デバイス

【課題】Alを含むIII族窒化物系半導体からなるチャネル層を備え、二次元電子ガスの移動度を高め電流特性を向上させることが可能なIII族窒化物半導体デバイス、及び該III族窒化物半導体デバイスの作製に用いられるIII族窒化物半導体積層ウェハを提供する。

【解決手段】III族窒化物半導体積層ウェハ10は、AlXGa1−XN(0<X≦1)からなる基板27と、Alを含むIII族窒化物系半導体からなり基板27上に設けられた第1のAlGaN層13と、第1のAlGaN層13上に設けられ、第1のAlGaN層13よりバンドギャップが大きいIII族窒化物系半導体からなる第2のAlGaN層15とを備える。第1のAlGaN層13の(0002)面及び(10−12)面におけるX線ロッキングカーブの半値幅は、1000[arcsec]未満である。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、Au配線との密着性が強く、より高い熱的安定性を有するバリアメタル層を実現し、更なる特性向上、歩留まり向上を実現する。

【解決手段】半導体装置を、Al層8を含む電極9,10と、Au配線12と、Al層8とAu配線12との間に設けられ、Al層8の側から順に第1Ta層14、第1TaN層15、第1Pt層16を積層した構造を有するバリアメタル層11とを備えるものとする。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】 窒化物半導体表面の自然酸化や熱処理による表面劣化を防止し、良好なショットキー特性を有する半導体装置を提供する。

【解決手段】 基板101に、不純物を積極的に注入することなく形成されたGaN緩衝層102、GaN緩衝層102よりもバンドギャップが大きい第2の窒化物半導体を材料とするAlxGayIn1-x-yN障壁層103、AlxGayIn1-x-yN障壁層103の上面にあって、この上面にオーミックコンタクトするソース電極105、ドレイン電極107、ソース電極105、ドレイン電極107の間に設けられたゲート電極106を形成して半導体装置製造する。そして、ゲート電極106を、第2の窒化物半導体よりも小さなバンドギャップを有するn型不純物が積極的に注入された高濃度n型GaaIn1-aNゲート電極106a、ゲート電圧伝送用電極106bによって構成する。

(もっと読む)

電界効果トランジスタ

【課題】本発明の目的は、電子走行層内のキャリアが、移動度の小さいヘテロ界面近傍に集中し、電子移動度を高くすることができないという問題を解決し、さらに、不純物散乱により移動度が高められないという問題を解決する電界効果トランジスタを提供する。

【解決手段】本発明の電界効果トランジスタは、半導体基板上に、n型の不純物がドープされ且つ広い禁制帯幅を備えるワイドギャップの半導体からなる電子供給層と、上記電子供給層より狭い禁制帯幅を備えるナローギャップの半導体層からなる電子走行層とを設ける電界効果トランジスタであって、上記電子走行層は、不純物を含まない第1のノンドープ層、不純物を含むドープ層、不純物を含まない第2のノンドープ層の3層からなり、かつ上記電子走行層中の、不純物を含むドープ層のドーパント濃度は1×1016cm-3以上かつ1×1017cm-3未満であることを特徴とする。

(もっと読む)

半導体装置

【課題】耐圧が安定するとともにオン抵抗を低減することが可能な半導体装置を提供する。

【解決手段】半導体装置であるMOSFETは、導電型がn型であるSiCウェハと、SiCウェハの第1の主表面20Aを含むように形成された導電型がp型の複数のpボディ21と、平面的に見て複数のpボディ21のそれぞれに取り囲まれる領域内に形成された導電型がn型のn+ソース領域22とを備えている。pボディ21は、平面的に見て円形形状を有しており、n+ソース領域22は、平面的に見てpボディ21と同心に配置された円形形状を有している。そして、複数のpボディ21は、平面的に見て正六角形の各頂点に位置するように配置されている。

(もっと読む)

化合物半導体装置の製造方法

【課題】基板の付け替えに際して基板を適切に分離することができる化合物半導体装置の製造方法を提供する。

【解決手段】基板の上方に、第1のバンドギャップのAlxGa1-xN(0≦x<1)を含む第1の化合物半導体層を形成する。前記第1の化合物半導体層上に、前記第1のバンドギャップよりも広い第2のバンドギャップのAlyInzGa1-y-zN(0<y<1、0<y+z≦1)を含む第2の化合物半導体層を形成する。前記第2の化合物半導体層の上方に、化合物半導体積層構造を形成する。前記第1のバンドギャップと前記第2のバンドギャップとの間のエネルギを有する光を前記第1の化合物半導体層に照射しながら前記第1の化合物半導体層を除去して、前記基板を前記化合物半導体積層構造から分離する。

(もっと読む)

ダイヤモンド薄膜およびダイヤモンド電界効果トランジスター

【課題】本発明の目的は、従来技術のデバイスのドレイン電流値が実用的には少なすぎ、試料を昇温すると、ある温度以上でドレイン電流が劇的に減少し、元に戻らず、デバイスが劣化するという問題を解決するダイヤモンド電界効果トランジスターおよびダイヤモンド多層膜。

【解決手段】ダイヤモンド上に水素を含む第1の表面層があり、その上にソース電極、ゲート電極、ドレイン電極が順に並んでおり、ソース電極−ゲート電極間、およびゲート電極−ドレイン電極間の上記ダイヤモンド結晶の第1の表面層上に、フッ素を含む保護層があることを特徴とするダイヤモンド電界効果トランジスター。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

101 - 120 / 400

[ Back to top ]