Fターム[5F102HC21]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | 熱処理(アニール) (453)

Fターム[5F102HC21]の下位に属するFターム

局部的アニール(レーザ、電子線照射) (10)

レジスト、ガラスの軟化 (1)

合金化、シリサイド化 (42)

Fターム[5F102HC21]に分類される特許

21 - 40 / 400

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

半導体装置の製造方法

【課題】設計された形状およびサイズのゲート電極を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】本実施形態に係る半導体装置の製造方法は、半導体層12の表面上のうち、互いに離間した位置に、チタン層17a、18a、アルミニウム層17b、18b、ニッケル層17c、18c、金層17d、18dがこの順で積層した積層体17、18を形成し、これらを、アルミニウムの融点より高い温度で加熱して複数の金属体17´、18´を形成するするとともに、これらの複数の金属体17´、18´を半導体層12にオーミック接触させる。この後、複数の金属体17´、18´を薄膜化して複数の合金層13a、14aを形成し、合金層13a、14aを含むドレイン電極13およびソース電極14を形成する。次に、ドレイン電極13とソース電極14との間のレジスト層19に開口部20し、この開口部20内にゲート電極15を形成する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体層とオーミック電極とのコンタクト抵抗を低減できる窒化物半導体装置を提供する。

【解決手段】Si基板10上に形成されたアンドープGaN層1,アンドープAlGaN層2と、アンドープGaN層1,アンドープAlGaN層2上に形成されたTi/Al/TiNからなるオーミック電極(ソース電極11,ドレイン電極12)とを備える。上記オーミック電極中の酸素濃度を1×1016cm−3以上かつ1×1020cm−3以下とする。

(もっと読む)

GaN薄膜貼り合わせ基板およびその製造方法、ならびにGaN系高電子移動度トランジスタおよびその製造方法

【課題】バッファリーク電流およびゲートリーク電流が抑制された高性能のHEMTを提供する。

【解決手段】本GaN薄膜貼り合わせ基板の製造方法は、GaNバルク結晶10の主表面から0.1μm以上100μm以下の深さの面10iへの平均注入量が1×1014cm-2以上3×1017cm-2以下の水素イオン注入工程と、水素イオン注入されたGaNバルク結晶10の上記主表面へのGaNと化学組成が異なる異組成基板20の貼り合わせ工程と、GaNバルク結晶10の熱処理によりGaNバルク結晶10を水素イオンが注入された深さの面10iにおいて分離することによる異組成基板20上に貼り合わされたGaN薄膜10aの形成工程と、を含む。GaN系HEMTの製造方法は、上記GaN薄膜貼り合わせ基板1のGaN薄膜10a上への少なくとも1層のGaN系半導体層30の成長工程を含む。

(もっと読む)

半導体装置の製造方法

【課題】膜の形成によって生じる半導体基板の反りを緩和できる、半導体装置の製造方法を提供する。

【解決手段】SiC半導体基板10の主面上にイオン注入用マスク材18を形成する。マスク材は半導体基板とは異なる熱膨張係数を有する。レジスト膜20をマスクとしてドライエッチングにより複数の装置形成領域の間の領域上(ダイシングライン)14に切欠き部16aを有するマスク用膜16を形成する。イオン注入などの工程を経て半導体装置を形成後、ダイシングラインに沿って各装置形成領域に分離する。

(もっと読む)

半導体基板、電界効果トランジスタ、半導体基板の製造方法および電界効果トランジスタの製造方法

【課題】DWB法における貼り合わせ時にIII-V族化合物半導体層が受けるダメージを小さくするとともに、受けたダメージの影響および界面準位の影響を低く抑え、高いキャリアの移動度を有するIII-V族MISFETを提供する。

【解決手段】ベース基板102と第1絶縁体層104と半導体層106とを有し、ベース基板102、第1絶縁体層104および半導体層106が、ベース基板102、第1絶縁体層104、半導体層106の順に位置し、第1絶縁体層104が、アモルファス状金属酸化物またはアモルファス状金属窒化物からなり、半導体層が、第1結晶層108および第2結晶層110を含み、第1結晶層108および第2結晶層110が、ベース基板102の側から、第1結晶層108、第2結晶層110の順に位置し、第1結晶層108の電子親和力Ea1が、第2結晶層110の電子親和力Ea2より大きい半導体基板を提供する。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】電極材料が拡散するのを抑制し、特性の向上を実現する。

【解決手段】半導体装置を、ゲート電極3とゲート絶縁膜2との間、Al含有オーミック電極4、5とAu配線9との間、及び、ゲート電極3の下方及びAl含有オーミック電極4、5の上方、のいずれかに設けられ、第1TaN層6A、Ta層6B、第2TaN層6Cを順に積層した構造を有する電極材料拡散抑制層6を備えるものとする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】低コストでしきい値電圧のバラツキの少ないノーマリーオフ化されたHEMTを提供する。

【解決手段】基板10の上方に半導体層21〜24を形成する工程と、半導体層23〜24にフッ素成分を含むガスを用いたドライエッチングによりリセス51となる開口部を形成する工程と、半導体層を加熱することによりリセス51の側面及び底面に付着しているフッ素を半導体層22〜24に拡散させフッ素を含む領域を形成する工程と、リセス51の内面及び半導体層22〜24上に絶縁膜30を形成する工程と、リセス51が形成されている領域に絶縁膜30を介し電極41を形成する工程と、を有する。

(もっと読む)

へテロ接合電界効果型トランジスタ及びその製造方法

【課題】耐圧特性の低下やゲートリーク電流の増加を生じることなく、低抵抗で高速動作可能なヘテロ接合電界効果型トランジスタおよびその製造方法を提供する。

【解決手段】ヘテロ接合FETの製造方法に関し、(a)チャネル層3及びチャネル層3上に形成されたバリア層4を窒化物半導体層として準備する工程と、(b)窒化物半導体層上に不純物拡散源としてZnO膜9を形成する工程と、(c)ZnO膜9上のドレイン電極6及びソース電極5を形成すべき領域以外に酸化膜10を形成する工程と、(d)窒化物半導体層に対して熱処理を行い、酸化膜10が形成されていない領域の下部のチャネル層3及びバリア層4に選択的に、ZnO膜9からZn及びOを拡散させる工程とを備える。

(もっと読む)

トランジスタ装置及びトランジスタ装置製造方法

【課題】トラップの影響を低減し、過渡応答を改善するトランジスタ装置及びトランジスタ装置製造方法を提供する。

【解決手段】ソース電極5とゲート電極6との間のGaNチャネル2における一部に形成された、不純物濃度が高い領域である高不純物領域13を含み、高不純物領域13は、ゲート電極6とドレイン電極7との間より不純物濃度が高い。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】材料の熱膨張係数の差に起因する反り等を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された電子走行層2と、電子走行層2上方に形成された電子供給層3と、が設けられている。基板1の表面に、電子走行層2よりも熱膨張係数が小さい第1の領域1bと、電子走行層2よりも熱膨張係数が大きい第2の領域1aと、が混在する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリ・オフ動作に適したMIS型を採用するも、電流コラプス特性を大幅に向上させて、デバイス効率及び耐圧に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成されたゲート絶縁膜6と、ゲート電極7とを含み、ゲート電極7は、ゲート絶縁膜6上に形成されたゲート基部7aと、ゲート基部7a上に形成されたゲート傘部7bとを有しており、ゲート傘部7bの下面が化合物半導体積層構造2とショットキー接触する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】所望の不純物濃度と、高い結晶性とを有するドリフト層を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】バッファ層31は、基板30上に設けられ、不純物を含有する炭化珪素から作られ、1μmより大きく7μmより小さい厚さを有する。ドリフト層32は、バッファ層31上に設けられ、バッファ層31の不純物濃度よりも小さい不純物濃度を有する炭化珪素から作られている。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】HEMTの移動度の低下を抑制することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】高電子移動度トランジスタ構造層3を、気相成長法により成長温度600℃以上750℃以下、V/III比150以下の条件で成長し、バイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下、V/III比75以下の条件で成長し、さらにノンアロイ層18を、380℃以上450℃以下の成長温度で成長する。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

炭化ケイ素金属半導体電界効果トランジスタ及び炭化ケイ素の金属半導体電界効果トランジスタを製造する方法

【課題】深いレベルのドーパントがほとんど存在しない半絶縁性のSiC基板上にMESFETを形成することにより、バックゲート効果が減少された、SiCのMESFETを提供する。

【解決手段】半絶縁性の基板上10に選択的にドープされたP型の炭化珪素の層13、及びN型のエピタキシャル層14を積層し、背面ゲート効果を減少させる。また2つの凹部を有するゲート構造体も備える。これにより、出力コンダクタンスを1/3に減少することができ、また電力のゲインを3db増加することができる。クロム42をショットキーゲート接点として利用することもでき、酸化物−窒化物−酸化物(ONO)の保護層60を利用して、MESFET内の表面効果を減少させる。また、ソース及びドレインのオーム接点をn型チャネル層上に直接形成して、これにより、n+領域を製造する必要がなくなる。

(もっと読む)

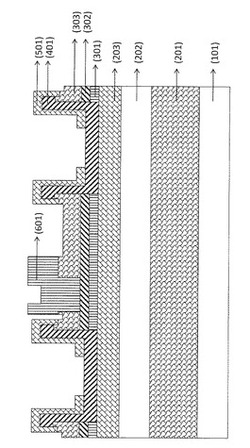

トランジスタ装置

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能

するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース、ドレ

イン、およびゲートを含む。第1のスペーサ層が、活性領域の上方でソースとゲートの間

にあり、第2のスペーサ層が、活性領域の上方でドレインとゲートの間にある。第1のス

ペーサ層上の第1のフィールドプレート、及び第2のスペーサ層上の第2のフィールドプ

レートが、ゲートに接続される。第3のスペーサ層が、第1のスペーサ層、第2のスペー

サ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、

第3のフィールドプレートが、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】Al原子を有するコンタクト電極が用いられる場合に、絶縁膜の絶縁信頼性を向上させることができる炭化珪素半導体装置の製造方法を提供する。

【解決手段】基板面12Bを有する炭化珪素基板10が準備される。基板面12Bの一部を覆うように絶縁膜15が形成される。絶縁膜15に接触するように基板面上にコンタクト電極16が形成される。コンタクト電極16はAl、TiおよびSi原子を含有する。コンタクト電極16は、Si原子およびTi原子の少なくともいずれかと、Al原子とを含有する合金から作られた合金膜50を含む。炭化珪素基板10とコンタクト電極16とがオーミックに接続されるようにコンタクト電極16がアニールされる。

(もっと読む)

多重フィールドプレートトランジスタ

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能

するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース、ドレ

イン、およびゲートを含む。第1のスペーサ層が、活性領域の上方でソースとゲートの間

にあり、第2のスペーサ層が、活性領域の上方でドレインとゲートの間にある。第1のス

ペーサ層上の第1のフィールドプレート、及び第2のスペーサ層上の第2のフィールドプ

レートが、ゲートに接続される。第3のスペーサ層が、第1のスペーサ層、第2のスペー

サ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、

第3のフィールドプレートが、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

【課題】埋込み部を形成する際のエッチングにより埋込みゲートが損傷をきたし、ゲート領域劣化が生じ得る。

【解決手段】ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。

(もっと読む)

21 - 40 / 400

[ Back to top ]