Fターム[5F102HC21]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | 熱処理(アニール) (453)

Fターム[5F102HC21]の下位に属するFターム

局部的アニール(レーザ、電子線照射) (10)

レジスト、ガラスの軟化 (1)

合金化、シリサイド化 (42)

Fターム[5F102HC21]に分類される特許

61 - 80 / 400

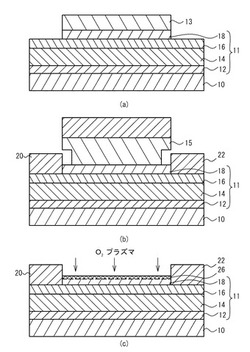

半導体装置の製造方法

【課題】信頼性を向上させることが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、窒化物半導体層11の表面に、パワー密度が0.2〜0.3W/cm2である酸素プラズマ処理を行う工程を有する半導体装置の製造方法である。本発明によれば、酸素プラズマ処理によって、窒化物半導体層11に導電層26が形成されることにより、イオンマイグレーション現象が抑制される。このため、半導体装置の信頼性が向上する。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】本発明は、ソース電極およびドレイン電極の熱耐久性を向上させて、かつ製造過程においてオーミック性に与える不安定要因を取り除き信頼性および量産性の高いGaN系HEMTを提供する。

【解決手段】GaN系HEMTは、基板と、窒化ガリウム系半導体と、融点が3000℃と高融点金属のタンタルと低融点金属のアルミニウムが前記窒化ガリウム系半導体上に積層されてなる前記ソースおよび前記ドレイン電極を備えている。前記ソース電極および前記ドレイン電極は、前記タンタルと前記アルミニウムの積層膜厚の比(前記アルミニウム膜厚/前記タンタル膜厚)を10以上にし、積層後のアニール処理温度が510℃以上、600℃未満で処理されて成る。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、剥離液の残渣を除去できる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板上に開口を有するレジストマスクを形成する工程と、該基板のうち該開口により露出した部分に所定の処理を施す工程と、アリールスルホン酸を含む剥離液を用いて該レジストマスクを剥離する工程と、リンス液を用いて該剥離液の残渣を除去する工程と、該基板上に膜を形成する工程と、を備える。そして、該リンス液の溶解度パラメータは12.98から23.43までのいずれかの値であることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】GaN系半導体層内に形成される電子トラップ濃度を低減する。

【解決手段】Si基板10上に接して形成されたAlNを主成分とする下地層12と、前記下地層12上に形成され、前記下地層12上に形成され、前記下地層12から圧縮応力を受ける第1バッファ層14と、前記第1バッファ層14上に形成された第2バッファ層16と、前記第2バッファ層16上に形成されたAlの組成比が0.1以下のGaN系半導体層18と、を具備し、前記第2バッファ層16における前記第1バッファ層14側の面の結晶軸長に対し前記第1バッファ層14と反対の面の結晶軸長が前記GaN系半導体層18に近く、前記第2バッファ層16の伝導帯底エネルギーが前記GaN系半導体層18より高い半導体装置。

(もっと読む)

窒化物半導体装置及び窒化物半導体装置の製造方法

【課題】シリコン基板上に優れた結晶性の窒化物半導体層が形成された窒化物半導体装置を提供する。

【解決手段】シリコン基板10と、シリコン基板10に接するとともにシリコン基板10上の一部分に形成された窒化シリコンからなる選択成長マスク層20とを備え、選択成長マスク層20が形成されていないシリコン基板10上に、当該シリコン基板10に接するように窒化物半導体層30が形成されている。

(もっと読む)

電界効果半導体装置の製造方法

【課題】半導体装置を構成する半導体層の表面上にAlOx層を安価に形成でき、且つAlOx層を厚膜化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板1と、前記半導体基板1上に形成された窒化物系化合物半導体層2、3、4と、前記窒化物系化合物半導体層2、3、4上に隣接して形成された酸化アルミニウム層7と、を備える半導体装置の製造方法であって、

前記窒化物系化合物半導体層2、3、4上に多結晶又は非晶質の窒化アルミニウム層6を形成する第1の工程と、前記多結晶又は非晶質の窒化アルミニウム層6を熱酸化して前記酸化アルミニウム層7を得る第2の工程と、を備えることを特徴とする半導体装置の製造方法。

(もっと読む)

炭化珪素トランジスタ装置の製造方法

【課題】微細化と、オン特性を改善する、炭化珪素トランジスタ装置の製造方法の提供。

【解決手段】高濃度n型炭化珪素基板2上に、低濃度n型ドリフト層3と高濃度p型層10をエピタキシャル成長する工程と、高濃度p型層10の一部を除去離間した複数の高濃度p型ゲート領域4を形成する工程と、互いに隣り合った高濃度p型ゲート領域4の間に位置するチャネル領域7、高濃度p型ゲート領域4及びゲート電極領域10の全面を覆う低濃度n型ドリフト層3よりも低い不純物濃度の低濃度n型領域11をエピタキシャル成長する工程と、低濃度n型領域11の一部を除去する工程と、低濃度n型領域11の表面にイオン注入し高濃度n型ソース領域5を形成する工程と、高濃度n型ソース領域5上にソース電極6を、高濃度n型炭化珪素基板2の裏面にドレイン電極1を、ゲート電極領域10にゲート電極8を形成する工程を含む炭化珪素トランジスタ装置の製造方法。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】リフトオフ法を用いずに、簡易な手法で化合物半導体装置のゲート電極、ソース電極、及びドレイン電極を各種パターンに欠陥を生ぜしめることなく形成する。

【解決手段】AlGaN/GaN・HEMTを製造する際に、化合物半導体層上に保護絶縁膜8を形成し、保護絶縁膜8に開口を形成し、開口を埋め込む導電材料を保護絶縁膜8上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてゲート電極15(又はソース電極45及びドレイン46)を形成し、その後、保護絶縁膜8上に保護絶縁膜16を形成し、保護絶縁膜8,16に開口を形成し、開口を埋め込む導電材料を保護絶縁膜16上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてソース電極22及びドレイン23(又はゲート電極53)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において低抵抗なオーミック性を有し、酸・アルカリによる腐食に対し高い耐性を持つ電極を得ることを目的とする。

【解決手段】本発明に係る第1の半導体装置は、窒化物半導体層1と、窒化物半導体層上に設けられた電極とを備え、窒化物半導体層1は電極下に、それ以外の部分よりも高濃度にn型不純物を含む高濃度不純物領域2を備え、電極は、窒化物半導体層1上に設けられた第一金属層3と、第一金属層3上に設けられた第二金属層4と、第二金属層4上に設けられた第三金属層5と、を備え、第一金属層3は第二金属層4よりも窒化物半導体層1との高い密着性を有する金属を含み、第三金属層5は水素よりもイオン化傾向の小さい金属を含む。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】室温(300K)以上において正孔濃度が1.0×1015cm‐3以上で、かつ、ドーパント原子濃度が1.0×1021cm‐3以下である実用的なp型ダイヤモンド半導体デバイスとその製造方法を提供すること。

【解決手段】単結晶ダイヤモンド基板1−1の上に形成された単結晶ダイヤモンド薄膜1−2の中には、二次元の正孔または電子チャンネル1−3が形成される。基板1−1の面方位と基板1−1の結晶軸「001」方向との成す角度をαs、ダイヤモンド薄膜1−2の面方位と単結晶ダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαd、チャンネル1−3の面方位とダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαcとする。単結晶ダイヤモンド薄膜1−2の表面上には、ソース電極1−4、ゲート電極1−5、ドレイン電極1−6が形成される。

(もっと読む)

窒化物半導体及び窒化物半導体素子

【課題】リーク電流が抑制された窒化物半導体、及び該窒化物半導体を備えた半導体素子を提供する。

【解決手段】Al原子,Ga原子及びIn原子から選択される1以上の金属原子と窒素原子とを少なくとも含むと共に、結晶面に対して垂直な転位線を持つらせん転位を有し、前記らせん転位の転位芯に相当する領域に位置された前記金属原子または窒素原子のうちの少なくとも一部が炭素原子で置換されている窒化物半導体である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体基板上の金属電極と半導体基板の界面に、現像残渣のない半導体装置を提供すること。

【解決手段】半導体基板上に、金属電極が設けられた半導体装置であって、金属電極は、半導体基板の上面視において、細線部と、細線部の電極の長手方向の両端に太線部と、細線部から太線部へ向けて線幅が漸増する線幅漸増部とからなり、細線部の側面と線幅漸増部の側面の境界領域に、曲率を有す円弧が付けられた形状であることを特徴とする半導体装置。

(もっと読む)

III族窒化物半導体素子、III族窒化物半導体素子の製造方法、および電子装置

【課題】 アクセス抵抗およびオン抵抗が低いIII族窒化物半導体素子、III族窒化物半導体素子の製造方法、および電子装置を提供する。

【解決手段】

障壁層902は、チャネル層901上方にヘテロ接合され、

チャネル層901の上部の一部およびその上方の障壁層902が除去されて凹部が形成され、

チャネル層901および障壁層902の一部にn型導電層領域904が形成され、

n型導電層領域904は、前記凹部の表面を含み、

n型導電層領域904の深さTimpが、n型導電層領域904表面の各部から前記表面と垂直方向の測定値で15nm以上であり、

オーミック電極906および907は、前記凹部の表面を介して前記n型導電層領域にオーミック接触していることを特徴とする、III族窒化物半導体素子。

(もっと読む)

電界効果トランジスタ

【課題】スイッチング速度を向上でき、動作不良品を低減できる、横型の電界効果トランジスタを提供する。

【解決手段】ゲート配線43は、基部44と、基部44から突出する複数の指状部45と、隣接する指状部45の先端部46を接続する接続部47と、を有する。ゲート配線43の指状部45は、ソース配線23の指状部25とドレイン配線33の指状部35と、の間に配置されている。ゲート配線43の基部44は、ソース配線23の基部24とドレイン配線33の指状部35との間に配置され、かつ、ソース配線23の指状部25との間に絶縁膜を介在させて指状部25と交差している。

(もっと読む)

半導体装置およびその製造方法

【課題】界面準位を低減しつつ、電荷トラップに起因するヒステリシスを抑制できる半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置200は、GaNを含む半導体層101を表面の少なくとも一部に有する基板(半導体基板100)と、半導体層101と接するように半導体基板100上に設けられており、窒素を含まず、Alを含む酸化金属層からなる第1のゲート絶縁層(Al2O3膜114)と、Al2O3膜114上に設けられており、SiおよびOを含む第2のゲート絶縁層(SiO2膜116)と、SiO2膜116上に設けられたゲート電極118と、を備え、ゲート電極118の下面は、SiO2膜116に接しており、Al2O3膜114の膜厚は、SiO2膜116の膜厚より薄い。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのショットキーダイオード10は、半導体からなる基板11と、基板11上に形成されたn型層12とを備えている。n型層12は基板11側の表面である第1の面12Aとは反対側の表面である第2の面12Bから第1の面12Aに向けて延びるように形成された溝13を有している。溝13の底部である底壁13Aに接触する位置には絶縁体としての酸化物層14が配置されており、かつ溝13の側壁13Bに接触するようにn型層12とショットキー接触可能な金属膜15が溝13を埋めるように形成されている。さらに、n型層12の第2の面12Bに接触するようにアノード電極16が配置されている。

(もっと読む)

電子回路装置

【課題】ノーマリオフ型の炭化珪素接合FETはゲートの特性が、使い勝手が悪いという問題がある。これは、ノーマリオフを実現するためにゲート電圧が0Vでオフしていなければならず、かつ、ゲート・ソース間のpn接合に電流が流れないようにオン状態としてはゲート電圧を2.5V程度に抑える必要があるため、実質的にゲート電圧を0Vから2.5Vの間で制御しなければならないためである。従って、閾値電圧からオン状態のゲート電圧までが1Vから2V程度しかなく、ドレイン電流がゲート電圧の変化に非常に敏感であるため、ゲートの制御が難しい。

【解決手段】本願発明は、ノーマリオフ型の炭化珪素接合FETのゲートに、接合FETのゲート容量と同等か少し小さな容量を持つ素子を接続したものである。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系HEMT及びMIMキャパシタを同一基板上に設ける場合でも小型化することができる半導体装置及びその製造方法を提供する。

【解決手段】基板1の表面上に下部電極11を形成し、下部電極11上に誘電体膜12を形成し、誘電体膜12上に基板1の表面に接する上部電極14aを形成する。また、基板1の裏面から基板1をエッチングすることにより、上部電極14aの基板1の表面に接する部分に達するビアホール1aを基板1に形成し、基板1の裏面上にビアホール1aを介して上部電極14aに接するビア配線36を形成する。

(もっと読む)

半導体ウェハ及び高周波電子デバイス用半導体ウェハ

【課題】シリコン基板などの支持基板上に窒化物半導体膜を形成し、その窒化物半導体膜上にエピタキシャル層を形成した半導体ウェハを提供する。

【解決手段】支持基板と、上記支持基板の表面に設けられた窒化物半導体薄膜と、上記窒化物半導体薄膜上に気相成長され形成された窒化物半導体エピタキシャル層と、を備える半導体ウェハにおいて、上記窒化物半導体薄膜は、GaN基板に設けられたイオン注入層を境として上記GaN基板から剥離されたGaN薄膜であって、上記GaN薄膜は(000−1)窒素面側を上記支持基板側に有し、(0001)Ga面側を上記窒化物半導体エピタキシャル層の気相成長面として有する。

(もっと読む)

電子デバイス及びオーミック電極形成方法

【課題】製造工程において高温で短時間のアニールを可能にすることにより、イオン注入の工程が不要なAlxGa1−xN/AlyGa1−yNヘテロ接合のオーミック電極を備える電子デバイスを提供する。

【解決手段】

電子デバイスは、ワイドバンドギャップ化合物半導体層と、前記ワイドバンドギャップ化合物半導体層上に形成されるオーミック電極とを含む電子デバイスであって、前記ワイドバンドギャップ化合物半導体層は、IniAljGakN(i+j+k=1,0≦i≦1,0<j≦1,0≦k<1)からなる化合物半導体バリア層とAlyGa1−yN(0<y≦1)からなる化合物半導体チャネル層からなり、前記オーミック電極は、前記化合物半導体バリア層上に密着層が積層され、前記密着層上にオーミック層が積層されて形成された電極であり、前記密着層はZrからなるようにする。

(もっと読む)

61 - 80 / 400

[ Back to top ]