Fターム[5F110BB12]の内容

Fターム[5F110BB12]に分類される特許

101 - 120 / 451

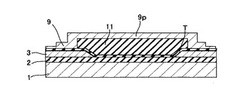

半導体装置及びその製造方法

【課題】Cdsubの低減を通じて、出力容量Cossの低減に寄与する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板と半導体基板上に絶縁膜を介して形成された第1導電型の半導体層とを有するSOI基板と、第1導電型の半導体層からなる活性領域内に、第2導電型の半導体層からなるウェルを形成するとともに、ウェル内および第1導電型の活性領域内に、第1導電型の半導体層からなるソース・ドレイン領域を形成した横型MOSFETにおいて、活性領域のうち、ドレイン領域にコンタクトするように形成されるドレインパッド形成領域9p下の少なくとも一部は、SOI基板の絶縁膜に到達するように形成された絶縁性領域11で構成される。

(もっと読む)

横型の絶縁ゲート型バイポーラトランジスタ

【課題】オン電圧の低減と、破壊耐量確保、高速スイッチングを同時に実現できる横型IGBTを提供する。

【解決手段】n型バリア層15を形成することでエミッタ側のキャリア濃度を高くしてオン電圧の低減を図りつつ、n型バリア層15を隣り合うエミッタ間に形成しないようにすることで、ターンオフ時間の改善を図る。また、このような構造により、スイッチング時の破壊耐量の向上も図ることも可能となる。したがって、オン電圧の低減と、破壊耐量確保、高速スイッチングを同時に実現できる横型IGBTとすることが可能となる。

(もっと読む)

インバータ回路

【課題】1チップ化しつつ、高温化による誤動作を抑制し、かつ、半導体パワー素子に流れる電流を低減し、チップサイズの増大を抑制することができるインバータ回路を提供する。

【解決手段】コンバータ電源回路部2の電源供給ライン8中、例えば、IPD20におけるパワーMOSFET220のハイサイド側に電流制限抵抗240を備える。この電流制限抵抗240によって電源供給ライン8に流れる電流の電流値を制限することができるため、パワーMOSFET220での発熱を抑制することが可能となる。したがって、インバータ回路1内の素子の定格温度を超えることを防止することが可能となり、誤動作が生じることを抑制できる。これにより、インバータ回路1の信頼性の向上を図ることが可能となる。また、パワーMOSFET220として必要な能力を軽減することが可能となり、大面積な素子としなくても済む。

(もっと読む)

オフセット構造の薄膜トランジスタ

【課題】オフセット構造の薄膜トランジスタを提供する。

【解決手段】ゲート電極と、それぞれゲート電極と一部重畳する第1活性領域及び第2活性領域を備える活性層と、ゲート電極と活性層との間のゲート絶縁膜と、第1活性領域とそれぞれ電気的に連結された第1ソース/ドレイン電極及び第2ソース/ドレイン電極、第2活性領域とそれぞれ電気的に連結された第3ソース/ドレイン電極及び第4ソース/ドレイン電極を備えるソース/ドレイン電極層と、を備えるが、第1ソース/ドレイン電極ないし第4ソース/ドレイン電極のいずれか二つは、ゲート電極と一部重畳し、他の二つは、ゲート電極とオフセットされており、ソース/ドレイン電極の配置は、ソース/ドレイン電極層の中心に対称である薄膜トランジスタである。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離されたSOI基板にIGBTとその制御回路等が形成される半導体装置において、IGBTの高耐圧化及びターンオフ特性の改善等が必要になる。

【解決手段】ダミー半導体基板16にN型エピタキシャル層8を形成し、N型エピタキシャル層8にトレンチ30を形成し、トレンチ30側壁及びN型エピタキシャル層8表面にN型バッファ層7、次にP型埋め込みコレクタ層6を形成し、トレンチ30底面及びP+型埋め込みコレクタ層6上を埋め込み絶縁膜5で被覆する。埋め込み絶縁膜5上をポリシリコン膜3で被覆し、該ポリシリコン膜3と絶縁膜2を介してP型半導体基板1を貼り合わせた後、ダミー半導体基板16を除去し、略同一平面状に露出するトレンチ30底面の埋め込み絶縁膜5、P+型埋め込みコレクタ層6、N型バッファ層7、N型ドリフト層8a等を具備するSOI基板を形成する。該SOI基板にIGBT等を形成する。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38の上部に、ドレイン電極36側及びソース電極34側に庇状に突き出したフィールドプレート40が形成され、基板32の表面層とフィールドプレート40との間に誘電体膜46が形成され、誘電体膜46は、フィールドプレート40のドレイン電極36側及びソース電極34側の終端面と面一状態となるように切れ込み、ドレイン電極36側の下端からドレイン電極36に接続するようにドレイン電極36に向かって延びており、且つ、ソース電極34側の下端からソース電極34に接続するようにソース電極34に向かって延びている。

(もっと読む)

成膜方法及び半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供することを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でスパッタリングを行う。

(もっと読む)

誘電体分離型半導体装置の製造方法

【課題】耐圧を向上させることができ、かつ半導体基板が反るのを防ぐことができる誘電体分離型半導体装置の製造方法を得る。

【解決手段】p型シリコン基板10の主面の領域42に複数のトレンチ溝44を形成する。p型シリコン基板10の表面を酸化して、p型シリコン基板10の主面に誘電体層12を形成し、領域42に厚膜誘電体層38を形成する。p型シリコン基板10に誘電体層12を介してn−型半導体層14を貼り合せる。厚膜誘電体層38の上方においてn−型半導体層14の一部にn+型半導体領域18を形成する。n+型半導体領域18から離間してn+型半導体領域18を取り囲むようにn−型半導体層14の一部にp+型半導体領域20を形成する。n+型半導体領域18に接続された主電極26を形成する。p+型半導体領域20に接続された主電極28を形成する。p型シリコン基板10の裏面に裏面電極32を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを目的の一とする。

【解決手段】酸化物半導体層を有するトランジスタにおいて、ゲート絶縁層を酸化ガリウム膜として、酸化物半導体層と接する構成とする。また、酸化物半導体層の上下を挟むように酸化ガリウム膜を配置することによって信頼性の向上を実現する。また、ゲート絶縁層は、酸化ガリウム膜と酸化ハフニウム膜の積層構造としてもよい。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】酸化物半導体膜を含むトランジスタにおいて、酸化物半導体膜の上面部及び下面部に、酸化物半導体膜と同種の成分でなる金属酸化物膜を積層され、さらに、金属酸化物膜において酸化物半導体膜と接する面と対向する面には、金属酸化物膜及び酸化物半導体膜とは異なる成分でなる絶縁膜が接して設けられているトランジスタを提供する。また、トランジスタの活性層に用いる酸化物半導体膜は、熱処理によって、水素、水分、水酸基または水素化物などの不純物を酸化物半導体より排除し、かつ不純物の排除工程によって同時に減少してしまう酸化物半導体を構成する主成分材料である酸素を供給することによって、高純度化及び電気的にi型(真性)化されたものである。

(もっと読む)

半導体装置

【課題】特性が良好であって、かつ大電力用途向けの半導体装置を提供することを課題とする。

【解決手段】半導体装置、具体的には縦型トランジスタのゲート電極層の一部を、ソース電極層、ドレイン電極層およびチャネル領域となる半導体層の一部と重畳する構造にすることである。つまり、ソース電極層と、ソース電極層に接した酸化物半導体層と、酸化物半導体層に接したドレイン電極層と、一部がソース電極層、ドレイン電極層および酸化物半導体層と重畳したゲート電極層と、ゲート電極層の全ての面に接するゲート絶縁層と、を有する半導体装置を提供することである。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、従来の製造方法と比較し、同一ウエハまたは製品上において複数のデバイス耐圧帯と良好なオン抵抗をもったLDMOSを備えた半導体装置およびその製造方法を提供することを目的とするものである。

【解決手段】 第1電界緩和用酸化膜24と第2電界緩和用酸化膜25と素子分離用LOCOS酸化膜17の膜厚を別々に最適化することにより、同一ウエハにおいて複数のデバイス耐圧と良好なオン抵抗を実現する。

(もっと読む)

半導体デバイスおよび方法

アルミニウムドープゲートを備えるプログラマブルIII−窒化物トランジスタ

【課題】アルミニウムドープゲートを有するプログラマブルIII−窒化物トランジスタを提供する。

【解決手段】第1のIII−窒化物材料104と第2のIII−窒化物材料106との界面に形成される2次元電子ガスを有する導電チャネルを含むIII−窒化物ヘテロ接合デバイスにおいて、ゲート接点140の下に形成されるゲート絶縁層112が導電チャネルの上方に配置され、接点絶縁層112は界面における2次元電子ガスの形成を変更する。接点絶縁層112はAlSiN又はアルミニウムがドープされたSiNとすることができる。接点絶縁層112はIII−窒化物ヘテロ接合デバイス160の閾値電圧をプログラミングしてデバイスをエンハンストモードデバイスにする。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの微細化を達成し、電界緩和がなされた、酸化物半導体を用いた半導体装置を提供することを課題の一とする。

【解決手段】ゲート電極の線幅を微細化し、ソース電極層とドレイン電極層の間隔を短縮する。ゲート電極をマスクとして自己整合的に希ガスを添加し、チャネル形成領域に接する低抵抗領域を酸化物半導体層に設けることができるため、ゲート電極の幅、即ちゲート配線の線幅を小さく加工しても位置精度よく低抵抗領域を設けることができ、トランジスタの微細化を実現できる。

(もっと読む)

半導体装置

【課題】ゲート構造を微細化してON抵抗を低減しても、アバランシェ耐量を高く維持できる半導体装置を提供する。

【解決手段】ドリフト領域2と、ベース領域3と、ベース領域3を挟んでドリフト領域2に対向して設けられたソース電極12と、ドリフト領域2とベース領域3とにゲート絶縁膜を介して接するトレンチ構造の複数のゲート電極6と、2つのゲート電極6の間において、ドリフト領域2とベース領域3との境界に沿って設けられ、ベース領域3に接する長さがゲート電極6よりも短いトレンチ構造のゲート電極7と、を備え、ソース電極12は2つのゲート電極6の間において、ソース電極12からゲート電極7に向かう方向に設けられたトレンチ9bの中に、ゲート電極7に近接した位置まで延在し、ゲート電極6のソース電極側の端とゲート電極7のソース電極側の端との間において、トレンチ9bの内壁面に露出したベース領域3に接していること。

(もっと読む)

半導体装置およびその製造方法

【課題】 LDMOSトランジスタにおいて、オン抵抗とのトレードオフ関係で最適化されたオフ耐圧を低下させることなく、チャネル長を短くすることによって飽和電流を増加させる。

【解決手段】 チャネルとなる低濃度ボディ領域10と素子分離膜4の間かつゲート酸化膜8の直下に選択的に低濃度ボディ領域10と逆の極性で濃度が高いショートチャネル領域12を設け、ボディ領域10のゲート酸化膜8直下部分のみを高濃度ソース領域7側に後退させた形状を実現する。

(もっと読む)

半導体装置の製造方法

【課題】オン抵抗の低いパワーMOS等の半導体装置を提供する。

【解決手段】ゲート酸化膜を介しゲート電極22を形成するゲート電極形成工程と、ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する工程と、第1の開口部において露出している表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、ゲート電極間よりも狭い第2の開口部31を有する層間絶縁膜30を形成する層間絶縁膜形成工程と、第2の開口部よりも広い第3の開口部を有する第2のレジストパターン32を形成する工程と、第3の開口部33において露出している表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、を有し、第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする。

(もっと読む)

半導体トランジスタ

【課題】GaN系半導体/ゲート絶縁膜の界面特性、及び、ゲート絶縁膜の膜質が共に良好である半導体トランジスタを提供する。

【解決手段】半導体トランジスタ11は、GaN系の半導体から成る活性層3と、活性層3上に形成されたゲート絶縁膜とを備える。ゲート絶縁膜は、活性層3上に形成され、Al2O3,HfO2,ZrO2,La2O3,Y2O3から成る群から選択された1つ以上の化合物を含む第1の絶縁膜6と、第1の絶縁膜6上に形成され、SiO2から成る第2の絶縁膜7とを有する。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】ダイヤモンド薄膜内に存在する結晶欠陥、不純物等を減少させ、高品質なダイヤモンド薄膜を作製可能なダイヤモンド薄膜作製方法を提供すること。

【解決手段】ダイヤモンドが安定な高圧力下でアニールを行う。これにより、結晶中に含まれる格子欠陥等が回復、除去され、ダイヤモンド結晶薄膜を高品質化する事ができる。「(ダイヤモンドが)安定な、安定に」とは、ダイヤモンドがグラファイト化せずにダイヤモンドの状態を保つ状態を指す。ダイヤモンドが安定にアニール出来る領域内でアニールを行う温度(アニール温度、とも呼ぶ)Tおよびアニールを行う圧力(アニール圧力、とも呼ぶ)Pが決定される。この領域は、図21に示される、P>0.71+0.0027TまたはP=0.71+0.0027Tを満たし、なおかつP≧1.5GPaの領域である。このような領域は、図21中の斜線部分である。

(もっと読む)

101 - 120 / 451

[ Back to top ]