Fターム[5F110BB12]の内容

Fターム[5F110BB12]に分類される特許

21 - 40 / 451

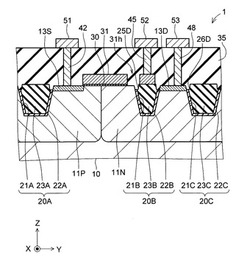

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

横型の絶縁ゲート型バイポーラトランジスタを備えた半導体装置

【課題】オン電圧の低減と、破壊耐量確保、高速スイッチングを同時に実現できる横型IGBTを提供する。

【解決手段】エミッタ側にn型バリア層15を形成することで、ホールのバリアとして機能させ、コレクタ側から注入されたホールがエミッタ側のチャネルpウェル層6に流れ出てホール濃度が低下することを防止する。これにより、エミッタ近傍のn-型ドリフト層2内のキャリア濃度を上げることが可能となり、オン電圧の低減が可能となる。また、コレクタ側において、コレクタ電極12のうちp+型層4aと接触している部分をオーミック接触、p型層4bと接触している部分をショットキー接触とする。このショットキー接触とされた部分において、コレクタ側からのホールの注入が抑制され、蓄積キャリアを低減して、寄生バイポーラトランジスタがオンし難くなるようにできる。よって、低オン電圧を維持しながらスイッチング耐圧を確保することが可能となる。

(もっと読む)

半導体装置

【課題】耐圧の低下を抑制しつつ電流駆動能力の向上と小型化とを実現できる半導体装置を提供する。

【解決手段】半導体装置1は、SOI基板の半導体層の上面に沿って形成されたゲート電極31と、ソース拡散領域181〜18Nと、電荷収集領域191〜19N+1と、ドレイン拡散領域16と、電界緩和領域17とを備える。ソース拡散領域181〜18Nと電荷収集領域191〜19N+1とは、Y軸方向に沿って交互に配列されている。ソース拡散領域181〜18Nの各々の幅をWeffとし、ゲート電極31の長さをLgとし、ゲート電極31とドレイン拡散領域16との互いに対向する端部間の距離をLdriftとするとき、Weff/2≦Lg+Ldrift/2、との関係式が成立する。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワー絶縁ゲート型電界効果トランジスタ(パワーMISFET)を提供する。

【解決手段】半導体層103を挟んでゲート電極105とドレイン電極102を形成し、ゲート電極105の側面に半導体層109を形成し、ゲート電極105の頂上部と重なる部分で、半導体層109とソース電極112が接する構造を有する。このようなパワーMISFETのドレイン電極とソース電極の間に500V以上の電源と負荷を直列に接続し、ゲート電極105に制御用の信号を入力して使用する。

(もっと読む)

トランジスタ

【課題】新たな半導体材料を用いたトランジスタを提供する。

【解決手段】水素濃度が1×1016cm−3以下の領域を有する酸化物半導体層又はキャリア密度が1×1014cm−3未満の領域を有する酸化物半導体層を有し、酸化物半導体層の膜厚は、酸化物半導体層のドナー密度に基づく空乏層の広がり得る最大幅よりも薄いトランジスタである。

(もっと読む)

有機半導体素子用電極及びその製造方法

【課題】電界効果移動度が十分な有機半導体素子を安価に製造することができる有機半導体素子用電極、及びかかる有機半導体素子用電極を有する有機半導体素子を提供する。

【解決手段】基板1上に、酸化グラフェンナノリボンを含有するインクをインクジェット法により塗布し、前記インクが含有する前記酸化グラフェンナノリボンを還元して、グラフェンナノリボンを含有する薄膜とすることにより形成される有機半導体素子用電極5、6。

(もっと読む)

有機半導体素子用電極及びその製造方法

【課題】電界効果移動度が高い有機半導体素子の製造に有用な有機半導体素子用電極、及び、該有機半導体素子用電極を有する有機半導体素子を安価に提供する。

【解決手段】基板1、ゲート電極4、ゲート絶縁膜3、有機半導体層2、ソース電極5及びドレイン電極6を有する有機半導体素子100であって、前記ゲート絶縁膜上に設けられた自己組織化単分子膜のパターン領域と、前記自己組織化単分子膜のパターン領域外である電極形成領域20に設けられたグラフェンナノリボンを含有する薄膜からなる前記ソース電極及びドレイン電極とを有する、有機半導体素子。

(もっと読む)

化合物半導体の形成方法

【課題】高電圧駆動素子の為にSiCやGaNの基板の簡素化が重要な課題となっている。

Si基板上のシリコン酸化膜の上に単結晶のSiC膜やGaN膜に形成したMOSFETなどの素子をアニールする手法を開示する。

【解決手段】光学ランプからの光をレンズで集光する手段、或いはレーザ光など高温度を発生させる手段によりSiCなど化合物半導体の表層部はSi基板の融点を越えるような高温度として、Si基板部はその融点よりも十分低い温度となるような冷却部を設けてSi基板を保持するステージを設けたことを特徴とするアニーリング装置。

(もっと読む)

誘電体分離基板および半導体装置

【課題】深い不純物拡散層の形成が容易な誘電体分離基板および半導体装置を提供する。

【解決手段】誘電体分離基板10では、半導体基板11に第1の厚さt1を有する絶縁膜12が設けられている。絶縁膜12上に第2の厚さt2を有する第1導電型の半導体層13が設けられている。半導体層13の下部に絶縁膜12に接して第2導電型の不純物拡散層14が部分的に設けられている。

(もっと読む)

窒化物系半導体装置

【課題】ゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、ノーマリオフの双方向動作が可能な窒化物系半導体装置を提供する。

【解決手段】窒化物系半導体素子10は、第1MOSFET部30及び第2MOSFET部31を備えており、第1ゲート電極26と第2ゲート電極27との間に設けられた第1SBD金属電極28及び第2SBD金属電極29がAlGaN層20とショットキー接合されている。第1SBD金属電極28と第1電極24とが接続されており、電気的に短絡していると共に、第2SBD金属電極29と第2電極25とが接続されており、電気的に短絡している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

半導体装置およびその作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを有する半導体装置を提供する。

【解決手段】加熱処理により酸素を放出する絶縁体基板と、該絶縁体基板上に設けられた酸化物半導体膜と、を有し、該酸化物半導体膜にチャネルが形成されるトランジスタを有する半導体装置である。加熱処理により酸素を放出する絶縁体基板は、絶縁体基板の少なくとも酸化物半導体膜が設けられる側に、酸素イオン注入を行うことで作製することができる。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】基板と、基板上に形成されたHEMT積層物と、を備え、HEMT積層物は、2DEGを含む化合物半導体層と、化合物半導体層より分極率の大きい上部化合物半導体層と、上部化合物半導体層上に備えられたソース電極、ドレイン電極及びゲートと、を備え、基板は、シリコン基板より誘電率及び熱伝導度の高い窒化物基板であるHEMT。該基板は、シリコン基板より誘電率及び熱伝導度の高い絶縁層、この絶縁層に蒸着された金属層及びこの金属層に付着されたプレートを備える。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

半導体装置

【課題】回路誤動作を防止できる半導体装置を提供する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。また、外部電源61に接続されるラインを電源供給ラインとガードリング端子固定ラインとを分岐し、電源供給ラインの電流が流れないガードリング端子固定ラインに抵抗63を備えることで、バイパスコンデンサ64をディスクリート部品としなくても良い回路構成とする。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と該酸化物半導体膜と接する下地となる膜との界面の電子状態が良好なトランジスタ。

【解決手段】下地となる膜は酸化物半導体膜と同様の原子配列を有し、下地となる膜と酸化物半導体膜とが接している面において、面内の下地膜の最隣接原子間距離と酸化物半導体の格子定数の差を、下地となる膜の同面内における最隣接原子間距離で除した値は0.15以下、好ましくは0.12以下、さらに好ましくは0.10以下、さらに好ましくは0.08以下とする。例えば、立方晶系の結晶構造を有し(111)面に配向する安定化ジルコニアを含む下地となる膜上に酸化物半導体膜を成膜することで、下地となる膜の直上においても結晶化度の高い結晶領域を有する酸化物半導体膜が得られる。

(もっと読む)

半導体装置の作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し

、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形

成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことによ

り、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成

し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面

に水素を供給する。

(もっと読む)

半導体装置

【課題】高耐圧を確保でき、かつ大電流を流すことができるMOSトランジスタを備えた半導体装置を提供する。

【解決手段】P型拡散層15に起因してN型拡散層13に第1空乏層23が形成される。ゲート電極19にゲート電圧が印加されていない状態では、P型ポリシリコンからなるゲート電極19及びN型拡散層13の仕事関数差に起因してN型拡散層13に第2空乏層25が形成される。空乏層23,25によってソースコンタクト用拡散層9とドレインコンタクト用拡散層11が電気的に遮断される。ゲート電極19にゲート電圧が印加された状態では、第2空乏層25が消滅又は縮小することによってソースコンタクト用拡散層9とドレインコンタクト用拡散層11がN型拡散層13を介して電気的に導通する。

(もっと読む)

半導体装置

【課題】パワーデバイスである大電力用途向けの電界効果トランジスタにおいて、特性の良好な電界効果トランジスタを提供する。

【解決手段】第1のゲート電極と、第1のゲート電極を覆うゲート絶縁層と、第1のゲート電極と重畳して、且つゲート絶縁層と接する酸化物半導体層と、酸化物半導体層の端部を覆うキャリア密度の高い酸化物半導体層と、キャリア密度の高い酸化物半導体層と接するソース電極及びドレイン電極と、ソース電極、ドレイン電極及び酸化物半導体層を覆う絶縁層と、絶縁層と接し、且つ、ソース電極及びドレイン電極の間に設けられる第2のゲート電極と、を有し、キャリア密度の高い酸化物半導体層は、酸化物半導体層を介して対向し、且つ酸化物半導体層の端部の上面、下面、及び側面のそれぞれ一部、並びにゲート絶縁層の上面一部と接する半導体装置である。

(もっと読む)

21 - 40 / 451

[ Back to top ]