Fターム[5F110CC01]の内容

Fターム[5F110CC01]の下位に属するFターム

順コプレナドープ (4,463)

Fターム[5F110CC01]に分類される特許

41 - 60 / 2,099

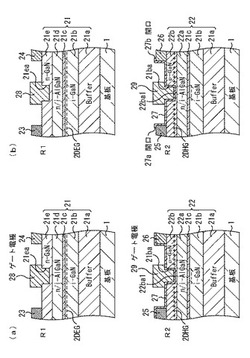

半導体装置及びその製造方法

【課題】オン時における電流の迅速な立ち上がりを実現し、複雑な工程を経ることなく、n型HEMTとモノリシックにインバータを構成可能な半導体装置を得る。

【解決手段】第1の極性の電荷(ホール)供給層22aと、電荷供給層22aの上方に形成されており、凹部22baを有する第2の極性の電荷(ホール)走行層22bと、電荷走行層22bの上方で凹部22baに形成されたゲート電極29とを含むp型GaNトランジスタを備える。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

電磁波剥離性フレキシブルデバイス用基板およびそれを用いた電子素子の製造方法

【課題】本発明は、安定的に電子素子部を形成可能な電磁波剥離性フレキシブルデバイス用基板を提供することを主目的とする。

【解決手段】本発明は、可撓性を有する金属基材と、上記金属基材の少なくとも一方の表面上に形成された絶縁層と、上記金属基材の他方の表面上に形成され、電磁波剥離性を有する電磁波剥離性粘着樹脂を含む電磁波剥離性粘着層と、を有することを特徴とする電磁波剥離性フレキシブルデバイス用基板を提供することにより、上記目的を達成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層14と、第2の半導体層14の上に形成された第3の半導体層15と、第3の半導体層15の上に形成されたゲート電極21と、第2の半導体層14の上に形成されたソース電極22及びドレイン電極23と、を有し、第3の半導体層15には、半導体材料にp型不純物元素がドープされており、第3の半導体層において、ゲート電極の直下にはp型領域15aが形成されており、p型領域15aを除く領域は、p型領域15aよりも抵抗の高い高抵抗領域15bが形成されている半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】耐圧をより向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体積層構造8と、基板1と化合物半導体積層構造8との間に形成された非晶質性絶縁膜2と、が設けられている。

(もっと読む)

半導体装置

【課題】電子走行層にFeが入り込むことを抑制し、半導体層等にクラックの発生が抑制される電界効果型トランジスタを提供する。

【解決手段】基板11の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層14と、高抵抗層14の上に形成された多層中間層15と、多層中間層15の上に半導体材料により形成された電子走行層16と、電子走行層の上に半導体材料により形成された電子供給層17と、を有し、多層中間層15は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする半導体装置。

(もっと読む)

電子装置およびその製造方法

【課題】開口部を形成されることにより、大きなバンドギャップを有するグラフェンシートを有する電子装置を提供する。

【解決手段】基板と、前記基板上に形成されたグラフェンシート23と、前記グラフェンシートの一端に形成されたソース電極23Sと、前記グラフェンシートの他端に形成されたドレイン電極23Dと、前記グラフェンシート上ゲート絶縁膜を介して形成され、前記グラフェンシートにゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極を結ぶ方向を横切って形成された複数の開口部23Aよりなる開口部列と、を備え、前記複数の開口部はいずれも、三つのジグザグ端により画成されて正三角形の形状を有し、前記ジグザグ端のうち二つは、前記ソース電極とドレイン電極を結んだ方向に対し30°の角度をなし、もう一つのジグザグ端は90°の角度をなし、それぞれの正三角形の向きを揃えて形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲートリーク電流が低減され、かつ、ノーマリーオフ動作する半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層12と、第1の半導体層12の上に形成された第2の半導体層13と、第2の半導体層13の上に形成された下部絶縁膜31と、下部絶縁膜31の上に、p型の導電性を有する酸化物により形成された酸化物膜33と、酸化物膜33の上に形成された上部絶縁膜34と、上部絶縁膜34の上に形成されたゲート電極41と、を有し、ゲート電極41の直下において、下部絶縁膜31の表面には凹部が形成されている半導体装置。

(もっと読む)

CMOS半導体装置の製造方法及びCMOS半導体装置

【課題】マイクロコンタクト印刷の版を凹版として使用し、微細な電気回路と高生産性のCMOS半導体装置の製造方法を提供するものである。

【解決手段】Pチャネル型電界効果トランジスタのPチャネル領域101とNチャネル型電界効果トランジスタのNチャネル領域102とを、凹版601を用いた印刷によって形成するようにし、凹版601が、第1凹部602と第2凹部603とを備え、インクジェット法によって、第1凹部602にP型半導体インク111を供給し、第2凹部603にN型半導体インク112を供給する工程と、インク供給後に、凹版601を被印刷基板001に押しつけて、第1凹部602に供給したP型半導体インク111と第2凹部603に供給したN型半導体インク112とを一括して被印刷基板001に転写する工程と、を含むCMOS半導体装置の製造方法を提供する事により、上記課題を解決する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ドレイン−ソース間のリーク電流が少なく、かつ、ノーマリーオフの半導体装置を提供する。

【解決手段】基板11の上に形成された不純物元素を含む第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層16と、第2の半導体層16の上に形成された第3の半導体層17と、第3の半導体層17の上に形成されたゲート電極21、ソース電極22及びドレイン電極23と、を有し、第2の半導体層16において、ゲート電極21の直下には、第1の半導体層13と接し、第1の半導体層13に含まれる不純物元素が拡散している不純物拡散領域15が形成されており、不純物元素は、不純物拡散領域がp型となる元素であることを特徴とする半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11daと、電子供給層5とゲート電極11gとの間に形成された第1のp型半導体層7aと、ソース電極11sと電子供給層5との間に形成されたp型半導体層7と、が設けられている。第2のp型半導体層7上のソース電極11sには、第1の金属膜11saと、第1の金属膜11saにゲート電極11g側で接し、第1の金属膜11saよりも抵抗が大きい第2の金属膜11sbと、が設けられている。

(もっと読む)

スパッタリングターゲット

【課題】高密度かつ低抵抗のスパッタリングターゲット、電界効果移動度の高い薄膜トランジスタを提供する。

【解決手段】Gaをドープした酸化インジウム、又はAlをドープした酸化インジウムを含み、正4価の原子価を示す金属を、Gaとインジウムの合計又はAlとインジウムの合計に対して100原子ppm超1100原子ppm以下含み、結晶構造が、実質的に酸化インジウムのビックスバイト構造からなる焼結体を含むスパッタリングターゲット。

(もっと読む)

半導体装置、薄膜トランジスタ基板および表示装置

【課題】金属酸化物を用いた絶縁膜を低温プロセスで結晶化することが可能で、これによりガラス基板やプラスチック基板上に特性の向上が図られた素子を設けることが可能な半導体装置を提供する。

【解決手段】基板上に、金属酸化物を用いた絶縁膜と半導体薄膜とが積層形成された半導体装置であって、絶縁膜はゲート絶縁膜として用いられ、ゲート絶縁膜に接する側にゲート電極が積層形成され、絶縁膜および半導体薄膜は結晶化され、かつ、ゲート電極と重なる部分の結晶性が他の部分の結晶性よりも高いものである。

(もっと読む)

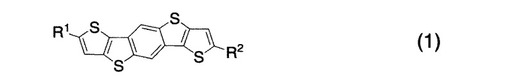

ジチエノベンゾジチオフェン誘導体組成物及びこれを用いた有機薄膜トランジスタ

【課題】溶媒への溶解性に優れ、高キャリア移動度が期待できる新規なジチエノベンゾジチオフェン誘導体組成物及びこれを用いた有機薄膜トランジスタを提供する。

【解決手段】下記一般式(1)で示されるジチエノベンゾジチオフェン誘導体99〜80重量%及び特定式で示されるジチエノベンゾジチオフェン誘導体1〜20重量%からなることを特徴とするジチエノベンゾジチオフェン誘導体組成物。

(ここで、置換基R1及びR2は、同一又は異なって、n−ペンチル基、n−ヘキシル基、n−ヘプチル基及びn−オクチル基からなる群より選択される置換基を示す。)

(もっと読む)

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

表示装置

【課題】低消費電力化できる液晶表示装置を提供することを課題の一とする。

【解決手段】表示部に複数の画素を有し、複数のフレーム期間で表示を行う液晶表示装置であって、フレーム期間は、書き込み期間及び保持期間を有し、書き込み期間において、複数の画素のそれぞれに、画像信号を入力した後、保持期間において、複数の画素が有するトランジスタをオフ状態にして、少なくとも30秒間、画像信号を保持させる。画素は、酸化物半導体層でなる半導体層を具備し、酸化物半導体層は、キャリア濃度が1×1014/cm3未満である。

(もっと読む)

論理回路および半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1

μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号とし

て、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力され

た第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を

出力信号として出力する構成とする。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

有機電界効果型トランジスタ

【課題】カーボンナノチューブを含有する活性層を有する有機電界効果型トランジスタにおいて、熱プロセス、経時変化、外部環境に対して、移動度、Von、ヒステリシスの性能を安定化すること。

【解決手段】ゲート電極、ゲート絶縁層、カーボンナノチューブを含有する活性層、該活性層に対して前記ゲート絶縁層と反対側に形成された架橋構造を持つポリシロキサンを含む第2絶縁層、ソース電極およびドレイン電極を有する有機電界効果型トランジスタ。

(もっと読む)

半導体装置

【課題】電流駆動能力がより小さなクロック信号生成回路を適用することが可能な半導体装置を提供する。

【解決手段】nチャネル型トランジスタで構成されるスイッチ及び論理回路を有し、スイッチは導通状態又は非導通状態がクロック信号によって選択され、論理回路は、ブートストラップ回路と、入力信号が入力される入力端子と、反転入力端子と、出力端子とを有し、高電源線と出力端子との接続を反転入力端子に入力される信号によって制御し、低電源線と出力端子との接続を入力端子に入力される信号によって制御することによって、入力信号がローレベル電位の場合には、ブートストラップ回路を用いて出力端子の電位を上昇させることにより出力端子から高電源電位を出力し、トランジスタは、チャネルが形成される半導体層と、半導体層を挟んで上下に設けられた一対のゲート電極とを有し、一対のゲート電極の他方はソースと接続される。

(もっと読む)

41 - 60 / 2,099

[ Back to top ]