Fターム[5F110CC01]の内容

Fターム[5F110CC01]の下位に属するFターム

順コプレナドープ (4,463)

Fターム[5F110CC01]に分類される特許

61 - 80 / 2,099

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

有機電界効果型トランジスタ

【課題】カーボンナノチューブを含有する活性層を有する有機電界効果型トランジスタにおいて、熱プロセス、経時変化、外部環境に対して、移動度、Von、ヒステリシスの性能を安定化すること。

【解決手段】ゲート電極、ゲート絶縁層、カーボンナノチューブを含有する活性層、該活性層に対して前記ゲート絶縁層と反対側に形成された架橋構造を持つポリシロキサンを含む第2絶縁層、ソース電極およびドレイン電極を有する有機電界効果型トランジスタ。

(もっと読む)

半導体装置

【課題】電流駆動能力がより小さなクロック信号生成回路を適用することが可能な半導体装置を提供する。

【解決手段】nチャネル型トランジスタで構成されるスイッチ及び論理回路を有し、スイッチは導通状態又は非導通状態がクロック信号によって選択され、論理回路は、ブートストラップ回路と、入力信号が入力される入力端子と、反転入力端子と、出力端子とを有し、高電源線と出力端子との接続を反転入力端子に入力される信号によって制御し、低電源線と出力端子との接続を入力端子に入力される信号によって制御することによって、入力信号がローレベル電位の場合には、ブートストラップ回路を用いて出力端子の電位を上昇させることにより出力端子から高電源電位を出力し、トランジスタは、チャネルが形成される半導体層と、半導体層を挟んで上下に設けられた一対のゲート電極とを有し、一対のゲート電極の他方はソースと接続される。

(もっと読む)

半導体装置

【課題】新規な構成を有する半導体装置である。

【解決手段】第1の素子を有し、第2の素子を有し、トランジスタを有し、容量を有し、第1の素子の出力は、第2の素子の入力と電気的に接続され、第2の素子の出力は、第1の素子の入力と電気的に接続され、第1の素子の入力は、入力端子と電気的に接続され、第1の素子の出力は、出力端子と電気的に接続され、トランジスタのソース及びドレインの一方は、容量の一方の電極と電気的に接続され、トランジスタのソース及びドレインの他方は、入力端子と電気的に接続され、トランジスタのチャネル形成領域は、結晶を有する酸化物半導体を有する。結晶を有する酸化物半導体を有するトランジスタはリーク電流が非常に小さいため、データを保持することができる。

(もっと読む)

有機半導体素子用電極及びその製造方法

【課題】電界効果移動度が高い有機半導体素子の製造に有用な有機半導体素子用電極、及び、該有機半導体素子用電極を有する有機半導体素子を安価に提供する。

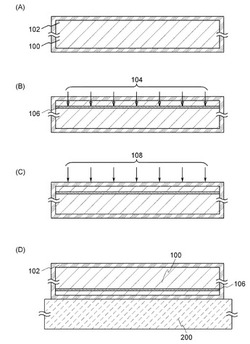

【解決手段】基板1、ゲート電極4、ゲート絶縁膜3、有機半導体層2、ソース電極5及びドレイン電極6を有する有機半導体素子100であって、前記ゲート絶縁膜上に設けられた自己組織化単分子膜のパターン領域と、前記自己組織化単分子膜のパターン領域外である電極形成領域20に設けられたグラフェンナノリボンを含有する薄膜からなる前記ソース電極及びドレイン電極とを有する、有機半導体素子。

(もっと読む)

高分子化合物、該高分子化合物を含む薄膜及び組成物

【課題】両極性の有機トランジスタを簡便に製造しうる、p型とn型の両極性を示す高分子化合物を提供すること。

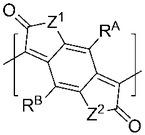

【解決手段】式

【化0】

(1)

〔式中、Z1は、−O−、−S−、−N(R1)−、−N(COR2)−又は−N(CO2R3)−を表す。Z2は、−S−、−N(R1)−、−N(COR2)−又は−N(CO2R3)−を表す。R1、R2及びR3は、それぞれ独立に、水素原子アルキル基、アリール基又はヘテロアリール基を表す。RA及びRBは、それぞれ独立に、水素原子、アルキル基、アルコキシ基、アルキルチオ基、アリール基、ヘテロアリール基、ハロゲン原子又はシアノ基を表す。〕

で表される構成単位を含む高分子化合物。

(もっと読む)

半導体装置

【課題】導電性が高い酸化物半導体層を有する酸化物半導体トランジスタを提供する。

【解決手段】インジウム、ガリウム、亜鉛を含む酸化物(IGZO)及び酸化インジウムの粒子を有する酸化物半導体層と、当該酸化物半導体層中のチャネル形成領域と、ゲート絶縁膜を挟んで重畳するゲート電極と、当該酸化物半導体層中のソース領域及びドレイン領域に重畳するソース電極及びドレイン電極とを有する半導体装置に関する。当該半導体装置は、トップゲート型酸化物半導体トランジスタ又はボトムゲート型酸化物半導体トランジスタであってもよい。また当該酸化物半導体層は、ソース電極及びドレイン電極の上に形成されていてもよいし、ソース電極及びドレイン電極の下に形成されていてもよい。

(もっと読む)

有機半導体素子用電極及びその製造方法

【課題】電界効果移動度が十分な有機半導体素子を安価に製造することができる有機半導体素子用電極、及びかかる有機半導体素子用電極を有する有機半導体素子を提供する。

【解決手段】基板1上に、酸化グラフェンナノリボンを含有するインクをインクジェット法により塗布し、前記インクが含有する前記酸化グラフェンナノリボンを還元して、グラフェンナノリボンを含有する薄膜とすることにより形成される有機半導体素子用電極5、6。

(もっと読む)

高分子化合物及びそれを用いた有機トランジスタ

【課題】電界効果移動度が高い有機トランジスタ作製に有用な高分子化合物を提供する。

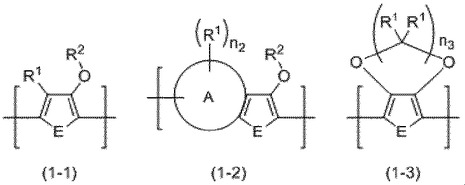

【解決手段】式(1−1)〜式(1−3)で表される構造単位からなる群から選ばれる少なくとも1種の構造単位と、アリーレン基または2価の芳香族複素環基からなる構造単位とを含む高分子化合物とする。

式中、R1は、水素原子、アルキル基、アルコキシ基、アルキルチオ基、アリール基、1価の芳香族複素環基またはハロゲン原子を表す。R2は、炭素数が2以上のアルキル基を表す。Eは、−O−、−S−、−Se−または−N(Ra)−を表す。Raは、水素原子、アルキル基、アリール基または1価の芳香族複素環基を表す。環Aは、芳香環または複素環を表す。n2は0以上の整数を表し、n3は1〜3の整数を表す。]

(もっと読む)

表示装置

【課題】消費電力が抑制された表示装置を提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、及び一対の電極を有する発光素

子を含む画素が複数設けられた画素部を有し、前記第1のトランジスタは、ゲートが走査

線に電気的に接続され、ソースまたはドレインの一方が信号線に電気的に接続され、ソー

スまたはドレインの他方が前記第2のトランジスタのゲートに電気的に接続され、前記第

2のトランジスタは、ソースまたはドレインの一方が電源線に電気的に接続され、ソース

またはドレインの他方が前記一対の電極の一方に電気的に接続され、前記第1のトランジ

スタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有する。そして、

前記表示装置が静止画像を表示する期間の間に、前記画素部に含まれる全ての走査線に供

給される信号の出力が停止される期間を有する。

(もっと読む)

半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出

力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有

するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を

用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極

又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持

することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

π電子共役系化合物前駆体を用いた電子デバイス用インク組成物ならびにその用途

【課題】前駆体膜を変換して得られた半導体膜の導電率の向上。その有機膜を電極と有機半導体の間に配置することで、電極と半導体層の接触抵抗を低減すること。その結果として、接触抵抗が改善された高性能の電気特性を得ることが可能な電子デバイス用インク組成物ならびにそれを用いた電子デバイス、電界効果トランジスタ、およびその製造方法を提供すること。

【解決手段】電子デバイス用インク組成物であって、少なくともπ電子共役系化合物前駆体と、前記π電子共役系化合物のドーパントと、前記π電子共役系化合物前駆体とドーパントを溶解させる溶媒を含有することを特徴とするインク組成物。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて製造することが可能な電界効果トランジスタを提供する。

【解決手段】本発明1つの電界効果トランジスタは、ソース領域144及びドレイン領域146並びにチャネル領域142を含む酸化物導電体層と、チャネル領域142の導通状態を制御するゲート電極120と、ゲート電極120とチャネル領域142との間に形成された強誘電体材料又は常誘電体材料からなるゲート絶縁層130とを備え、チャネル領域142の層厚は、ソース領域144の層厚及びドレイン領域146の層厚よりも薄い。

(もっと読む)

高分子化合物及びそれを用いた有機トランジスタ

【課題】有機トランジスタの活性層に用いた場合に、電界効果移動度が十分に高くなる高分子化合物を提供する。

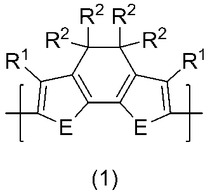

【解決手段】式

〔式中、Eは、−O−、−S−又は−Se−を表す。R1は、水素原子、アルキル基、アルコキシ基、アルキルチオ基、アリール基、ヘテロアリール基又はハロゲン原子を表す。R2は、水素原子、アルキル基、アリール基、ヘテロアリール基又はハロゲン原子を表すか、2個のR2が連結して環を形成する。〕で表される構造単位と、式(1)で表される構造単位とは異なる式−Ar1−で表される構造単位とを含む高分子化合物である(式中、Ar1は、2価の芳香族基、−CR3=CR3−で表される基又は−C≡C−で表される基を表す)。

(もっと読む)

高電子移動度トランジスタとその製造方法

【課題】高電子移動度トランジスタにおいて、ゲート部のドレイン側端部における電界集中を緩和する。

【解決手段】高電子移動度トランジスタ10は、導電体部23と第1抵抗部R1と第2抵抗部R2を備えている。導電体部23は、ドレイン電極21とゲート部26の間に設けられている。第1抵抗部R1は、一端がドレイン電極21に電気的に接続されており、他端が導電体部23に電気的に接続されている。第2抵抗部R2は、一端がソース電極28に電気的に接続されており、他端が導電体部23に電気的に接続されている。

(もっと読む)

半導体装置

【課題】不揮発性を有し、書き込み回数に制限のない新たな構造の半導体装置を提供する。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

チューナブルバリアを備えるグラフェンスイッチング素子

【課題】チューナブルバリアを備えるグラフェンスイッチング素子を提供する。

【解決手段】バックゲート基板と、基板上のゲート絶縁層と、ゲート絶縁層上のグラフェン層と、グラフェン層の第1領域上に順次に積層された半導体層及び第1電極と、グラフェン層で第1領域と離隔している第2領域上の第2電極と、を備え、バックゲート基板とグラフェン層とは、半導体層を介して対向し、半導体層は、n型またはp型にドーピングされたチューナブルバリアを備えるグラフェンスイッチング素子。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】性能および製造安定性を向上させることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、第1の面および第2の面を有する有機半導体部と、第1の面に隣接されたソース電極部と、第2の面に隣接されたドレイン電極部とを備える。ソース電極部およびドレイン電極部のうちの少なくとも一方は、有機半導体部よりも高導電性の有機半導体材料を含む高導電性電極部である。

(もっと読む)

半導体装置

【課題】小面積、低電力動作、高速動作を並立する論理ゲートを含む半導体装置の構成を提供する。

【解決手段】本発明に係る半導体装置は、基板上にゲート絶縁膜を介してゲート電極と半導体層が配置され、半導体層に接続してソース電極とドレイン電極とが配置される薄膜トランジスタを2つ以上含む論理ゲートで構成される。少なくとも第一の薄膜トランジスタは、そのゲート電極が電気的に浮遊状態にあり、かつ、その半導体層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。また、少なくとも第二の薄膜トランジスタは、そのゲート電極が入力端子に接続され、かつ、そのチャネル層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。

(もっと読む)

電子装置

【課題】カーボンによるバンドギャップ・エンジニアリングを可能とし、カーボン原子に基づく多彩なエレクトロニクスを達成して、信頼性の高い電子装置を実現する。

【解決手段】電子装置は、単層のグラフェン膜1と、グラフェン膜1上の両端に設けられた一対の電極2,3とを有しており、グラフェン膜1では、電極2,3間の領域において、中央部位のBC間が複数のアンチドット10が形成されてなる第1の領域1aとされており、第1の領域1aの両側におけるAB間及びCD間がアンチドットの形成されていない第2の領域1bとされている。

(もっと読む)

61 - 80 / 2,099

[ Back to top ]